herramientas de apoyo para la enseñanza de

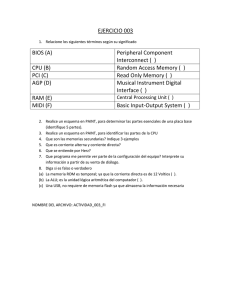

Anuncio