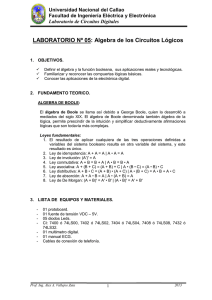

Reducción de Circuitos Lógicos: Álgebra de Boole y Karnaugh

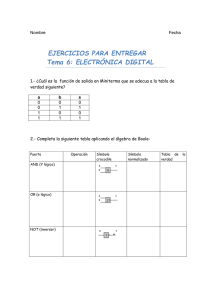

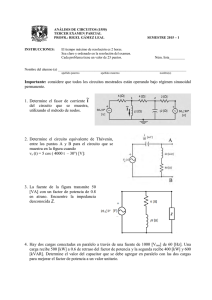

Anuncio

UNIVERSIDAD NACIONAL DE INGENIERÍA FACULTAD DE INGENIERÍA MECÁNICA ESCUELA DE INGENIERÍA MECATRÓNICA CURSO: Análisis y diseño de circuitos digitales Laboratorio 2 SECCIÓN: “A”. TEMA: Reducción de circuitos lógicos mediante el álgebra de Boole. INTEGRANTES: Giraldo Castillo Oscar O. Valentín Soria Arturo B. Carrasco Mendoza Martin. PROFESOR: Julien Noel. 2010 II LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 1 OBJETIVO Proporcionar al alumno los modelos de reducción de funciones empleando el álgebra de Boole y mapa de Karnaugh, aplicado a circuitos digitales. EQUIPOS Y MATERIALES Osciloscopio, multímetro, cables de conexión, modulo digital, protoboard, kit de componentes TTL. Experiencia 1: 1. Implemente el circuito en el módulo digital y complete la tabla de verdad. X 0 0 0 0 1 1 1 1 Y 0 0 1 1 0 0 1 1 Z 0 1 0 1 0 1 0 1 F 0 1 0 1 0 0 0 1 2. Simplifique la función mediante el álgebra de Boole, luego impleméntelo con compuertas lógicas. Simplificando la expresión: ̅ (̅ ) ̅ (̅ (̅ ) ) LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 2 Experiencia 2: 1. Repetir los pasos anteriores para el circuito K. X 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Y 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Z 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 W 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 F 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 0 2. Simplifique la función mediante el álgebra de Boole, luego impleméntelo con compuertas lógicas. Simplificando la expresión: ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ̅̅̅̅̅̅ ( ̅̅̅̅̅̅̅̅̅̅̅̅̅̅̅ ( ) (̅̅̅̅̅̅̅)( ) (̅̅̅̅ ̅̅̅̅̅̅̅̅̅ ) ̅ )( ̅ ̅ ̅) ̅ ̅ ̅ ̅ )( ̅ ̅̅ ̅ ̅ ̅̅ ̅ ̅ ̅( ̅ ̅) ̅ ̅ ̅ 𝑋 𝑋 𝑌 ̅ ̅ 𝑌̅ ̅ ̅ ̅ ̅ ̅ ̅ LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 3 Experiencia 3: 1. Repetir los pasos anteriores para el circuito L. A B C D 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 F 0 0 1 1 0 0 1 1 1 1 1 1 1 1 0 0 2. Simplifique la función mediante el mapa de Karnaugh, luego impleméntelo con compuertas lógicas. ⁄ 00 01 11 10 00 0 0 1 1 01 0 0 1 1 11 1 1 0 1 10 1 1 0 1 Expresión simplificada: ̅ ̅ ̅ ̅ LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 4 Ejercicio Cuatro tanques (A, B, C, D) de una planta química contienen diferentes líquidos sometidos a calentamiento. Se usan sensores de nivel de líquido para detectar si el nivel de líquido de los tanques A y B excede un nivel predeterminado. Los sensores de temperatura de los tanques C y D detectan cuando la temperatura desciende por debajo del límite previsto. Suponga que las salidas A y B del sensor de nivel de líquido son BAJOS cuando el nivel es satisfactorio y ALTOS cuando es demasiado alto. Asimismo las salidas C y D del sensor de temperatura son BAJAS cuando la temperatura es satisfactoria y ALTAS cuando la temperatura es demasiado baja. Diseñe un circuito lógico que detecte cuando el nivel del tanque A o B es demasiado alto al mismo tiempo que la temperatura de los tanques C o D es demasiado baja. A0 B0 C0 D0 Dónde: Sensor de Nivel. Sensor de Temperatura. Consideramos a todos los sensores como contactos normalmente abiertos. ( ) Nivel del tanque A o B es demasiado alto: La temperatura de los tanques C o D es demasiado baja: ( )( ) Mostramos a continuación el circuito: LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 5 A B C D 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 F 0 0 0 0 0 1 1 1 0 1 1 1 0 1 1 1 LABORATORIO DE ANÁLISIS Y DISEÑO DE CIRCUITOS DIGITALES 6