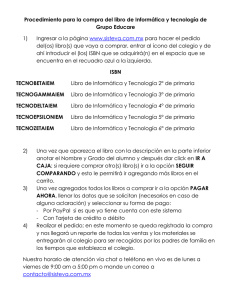

Javier García Zubía Ejercicios básicos de sistemas digitales 4.ª edición Ā A Universidad de Deusto • • • • • • • • Ejercicios básicos de sistemas digitales Javier García Zubía Ejercicios básicos de sistemas digitales 4ª edición 2008 Universidad de Deusto Bilbao Ninguna parte de esta publicación, incluido el diseño de la cubierta, puede ser reproducida, almacenada o transmitida en manera alguna o por ningún medio, ya sea eléctrico, químico, mecánico, óptico, de grabación o de fotocopia, sin permiso previo del editor. Publicación impresa en papel ecológico Compuesto según diseño de JosuKa Díaz Labrador ¤ Publicaciones de la Universidad de Deusto Apartado 1 - 48080 Bilbao e-mail: [email protected] ISBN: 978-84-9830- 784- 9 Índice 1. Códigos binarios .............................................................................. 2. Manipulación básica booleana ....................................................... 3. Diagramas de Veitch-Karnaugh .................................................... 4. Sistemas combinacionales a nivel de bit o de puerta lógica....... 5. Sistemas combinacionales a nivel de palabra o MSI ................... 6. Biestables........................................................................................... 7. Registros y Contadores ................................................................... 8. Autómatas......................................................................................... 1 15 31 47 95 131 147 161 V © Universidad de Deusto - ISBN 978-84-9830-784-9 © Universidad de Deusto - ISBN 978-84-9830-784-9 Prólogo Uno de los principales cometidos de un profesor es facilitar el trabajo al alumno en la medida de lo posible, por ejemplo mediante este libro. Quede dicho esto en primer lugar para no llamar a nadie a engaño: éste no es un libro clásico de teoría, ni tampoco lo es de ejercicios resueltos. La enseñanza en clase de toda asignatura técnica tiene dos aspectos esenciales: la teoría y los ejercicios. Como el tiempo asignado a las clases es limitado, éste se dedica principalmente a la teoría; así en el tiempo restante, a veces escaso, el profesor plantea y resuelve ejercicios. Estos ejercicios de clase son completados con otros que el alumno deberá resolver fuera del horario de clase con el fin de asentar los conocimientos y habilidades adquiridas. Este libro tiene por objetivo facilitar la labor del alumno fuera de clase. Para ello no sólo se entregan los enunciados, sino que también se acompañan de las tablas y diagramas que ayuden en su resolución. De este modo el libro parece un crucigrama a completar por el alumno, con sus casillas inicialmente vacías. El libro facilita el desarrollo del curso y la comunicación entre el profesor y la clase. Ayuda al alumno a preguntar sus dudas y al profesor a detectar las lagunas en lo enseñado. Los ejercicios que aquí se presentan son de procedencia muy variada. La mayoría son originales, otros son los ejercicios típicos, además de los que ya han caído en examen (que tanto gustan a los alumnos), y de algunos han sido enunciados por los propios alumnos. Por último quiero agradecer a mis compañeros de curso Jose Antonio Aranguren y Alfonso Barba sus siempre acertados comentarios, ya que sin ellos este libro no sería tan completo Bilbao, julio de 2000 VII © Universidad de Deusto - ISBN 978-84-9830-784-9 . Prólogo a la 2ª edición Cualquiera que conozca la primera edición de este libro verá que ésta es en principio idéntica, pero ha cambiado algo. En primer lugar, he añadido a cada capítulo una breve introducción teórica. En estas 2 ó 3 páginas intento recordar al lector no tanto las bases teóricas de los ejercicios siguientes, sino sobre todo los métodos que debe aplicar para resolverlos. Algunos pensarán que esta introducción es demasiado breve, pero no quisiera desvirtuar el enfoque original del libro. A aquel que quiera profundizar en los aspectos teóricos le remito al libro “Sistemas Digitales” cuyos autores somos José Mª Angulo Usategui y yo mismo, y fue editado por Paraninfo en el año 2001. En segundo lugar, el lector podrá ver que han desaparecido algunos de los temas que se trataban en el anterior libro. Esto ha sido así para dejar sitio a nuevos ejercicios, y sobre todo para eliminar del libro enfoques y técnicas ya superadas. Un ejemplo de esto último es que en el libro ya no hay ejercicios de contadores asíncronos, pues éstos van (o deben) desaparecer de un curso reglado de electrónica digital. Por último, en el libro hay muchos ejercicios nuevos, sobre todo en los últimos capítulos, que son los más prácticos (los primeros simplemente fortalecen la metodología del alumno). Sólo cuando el lector se proponga resolver los ejercicios verá las nuevas incorporaciones. Éstas sobre todo se centran en los ejercicios combinacionales y secuenciales MSI o funcionales, es decir, aquellos que usan bloques como multiplexores, comparadores, contadores, etc. Estos nuevos ejercicios vienen a completar el hueco que tenía el primer libro, a cambio han desnudado un poco el libro, perdiendo el libro en estos temas su aspecto de crucigrama. Cabe decir que la complicación de estos nuevos ejercicios es baja. Primero porque el nivel del curso sigue siendo el básico, y segundo porque este tipo de sistemas está siendo implementado con dispositivos PLD más que con puertas lógicas, utilizando lenguajes de descripción hardware como ABEL, VHDL, etc.; técnicas y métodos que quedan totalmente fuera de este libro. Sólo me queda esperar que este libro siga siendo útil a aquellos profesores y alumnos que lo utilizan. VIII © Universidad de Deusto - ISBN 978-84-9830-784-9 Prólogo a la 3ª edición En esta tercera edición poco cabe decir que no se sepa ya. Cada dos años sale una nueva edición. En ésta se añaden nuevos ejercicios, desaparecen otros y se corrigen los fallos. En resumen, una nueva edición aumentada y corregida. El objetivo del libro se mantiene: ayudar en el seguimiento del curso en el aula con ejercicios que refuercen o introduzcan lo aprendido. Desde este punto de vista, son los alumnos los que dan valor al libro. Los alumnos o profesores más interesados cuentan con una edición de estos ejercicios resueltos. La editorial Paraninfo ha publicado en el 2003 el libro “Problemas Resueltos de Electrónica Digital”. Por último, y como siempre, quiero agradecer a mis compañeros de asignatura sus aportaciones y recomendaciones para este libro, especialmente a Alfonso Barba por todos estos años juntos en la electrónica digital. Sigo contando con José Antonio Aranguren, Iván Trueba e Ignacio Angulo. Como siempre, estaré encantado de recibir comentarios o nuevos ejercicios a mi dirección de correo [email protected]. IX © Universidad de Deusto - ISBN 978-84-9830-784-9 Prólogo a la 4ª edición En esta cuarta edición los cambios han consistido en añadir nuevos ejercicios de examen (más de 50) y en borrar otros ya “antiguos”. En cuanto a los cambios hay algunos destacables: desaparecen los ejercicios NAND/NOR, ya que su utilidad actual no está muy clara en este nivel; aparecen ejercicios de análisis en sistemas combinacionales funcionales; y el tema de biestables se ha reducido de una forma considerable, evitando disquisiciones teóricas. Otro cambio importante ha sido eliminar la implementación de autómatas con circuitos digitales (J-K, D, etc.), es decir, en la nueva edición solo se plantea el DTE, ya que el esfuerzo de implementación no se corresponde con su interés. La última novedad consiste en que se ha añadido a algunos capítulos cómo usar el programa BOOLE-DEUSTO (http://paginaspersonales.deusto.es/zubia) para resolver los ejercicios. El BOOLE-DEUSTO es un entorno informático con difusión internacional y gran aceptación universitaria, ya que es tan potente como sencillo, siendo gratuito. Los alumnos o profesores más interesados cuentan con una edición de algunos de estos ejercicios resueltos. La editorial Paraninfo ha publicado en el 2003 el libro “Problemas Resueltos de Electrónica Digital”. Por último, y como siempre, quiero agradecer a mi compañero Ignacio Angulo sus aportaciones a este libro; y también a los alumnos, que con sus comentarios tanto mejoran el libro. Como siempre, estaré encantado de recibir comentarios o nuevos ejercicios a mi dirección de correo [email protected]. X © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios Introducción metodológica Resolver ejercicios de códigos es muy fácil, tanto que algunos prefieren liarse. En este tema se exige al alumno que sepa representar información binaria y operar con ella. La información común de nuestro mundo diario es alfanumérica, pero en el reducido campo de nuestra asignatura solo representaremos números, así que todo es más fácil. Volviendo a nuestro mundo, sabemos que estos números los representamos siempre en decimal, en el único código decimal que utilizamos. Este código por ser único no tiene ni nombre (sí lo tiene), es simplemente el decimal. Vayamos ahora al mundo digital, en él los números se representan en binario, pero frente al mundo real no existe un único código binario, existen muchos. La razón de que existan muchos códigos binarios es porque ninguno de ellos es lo suficientemente bueno para eliminar a los otros. Cada código binario está especializado en un campo, aunque hay un par de códigos binarios que están por todas partes: el código binario puro y el BCD puro. En este momento tenemos un código decimal y muchos binarios. Llamamos escribir a pasar de decimal a binario, y leer a pasar de binario a decimal. Esta descripción muestra un claro favoritismo a nuestro mundo; mejor sería decir que pasamos de un código a otro, o dicho más adecuadamente, que transcodificamos. Una vez que sepamos representar información binaria, debemos saber operar con ella. Como nuestro curso es básico, aprenderemos las operaciones básicas binarias, que son las lógicas y las aritméticas, siendo estas últimas las que más se practican en los siguientes ejercicios, donde sumaremos, restaremos y complementaremos. Resumiendo, debemos saber pasar del código decimal a cualquiera de los binarios, y viceversa, y sumar, restar y complementar en cualquier código binario. Empecemos por saber leer y escribir, y luego por sumar, restar y complementar. 1 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Transcodificación binario-decimal Antes de escribir o leer hay que saber de qué tipo de número estamos hablando: sin signo o con signo. Seguidamente hay que saber qué código estamos usando. De momento hay que distinguir entre códigos de palabra o de dígito. La diferencia metodológica estriba en que para usar el primer código hay que saberse una regla, y para usar el segundo hay que saberse una tabla. Pero ya estamos hablando de métodos, es momento de describirlos. Paso de decimal a código binario de palabra Dada una secuencia decimal, se le aplica con rigor la regla del código binario elegido, que puede ser, básicamente, uno de tres: binario puro, Gray y exceso. De decimal sin signo a binario puro sin signo Se divide sucesivamente el número decimal entre dos hasta que el cociente es 1 ó 0. En este momento el equivalente binario se obtiene leyendo el último cóciente y los restos de abajo arriba. Por ejemplo: 19 en decimal se escribe 10011 en binario puro 19/2=9 Resto=1 9/2=4 Resto=1 4/2=2 Resto=0 2/2=1 Resto=0 En realidad con poco tiempo de práctica nadie aplica este método, todos lo hacemos a ojo y con acierto. Al fin y al cabo tenemos que acabar escribiendo magnitudes en binario como en decimal; nuestro mundo también va a ser el digital binario. De binario puro sin signo a decimal sin signo Se obtiene el sumatorio de los bits ponderados con las correspondientes potencias de 2. Por ejemplo: 10011 en binario puro es 19 en decimal 10011= 1x24 + 0x23 + 0x22 + 1x21 + 1x20 = 16+0+0+2+1 Pero igual que en el caso anterior, nadie aplica esta regla tan larga como exacta, una vez que tengamos confianza leeremos directamente del binario. Al fin y al cabo, nuestro mundo es binario y no deberíamos pasar al decimal. 2 © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios De decimal con signo a binario puro con signo en complemento a 1 o en complemento a 2. La regla de escritura es muy sencilla como muestra la siguiente tabla. Binario puro con C-1 positivos: binario puro y añadir 0 negativos: C-1 del positivo decimal +13 -13 +1 -1 0 Binario puro con C-2 positivos: binario puro y añadir 0 negativos: C-2 del positivo binario puro binario puro con C-1 1101 01101 10010 1 01 10 0 00 binario puro con C-2 01101 10011 01 11 00 Paso de decimal a código binario BCD Si los anteriores códigos se basaban en una regla, éstos se basan en una tabla. El método consiste en sustituir cada dígito decimal por los cuatro bits correspondientes. A continuación se ofrece una tabla con alguno de los códigos BCD, con los más comunes. decimal 0 1 2 3 4 5 6 7 8 9 BCD puro 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 BCD XS3 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 Aiken 0000 0001 0010 0011 0100 1011 1100 1101 1110 1111 BCD 5421 0000 0001 0010 0011 0100 1000 1001 1010 1011 1100 Algunos alumnos tienen tendencia a buscar y aprender la regla que subyace en esta tabla, pero no siendo esto malo debe recordarse que la que manda es la tabla, no la regla intuida. Para pasar de un código BCD a decimal habrá que aplicar la tabla inversa a cada grupo de cuatro bits. Parece sencillo aunque tiene alguna particularidad. 3 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Operaciones con información binaria Básicamente hablamos de operaciones lógicas: AND, OR, NOT, etc. y aritméticas: suma, resta y complemento. Las primeras serán vistas en el siguiente capítulo, pasemos a las aritméticas. Una vez más todo pasa por aplicar el método rigurosamente, y habrá tantos como códigos binarios utilicemos. Suma en binario puro sin signo Este es la suma básica, y es tan sencilla como sumar en decimal. La tabla de la suma es: 0 + 0= 0 y me llevo 0 (S=0 y C=0) 0 + 1= 1 y me llevo 0 (S=1 y C=0) 1 + 0 = 1 y me llevo 0 (S=1 y C=0) 1 + 1 = 1 y me llevo 1 (S=0 y C=1) Suma en binario puro con signo en complemento a 2 1. Sumar las secuencias binarias según la regla del binario puro. 2. Despreciar el acarreo final. 3. Habrá desborde si los dos últimos acarreos son distintos. Complemento a 2 de una secuencia binaria 1. Complementar a 1. 2. Sumar 1, despreciando el acarreo final si se produce. Resta en binario puro con signo en complemento a 2 1. Complementar a 2 el sustraendo. 2. Sumar el minuendo y el sustraendo negado según la regla del C-2. Como consejos finales: • Identifica bien cuál es el código de partida y cuál es el de llegada. • Identifica si el número a leer o escribir tiene signo o no. • Ten presente (a la vista) la regla o tabla que vas a aplicar. • Aplica el método o tabla radicalmente. • Recuerda que un código es algo arbitrario y no necesita de tu inteligencia. • Comprueba el resultado en la medida de lo posible: si has pasado de A a B, siempre podrás darle la vuelta y ver si obtienes de nuevo A. 4 © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios Ejercicios 1.1 Pasa de decimal a binario, y viceversa. Binario Decimal Decimal 01 1 1101 7 1100 9 1111 12 0011 34 0101 32 1010 33 0000 01 000000 00001 110011 100 10101 205 0100011 63 01111000 64 0110011 4 000000011 56 11011 62 011 1023 100000001 0000 00110 015 Binario 5 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 1.2 Convierte entre sí los siguientes números hexadecimales y binarios. Hexadecimal Binario 12A 3C0 4 FF D1A 11 00100110 010100001 11001101100 10000 1000 01001 6 © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios 1.3 Pasa de decimal a BCD puro, y viceversa. DEC. BCD puro 4 32 63 0 1 00 36 12 04 100 00110010000 01100011 00000000 01000010 10000111 000100000000 0010 000010011001 00111100 7 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 1.4 Anota para cada número de bits, el rango de valores asociado a cada código. Anota fuera de la tabla las expresiones generales para cada código. Núm. bits BP sin signo BP con C-2 1 2 3 4 5 6 7 8 9 10 BP sin signo Rango Goles en un partido Peso de una persona 10 notas de un alumno Temperatura en una casa Temperatura en la calle Altura sobre el nivel del mar Años de vida Dinero en una cuenta Diferencia horaria Altura de una marea 8 © Universidad de Deusto - ISBN 978-84-9830-784-9 Núm. bits 1. Códigos binarios 1.5 Anota para cada secuencia binaria la secuencia decimal que le corresponde, según sea el código en el que se lea dicha secuencia binaria. Secuen. Binaria Según BP sin Según BP con signo signo en C-2 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 9 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 1.6 Codifica las siguientes magnitudes decimales con signo en el código binario puro con signo en C-2. Selecciona cuidadosamente el número de bits para codificar cada número. Decimal Binario con C-2 +15 +36 +8 +1 +0 -10 -4 -9 +17 -17 -001 -106 -64 -63 +36 -44 -0 -99 -1585 +1260 10 © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios 1.7 Obtén el número decimal con signo correspondiente a cada secuencia binaria codificada en binario puro con signo en C-2. Decimal leído Binario según BP con C-2 100 00111 10100 11000 10011101 1100 011111 10000 11111 01111 1111 10010100 11111111 1011001 0000001 11 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 1.8 Completa las siguientes sumas binarias, indicando en cada caso si ha habido o no desborde. Comprueba los datos anotando a la izquierda los resultados decimales. Dec. Binario Puro Dec. Binario Puro 1100 01 00110 + 110 101000 + 000001 11000 + 10011 11001 + 1111001010 010 + 00010 1001001010 +1000010011 0100001 +0111101 111111111 + 1 11011010 + 1110000101 + 12 © Universidad de Deusto - ISBN 978-84-9830-784-9 1. Códigos binarios 1.9 Completa las siguientes sumas binarias en BP con signo en C-2, indicando en cada caso si ha habido o no desborde. Y viceversa. Dec. Binario con signo en C-2 00101 + 11100 11010 + 00011 0001101 + 1101000 1111001 + 0110000 0011 + 1100 Decimal Binario con C-2 (5) + (-3) (-5) + (3) (00) + (-12) (-12) + (-20) (-37) + (37) 13 © Universidad de Deusto - ISBN 978-84-9830-784-9 © Universidad de Deusto - ISBN 978-84-9830-784-9 2. Manipulación básica booleana Introducción metodológica En este capítulo practicarás con las bases del álgebra de Boole y sus representaciones. Si en el anterior capítulo hemos presentado unos métodos que han de ser aplicados con rigidez, qué decir de este capítulo en el que practicaremos con un álgebra, la de Boole. En esta introducción no daremos muchos ejemplos porque la alargarían innecesariamente. Operadores básicos y no básicos booleanos Recordemos los operadores lógicos o booleanos. A B A+B A⋅B A A+B A⋅B A⊕B 0 0 1 1 0 1 0 1 0 1 1 1 0 0 0 1 1 1 0 0 1 0 0 0 1 1 1 0 0 1 1 0 Obtener la tabla de verdad de cualquier expresión booleana Simplemente habrá que sustituir las variables por las combinaciones de 0 y 1 y operar según la anterior tabla. El proceso es lento pero infalible. No merece la pena correr. Por ejemplo, para obtener la tabla de verdad de f= B ⋅(A+C⋅ (A+B) ) habría que plantear una tabla con 8 filas, de 000 a 111. Para cada una de las filas habría que proceder como para 000: f(000) = 0 ⋅(0+0⋅ (0+0) ) = 1⋅(0+0⋅ (1)) =1⋅0 = 0 Lo rápido que cada uno quiera ir es una cuestión libre, pero sólo habrá un resultado correcto, un solo resultado lógico. 15 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Demostración de un teorema booleano por inducción perfecta Al menos tenemos dos caminos para demostrar un teorema: el clásico método algebraico y el particular de la inducción perfecta. Este último camino dice que si se comprueba la veracidad de un teorema para todos las posibles combinaciones de entrada, entonces el teorema lo es en conjunto. O sea, que si se cumple para cada caso, se cumple en general. Este camino se puede usar en álgebra de Boole porque las variables tienen sólo dos valores posibles: 0 y 1, mientras que en nuestra álgebra no, porque cada variable puede tomar infinitos valores. Obtener la forma normal de una tabla de verdad 1. Forma normal disyuntiva: sumar los minitérminos con un 1 en f. 2. Forma normal conjuntiva: multiplicar los maxitérminos con un 0 en f Obtener la tabla de verdad de un circuito lógico La operación es tan lenta como sencilla: asignar a las variables los 0 y 1 de una fila de la tabla de verdad, y seguir el efecto de estos bits a través de las puertas hasta llegar a la salida. Por ejemplo, la siguiente figura muestra la obtención de la salida del circuito para la entrada 000 0 0 0 Ai Bi Ci-1 0 0 0 0 0 0 Ci 0 0 0 0 Si 0 0 0 Si(000) = 0 y Ci(000) = 0 Visto cómo obtener una fila de la tabla, las demás son tan fáciles como lentas de obtener. 16 © Universidad de Deusto - ISBN 978-84-9830-784-9 2. Manipulación básica booleana Negar una expresión booleana Para negar una expresión booleana cualquiera basta con aplicar el teorema de Demorgan recursivamente: 1. La negación de una suma es el producto de las variables negadas. 2. La negación de un producto es la suma de las variables negadas. Implementación de una expresión booleana Basta con sustituir cada operador lógico algebraico por su operador lógico gráfico: cambiar símbolos por gráficos. Implementación de una suma de productos (SOP) Aparecen dos niveles: el primero con tantas AND como productos parciales y el segundo con una sola OR para la suma global. Implementación de un producto de sumas (POS) Aparecen dos niveles: el primero con tantas OR como sumas parciales y el segundo con una sola AND para el producto global. Implementación de funciones sólo con NAND o con NOR Cualquier expresión booleana puede ser implementada solo con NAND o con NOR. 17 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales USO DE BOOLE-DEUSTO Dentro de este capítulo el uso de BOOLE puede ayudar mucho. En casi la totalidad de los ejercicios se puede usar esta calculadora booleana. Describiremos brevemente el uso de BOOLE. Funciones booleanas Una vez arrancado BOOLE y elegido Sistema Combinacional, daremos un nombre al sistema e indicaremos su número de variables de entrada y salida y su nombre. Seguidamente activaremos la opción Expresión Booleana, apareciendo la imagen de la figura 2.1. En ella escribiremos cualquier expresión booleana con OR, AND, NOT y XOR (ver Ayuda). Al pulsar evaluar la función será procesada, finalmente activamos Salir. Figura 2.1 Carga de expresión booleana Una vez procesada la función podemos ver su tabla de verdad activando en la pantalla principal la opción Tabla de Verdad Manual. La figura 2.2 muestra el resultado. Figura 2.2 Tabla de Verdad 18 © Universidad de Deusto - ISBN 978-84-9830-784-9 2. Manipulación básica booleana Tabla de Verdad Para cargar una tabla de verdad hay que activar la opción Tabla de Verdad Manual en la pantalla principal. Al hacerlo, nos aparecerá la imagen de la figura 2.3, en ella, y con simples clic de ratón, iremos cargando los valores de cada fila de la tabla. Por ejemplo, podemos escribir sólo los 1 de la tabla y activar la opción de rellenar, con 0 ó X, para completar el resto de la tabla, lo que resulta bastante cómodo. Lo que no se puede es dejar filas sin completar. Figura 2.3 Carga de una tabla de verdad Pulsamos Evaluar y luego Salir y la tabla queda cargada. A partir de ahora podemos usarla. Por ejemplo, para ver sus expresiones canónicas o formas normales basta con activar la correspondiente opción, resultando la imagen de la figura 2.4. 19 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Figura 2.4 Forma normal disyuntiva Circuito Lógico Para obtener el circuito lógico de una expresión booleana SOP, POS, NAND o NOR basta con activar la opción Visualizador de Circuitos. En ella (ver figura 2.5) podemos escribir en la parte inferior izquierda la expresión booleana que queramos, siempre que ésta sea SOP, POS, NAND o NOR (ver Ayuda), es decir, no obtiene el circuito lógico de cualquier expresión. Figura 2.5 Visualizador de Circuitos 20 © Universidad de Deusto - ISBN 978-84-9830-784-9 2. Manipulación básica booleana Ejercicios 2.1 Obtén en la tabla de verdad la columna resultado de cada una de las siguientes funciones. f1 = A⋅B⋅C f2 = A+B+C f3 = A⋅(B+ C ) f4 = (A+B)⋅(B+C) f5 = B ⋅(A+C⋅ (A+B) ) f6 = (A+C)⋅ (B⋅(C+B)) f7 = (A+B)⋅( A + B ) f8 = A+B⋅(A+C⋅B(A+B)) ABC f1 f2 f3 f4 f5 f6 f7 f8 000 001 010 011 100 101 110 111 21 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 2.2 Demuestra los teoremas principales utilizando el método de inducción perfecta. Es decir, completa las correspondientes columnas de la tabla de verdad y comprueba que son idénticas. Teoremas de una variable Elem. Identidad X 0+X X 1⋅X El. Complementario X X+ X 1 X⋅ X 0 0 1 Prop. Idempotencia X X+X X X⋅X X Elemento Nulo X+1 1 X⋅0 0 0 1 Teoremas de dos variables Teorema de Absorción X Y X+X⋅Y X X⋅(X+Y) X Teorema de Demorgan X+Y ( X ⋅ Y ) X⋅Y ( X + Y ) 00 01 10 11 22 © Universidad de Deusto - ISBN 978-84-9830-784-9 2. Manipulación básica booleana Teoremas de tres variables Propiedad Distributiva X Y Z X⋅(Y+Z) X⋅Y+X⋅Z X+(Y⋅Z) (X+Y)⋅(X+Z) 000 001 010 011 100 101 110 111 Teorema de Demorgan Extendido X Y Z (X+Y+Z) X Y Z (XYZ) X + Y + Z 000 001 010 011 100 101 110 111 23 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 2.3 Pon al lado de cada igualdad Verdadero (V) o Falso (F). x+1 = x·1 x+ x = x+1 (x+y) = x + y x+x = x·x (x·y) = x · y x+(x·y) = x·(x+y) (x· (y·z) ) = ( (x·y) ·z) (x+ (y+z) ) = ( (x+y) +z) 24 © Universidad de Deusto - ISBN 978-84-9830-784-9 0+x = 1·x x· x = x·0 2. Manipulación básica booleana 2.4 Analiza los siguientes circuitos obteniendo las correspondientes tablas de verdad. Ai Bi Ci-1 Ci Si X/Ai Y/Bi Z/Ci-1 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 f1 f2 Si Ci 25 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 2.5 Analiza el siguiente circuito obteniendo su tabla de verdad. B3 B2 B1 B0 X3 B3 B2 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 X1 X2 X3 X2 X1 26 © Universidad de Deusto - ISBN 978-84-9830-784-9 X0 X0 2. Manipulación básica booleana 2.6 Analiza el siguiente circuito obteniendo su tabla de verdad. E7 S2 E6 S1 E4 E3 E2 S0 E1 E0 E7 E6 E5 E4 E3 E2 E1 E0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 1 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 S2 S1 S0 27 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 2.7 Analiza el siguiente circuito obteniendo su tabla de verdad. A2 A1 A0 EI S0 S1 S2 S3 S4 S5 S6 EI A2 A1 A0 S7 S6 S5 S4 S3 S2 S1 S0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 28 © Universidad de Deusto - ISBN 978-84-9830-784-9 S7 2. Manipulación básica booleana 2.8 Analiza el siguiente circuito obteniendo su tabla de verdad. D0 D1 D2 D3 BPI1 D4 D5 D6 D6 D5 D4 D3 D2 D1 D0 BPI1 0 0 0 0 0 0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 1 1 1 0 0 0 0 0 0 0 1 1 1 0 1 1 0 1 0 0 0 0 0 0 0 1 1 1 1 1 0 0 0 1 1 1 1 1 1 1 0 1 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 29 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 2.9 Dibuja los circuitos lógicos digitales correspondientes a las siguientes funciones. f1 = A·B f2 = A+B f3 = A f4 = B f5 = A· B + A ·C f6 = (A+C) · ( A + B ) f7 = C + A ·B f8 = 1 f9 = 0 A B C A B C 30 © Universidad de Deusto - ISBN 978-84-9830-784-9 3. Diagramas de VeitchKarnaugh Introducción metodológica Este capítulo está dedicado a los diagramas de Veitch-Karnaugh, a cómo escribirlos y a cómo leerlos (simplificarlos). La razón porque la que estos diagramas tienen un capítulo para sí es que se utilizan mucho a lo largo de la asignatura, y que si bien es muy fácil escribirlos, no lo es tanto simplificarlos. Escritura u obtención de un V-K a partir de la tabla de verdad Partiendo de una tabla de verdad para obtener el V-K: 1. Dibujar el V-K y asignar las variables con cuidado. 2. Recordar qué casilla se relaciona con cada fila de la tabla. 3. Escribir sólo los 1 y las X de la tabla verdad en el V-K. La relación entre casillas y filas es fija. Para 3 y 4 variables: B A C A 0 4 5 1 2 6 7 3 C 0 8 10 2 B 4 12 14 6 D 5 13 15 7 1 9 11 3 Simplificación o lectura de un V-K Si escribir un V-K es algo directo, simplificarlo no lo es tanto. Simplificar es una habilidad; es un método heurístico, es decir, hay simplificaciones fáciles y difíciles, y la experiencia del alumno es importante. Antes de dar las pautas de simplificación recordemos que simplificar es rodear todos los 1 con el menor número de lazos, siendo éstos del mayor tamaño posible. A veces es importante aplicar esta definición para quitarnos las dudas que pueden aparecer por espejismos estéticos. Para simplificar un V-K podemos seguir el método canónico o el intuitivo. 31 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Método canónico Método intuitivo Formar los lazos de 1 que no Formar el lazo o lazos más puedan ser de 2 grande. Formar los lazos de 2 que no Formar el siguiente lazo más puedan ser de 4 grande. Seguir así hasta rodear todos los Seguir así hasta rodear todos los 1. 1. El mejor método es el canónico, pero el que mejor se acomoda a nuestra forma de hacer las cosas es el intuitivo. En las simplificaciones fáciles aplicaremos la intuición, y en las difíciles el canónico y la definición general. Para aprender a simplificar basta con practicar. Antes de empezar, ahí van unos pocos consejos: • se puede simplificar mucho o poco, pero nunca mal, • no importa que los lazos se crucen entre sí (es lo que se busca), • una casilla puede pertenecer a varios lazos (es lo que se busca), • desterrar ciertos gustos estéticos a la hora de simplificar, • resolver las situaciones incómodas con algo de ingenio, • la función simplificada no tiene por qué ser única, • nunca formar un lazo con sólo X, • los lazos han de ser de 1, 2, 4, 8.... casillas, • un V-K es un cilindro doble: arriba-abajo, dcha-izqda y • los lazos han de ser cuadrados, tiras, etc. 32 © Universidad de Deusto - ISBN 978-84-9830-784-9 3. Diagramas de Veitch-Karnaugh USO DE BOOLE-DEUSTO El uso de BOOLE en este capítulo ha de ser intensivo. El lector encontrará en él una gran ayuda. Esta parte del BOOLE es una de las más apreciadas por cuantos alumnos y profesores ya usan BOOLE. BOOLE no sólo obtiene la expresión simplificada, sino que además pinta los lazos e indica el nombre de cada uno de ellos. Además tiene una opción en la que el lector frente a un V-K introduce su solución. indicándole el BOOLE lo acertado de ésta. El uso de BOOLE en este capítulo da sentido al nombre de calculadora booleana que damos el programa. Diagramas de Veitch-Karnaugh Al activar la opción Diagrama V-K (tipo 1 o 2) el usuario puede cargar el V-K mediante simples clic de ratón. Además puede ayudarse en la opción de completar el V-K. Lo que nunca podrá es dejar el V-K incompleto. Al finalizar la carga hay que activar Evaluar y Salir. Además de la anterior carga directa del V-K, el usuario puede obtener el V-K de la función en curso, que él habrá cargado como sea: tabla de verdad, forma normal, expresión booleana, etc., como el que usa una calculadora. De este modo el usuario ve el V-K de una forma normal, así se resuelve el ejercicio 3.1. La figura 3.1 muestra la carga de un V-K de cuatro variables con condiciones libres. Figura 3.1 Carga de un diagrama de Veitch-Karnaugh 33 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Simplificación de diagramas de V-K Una vez cargado el V-K basta con activar la opción Exp. SOP Simplificada o Exp. POS Simplificada, con lo que BOOLE simplificará desde los 1 o desde los 0, respectivamente. La figura 3.2 muestra la simplificación de un V-K tipo Gray. En ella podemos ver cómo aparecen pintados los lazos. Recuerde el lector que la expresión mínima no ha de ser única, puede que la que él esté pensando sea distinta a la presentada por BOOLE, siendo ambas correctas. Figura 3.2 Diagrama de V-K simplificado Modo aprendizaje Esta es la opción más valorada por los usuarios de BOOLE-DEUSTO. Puede que el lector no quiera ver la solución del BOOLE, sino que prefiera meter la suya y que BOOLE le diga si está bien. En este caso el lector debe cargar el V-K y luego activar la opción Modo Aprendizaje. Una vez hecho esto, basta con dibujar los lazos con simples clic de ratón: con el botón izquierdo se seleccionan las casillas y con el derecho se forma el lazo. Hecho esto, al activar Evaluar Solución, el BOOLE nos indicará si lo planteado es correcto o no. 34 © Universidad de Deusto - ISBN 978-84-9830-784-9 3. Diagramas de Veitch-Karnaugh Ejercicios 3.1 Simplifica las funciones representadas por su diagrama V-K. C f1 1 1 1 1 1 1 1 1 1 1 1 1 1 B D C f2 A A 1 B D 1 1 1 1 1 1 1 1 1 C f3 C f4 A 1 B D A 1 1 1 1 1 1 B 1 1 D 1 1 1 1 1 C f5 1 B D C f6 A 1 1 1 1 1 1 A B D 1 1 1 1 1 1 1 1 1 1 1 35 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales C f7 C f8 A B D 1 1 1 1 A 1 1 1 1 B 1 1 1 1 D 1 1 1 1 C f9 C f10 A 1 1 B D 1 1 1 A 1 1 1 1 1 B D 1 1 1 1 1 1 1 C f11 D C f12 A 1 B 1 A 1 1 1 1 1 B 1 1 D 1 1 36 © Universidad de Deusto - ISBN 978-84-9830-784-9 1 1 1 1 1 1 3. Diagramas de Veitch-Karnaugh C f13 C f14 A A 1 B D 1 1 1 1 1 1 B D 1 1 1 1 1 1 1 1 C f15 C f16 A 1 B D 1 1 1 1 B D A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 C f17 C f18 A A 1 B D 1 1 1 1 1 1 B D 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 37 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales C f19 B D C f20 A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 A 1 1 1 1 1 1 1 1 1 1 1 1 1 B D 1 C f21 B D C f22 A 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 A 1 B 1 D 1 1 1 1 1 1 1 C f23 B D C f24 A 1 1 X X X 1 1 B X D X 38 © Universidad de Deusto - ISBN 978-84-9830-784-9 A 1 1 1 X X 1 X 3. Diagramas de Veitch-Karnaugh C f25 C f26 A 1 B D X X 1 X X 1 B D A X 1 1 1 X 1 X 1 1 X X X 1 X 1 C f27 B D C f28 A 1 1 1 X X 1 1 1 A 1 X B D 1 X X X 1 1 X 1 C f29 B D 1 X C f30 A 1 1 1 X 1 1 1 1 1 1 X X X X A B D 1 1 1 1 1 X X 39 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales C f31 B D C f32 A X X 1 1 1 1 1 X 1 1 1 1 B A 1 D 1 X X X 1 1 X 1 1 C f33 C f34 A X B 1 X D X 1 B D A 1 X X 1 1 1 X 1 1 1 X 1 X X 1 1 C f35 B D C f36 A X 1 1 1 X 1 X 1 1 X B D 1 A X X X X X X X X X X X X X X X X 40 © Universidad de Deusto - ISBN 978-84-9830-784-9 3. Diagramas de Veitch-Karnaugh C f37 B D C f38 A 1 1 X X 1 1 X X 1 1 X X 1 1 X X A X B D X X X X 1 X X X X X X C f39 B D C f40 A 1 1 A 1 1 1 B 1 D 1 1 1 1 1 1 1 1 C f41 B D C f42 A 1 1 1 A 1 1 1 B 1 X 1 1 1 1 1 D 1 1 1 1 1 1 41 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales C f43 1 B D C f44 A 1 1 1 1 1 A 1 1 1 1 B D 1 1 1 1 1 1 1 1 1 1 1 1 1 C f45 C f46 A 1 B 1 A 1 1 1 D 1 B 1 D 1 1 1 1 1 1 C f47 B C f48 A 1 1 D 1 1 1 1 1 1 1 1 1 1 1 B D A 1 1 1 1 1 1 1 1 1 1 1 1 42 © Universidad de Deusto - ISBN 978-84-9830-784-9 1 1 1 3. Diagramas de Veitch-Karnaugh C f49 B D C f50 A 1 1 B X X X D A 1 1 1 X 1 1 X 1 1 1 1 X 1 C f51 1 B D C f52 A A 1 1 X X X X X B X X X X X D 1 C f53 B D C f54 A 1 X 1 X 1 1 1 1 B D A X X X X X X X X X X X X 1 1 43 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales C f55 C f56 A B D B X X 1 X X D A X 1 1 X 1 X 1 1 X 1 X 1 1 C f57 B D C f58 A X 1 1 X X 1 1 1 A B D 1 1 C f59 B D 1 C f60 A X X X 1 1 X X 1 1 X X X B D 44 © Universidad de Deusto - ISBN 978-84-9830-784-9 A X X X X X X X X 3. Diagramas de Veitch-Karnaugh C f61 C f62 A 1 X B D 1 1 1 A 1 1 1 1 B D 1 X X X X X X X 1 C f63 C f64 A 1 B D 1 A 1 1 1 B 1 1 1 1 1 1 D 1 X 1 1 X X 1 1 X X 1 X C f65 B C f66 A 1 1 D 1 A 1 X X X X X 1 1 B D 1 1 1 1 X X X X 1 X 1 45 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Plantea tus propios diagramas V-K C f67 C f68 A B A B D D C f69 C f70 A B A B D D C f71 C f72 A B D B D 46 © Universidad de Deusto - ISBN 978-84-9830-784-9 A 4. Sistemas combinacionales a nivel de bit o de puerta lógica Introducción metodológica En los anteriores capítulos hemos practicado con distintas herramientas básicas de análisis y diseño. Ahora con la caja de herramientas medio llena es momento de abordar diseños de cierta complejidad. Todo lo que vamos a hacer es aplicar los métodos vistos antes. La relación siguiente muestra el flujo de diseño (descendente) y el de análisis (ascendente). Con el diseño vamos con paso firme (gracias a los métodos) hacia una meta (el circuito lógico), y con el análisis comprobamos sin dudas (gracias a los métodos) que la meta alcanzada es la esperada (gracias a las especificaciones) • Descripción textual del sistema a diseñar. • Determinación de las variables de entrada y salida. • Tabla de verdad. • Forma normales. • Diagramas de Veitch-Karnaugh. • Expresiones mínimas. • Expresiones NAND/NOR u otras. • Circuito lógico. • Implementación mediante CI’s de puertas lógicas. Todos los pasos de esta lista son conocidos y dominados por el alumno, ahora solo debe aplicarlos con orden. El alumno debe saber que la calidad de todo el diseño depende de la tabla de verdad; de su verdad. Para obtener una correcta tabla de verdad son válidos algunos consejos: • lo bien escrito que esté el enunciado es muy importante, • plantea siempre 2n filas en la tabla de verdad, no quites filas, 47 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales • • • • • • • cada fila es una pregunta, la respuesta es la salida, entiende el enunciado o pide aclaraciones, la salida solo puede ser 0 ó 1, si no es una será la otra, utiliza las condiciones libres con responsabilidad, aunque una X no se deba dar, puede llegar a darse por desgracia, si tienes dudas con una fila, pasa a la siguiente y completa la tabla despacio, leyendo cada fila de entrada y escribiendo cada salida con cuidado y agilidad. 48 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica USO DE BOOLE-DEUSTO Inicialmente, BOOLE nace para resolver este tipo de ejercicios, así que este capítulo es su medio original. Veamos un ejemplo. Diseño de un sistema combinacional Al arrancar el BOOLE elegiremos la opción Sistema Combinacional. Seguidamente daremos nombre al sistema, indicaremos su número de variables de entrada y salida y si queremos podremos cambiar el nombre de las variables, que incialmente son A, B, ... para las entradas, y S0, S1... para las salidas. Todo esto se puede ver en la figura 4.1. Figura 4.1 Pantalla principal para sistemas combinacionales Una vez descrito el sistema, es momento de cargarlo mediante su tabla de verdad. Al activar la opción Tabla de Verdad Manual, el usuario podrá, mediante simples clic de ratón, asignar a cada fila el valor o valores correspondientes de salida. Recordemos que la tabla debe quedar completa, sin huecos, y que para ello podremos ayudarnos de la opción Completar Con. La figura 4.2 muestra la tabla de verdad de un circuito de complemento a 9. 49 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Figura 4.2 Tabla de verdad de un circuito de complemento a 9 Una vez cargada la tabla de verdad, activando Evaluar y Salir, podemos tomar dos caminos: seguir los pasos de diseño uno a uno o ir directamente a activar la opción Expresión SOP Simplificada. Sigamos el primer camino. Tras la tabla de verdad habrá que obtener las formas normales. Basta con activar Forma Normal Disyuntiva (vamos a trabajar desde los 1) y se obtendrá la figura 4.3. Figura 4.3 Formas normales del sistema 50 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica En la figura 4.3 sólo vemos una función, S0, para ver el resto hay que hacer clic sobre la barra de desplazamiento situada a la izquierda. Tras las formas normales (pulsar Salir) llega el turno de los diagramas de V-K. Basta con activar la opción Diagramas V-K para ver la figura 4.4. Si se activara la opción Diagramas V-K (2), se podría ver el V-K de tipo Gray. De esta manera se cubren los gustos de todos los profesores y diseñadores. Figura 4.4 Diagramas de V-K del sistema Una vez vistos los diagramas de V-K (para verlos todos hacer clic en la barra de desplazamiento), es el momento de la simplificación. Para ello basta con que se active la opción Expresión Simplificada SOP, obteniéndose lo mostrado en la figura 4.5. Figura 4.5 Expresiones simplificadas del sistema 51 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Además de la función simplificada BOOLE muestra los lazos de simplificación, relacionando cada uno de ellos con la expresión booleana correspondiente. La figura 4.6 muestra los lazos de la salida S2. Figura 4.6 Diagrama de V-K y lazos de la salida S2 del sistema En este punto el usuario puede optar por visualizar el circuito SOP directamente o por ver las expresiones NAND, NOR correspondientes. Para ver los circuitos hay que ir salida por salida, haciendo clic en la barra de desplazamiento a la izquierda de la figura 4.5. La figura 4.7 muestra el circuito lógico SOP de la primera salida. Figura 4.7 Circuito lógico SOP de la salida S3 del sistema 52 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Ejercicios 4.1 Tres sensores binarios miden una señal. Diseña el circuito digital que ofrezca en la salida el valor representativo de los tres sensores, es decir, el valor mayoritario. S2 S1 S0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 S 53 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.2 Un circuito tiene tres sensores lumínicos puestos a diferentes alturas, alto, mediano y bajo, SA, SM y SB. Si un diamante es grande interfiere las tres señales lumínicas, si es mediano, dos (SM y SB), si es pequeño, una (SB) y si es enano, ninguna. El sensor de peso en quilates (SP) que se pone a 1 si supera los tres quilates, y a 0 en caso contrario. Las condiciones son: • Un diamante grande (G) o mediano (M) debe pesar al menos 3 quilates, si no, se rechaza (R). • Si es pequeño, nunca debe pesar más de 3 quilates, en caso contrario es rechazado (R). • Los diamantes enanos se rechazan (R). • Las condiciones irreales, se consideran imposibles. SA SM SB SP 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 P M G Formas canónicas 54 © Universidad de Deusto - ISBN 978-84-9830-784-9 R 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 55 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.3 Un potente computador ha sido instalado en una sala de la universidad que debe permanecer a 2º centígrados, que es la temperatura correcta de funcionamiento del computador. La sala cuenta con un sensor de temperatura que indica la temperatura de la sala expresada en binario puro con signo en complemento a 2 siempre en el rango que va entre -6º y +6º centígrados, ambas temperaturas incluidas. En función de lo anterior el sistema cuenta con dos salidas, C y AC, que controlan a un calefactor y un aparato de aire acondicionado, respectivamente. Implementa el mínimo circuito capaz de controlar correctamente C y AC. T3 T2 T1 T0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 C AC Formas canónicas 56 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 57 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.4 Diseña el mínimo circuito que implemente el C-2 de un numero de cuatro bits. E3 E2 E1 E0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 C3 C2 C1 Formas canónicas 58 © Universidad de Deusto - ISBN 978-84-9830-784-9 C0 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 59 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.5 Diseña un circuito combinacional capaz de detectar un error en la codificación de un numero decimal en BCD. B3 B2 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 E Formas canónicas 60 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 61 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.6 Tenemos cuatro tanques (A, B, C y D). Los tanques A y B tienen un sensor que se activa cuando el nivel es demasiado alto. Por otra parte, los tanques C y D tienen un sensor que se activa cuando la temperatura es demasiado baja. Construir el diagrama lógico que activa la alarma cuando A o B tienen un nivel demasiado alto, o cuando la temperatura de C o D es demasiado baja. A B C D 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 AL Formas canónicas 62 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 63 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.7 Una veleta indica mediante cuatro señales N, S, E y O qué viento sopla, si es que sopla. Diseña el circuito mínimo que decodifique las anteriores señales sobre un 7-segmentos, según el siguiente criterio: • Si sopla del norte se activa el segmento a; si del sur, d. • Si sopla del este se activan b y c; si del oeste, se activan e y f. • Si sopla del noreste se activan a y b; si del noroeste, a y f. • Si sopla del sureste se activan c y d; si del suroeste, d y e. N S E O 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 a b c d Formas canónicas 64 © Universidad de Deusto - ISBN 978-84-9830-784-9 e f g 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 65 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.8 Implementa el mínimo circuito decodificador BCD a 7 segmentos. B3 B2 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 a b c d correspondiente e Diagramas de Veitch-Karnaugh 66 © Universidad de Deusto - ISBN 978-84-9830-784-9 f g a un 4. Sistemas combinacionales a nivel de bit o de puerta lógica 67 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.9 Se desean controlar dos bombas B1 y B2 en función de la cantidad de agua en un depósito. Los sensores B (nivel bajo de agua) y A (nivel alto de agua) entregan un uno lógico cuando el agua supera dicho nivel. Los sensores TB1 y TB2 indican mediante un uno si la temperatura de las bombas B1 y B2 ha superado el límite de funcionamiento. Si el nivel se encuentra: • por debajo de B se deben activar las dos bombas; • por encima de B pero por debajo de A se debe activar una bomba, preferiblemente B1 (teniendo en cuenta su temperatura); • por encima de A se deben desactivar B1 y B2; • si la temperatura del motor superara el límite, éste debería pararse. Cualquier situación anómala en los valores de los sensores conllevará la parada de ambas bombas por seguridad. TB1 TB2 B A 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 B1 B2 68 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 69 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.10 Diseña un comparador de dos números A y B de dos bits, que indique si A > B, A = B y A < B. A1 A0 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 A>B A=B A<B Formas canónicas 70 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 71 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.11 Una máquina dispone de cuatro ranuras de 25, 25, 10 y 5 pts. en las que cabe una única moneda. En la salida dispone de un mecanismo para ofrecer el producto. Para dar las vueltas tiene varios dispensadores de monedas de 5 y 10 pts, cada uno entrega una única moneda. Diseña el circuito que cuando el valor de la entrada iguale o supere las 40 pts entregue el producto y los cambios correspondientes. 25 25 10 5 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 Formas canónicas 72 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 73 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.12 La nota de un alumno se recibe codificada en binario puro. Obtén el mínimo circuito que visualice la nota en un 7 segmentos según la siguiente regla: • Suspenso (0-4): excita el segmento g. • Aprobado (5): excita el segmento a. • Bien (6): excita los segmentos a y b. • Notable (7-8): excita los segmentos a, b y c. • Sobresaliente (9): excita los segmentos a, b, c y d. • Matrícula de Honor (10): excita todos los segmentos menos el g. B3 B2 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 a b c d e Formas normales 74 © Universidad de Deusto - ISBN 978-84-9830-784-9 f g 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 75 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.13 • • • • Un proceso dispone de dos depósitos, DA y DB, con dos sensores cada uno: arriba y abajo (SA y SB). En total cuatro sensores. Ambos depósitos están conectados entre sí con VA (agua de A a B) y VB (agua de B a A). Hay tres niveles de paso de agua: 1, 3 o 5. Si ambos depósitos están al mismo nivel, entonces ambas válvulas se encuentran en el nivel 1 de apertura. Si un depósito está un nivel por encima del otro, entonces el que más tiene se pondrá a nivel 3, y el otro a 1. Si un depósito está dos niveles por encima del otro, entonces el que más tiene se pondrá a nivel 5, y el otro a 1. Nunca se podrán dar situaciones imposibles. ASA ASB BSA BSB VA3 VA2 VA1 VA0 VB3 VB2 VB1 VB0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 76 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 77 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.14 Implementa el mínimo circuito capaz de cambiar pesetas en euros. La máquina acepta monedas de 5, 10, 25 y 50 pesetas y puede entregar monedas de 1, 2, 5, 10 y 20 céntimos de euro. Téngase en cuenta que cada entrada y salida sólo puede recibir y entregar una sola moneda. P5 P10 P25 P50 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 Formas canónicas 78 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica 79 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.15 Implementa el mínimo circuito capaz de controlar los semáforos de una rotonda. La rotonda dispone de cuatro calles de entrada E3-0, en las que entran 5 coches por minuto, 15 c/m, 25 c/m y 30 c/m, respectivamente, y de cuatro calles de salida S3-0, que permiten el paso de 5 coches por minuto, 10 c/m, 20 c/m o 40 c/m, respectivamente. Si se sabe que nunca vendrán coches por más de dos calles de entrada a la vez, activar de forma adecuada los semáforos de las calles de salida para que éstos saquen tantos coches como los que entran. E5 E15 E25 E30 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 S5 S10 S20 Formas canónicas 80 © Universidad de Deusto - ISBN 978-84-9830-784-9 S40 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 81 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.16 Implementa un transcodificador de binario puro de cuatro bits a dos dígitos BCD. E3 E2 E1 E0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 A3 A2 A1 A0 B3 Formas canónicas 82 © Universidad de Deusto - ISBN 978-84-9830-784-9 B2 B1 B0 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 83 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.17 Implementa el circuito mínimo capaz de comparar dos números de dos bits codificados en binario puro con signo en complemento a 2. A1 A0 B1 B0 A>B A=B A<B 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 Formas canónicas 84 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 85 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.18 • • • Una máquina expendedora de golosinas tiene cuatro entradas: dos para el dinero introducido D1-D0 (10 y 5 céntimos de euro) y dos para seleccionar el producto P1-P0 (11 para pipas, 10 para chicles, 01 para cerillas y 00 para no comprar). Las pipas cuestan 10 céntimos, el chicle 7 y las cerillas 3. Implementa el mínimo circuito capaz de visualizar en un siete segmentos cuántos céntimos faltan o sobran para el producto elegido. Notas: Sin monedas en la entrada, el 7-segmentos no visualiza nada. No tiene sentido meter monedas sin seleccionar un producto. El usuario nunca meterá monedas desaprovechadas. Es decir, el usuario nunca meterá dos monedas, si llegara con cualquiera de las dos. Dicho de otra forma, siempre se podrá visualizar la cantidad en el 7-segmentos. D1 D0 P1 P0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 a b c d e 86 © Universidad de Deusto - ISBN 978-84-9830-784-9 f g 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 87 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.19 Implementa el mínimo circuito capaz de decodificar sobre siete diodos led (L6-L0) el valor de un dado de 1 a 6 codificado en BCD puro. Es decir, llega el valor de la tirada (de 1 a 6) codificado en BCD y hay que visualizarlo sobre siete diodos. Los siete diodos se disponen tres arriba, tres abajo y uno en medio, y la forma de activarlos será siguiendo el dibujo del dado. D3 D2 D1 D0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 L6 L5 L4 L3 L2 88 © Universidad de Deusto - ISBN 978-84-9830-784-9 L1 L0 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 89 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.20 Implementa el mínimo circuito capaz de dividir (cociente y resto) dos números binarios de dos bits cada uno. Tanto la entrada como las salidas estarán codificadas en binario puro con signo en C-2. A1 A0 B1 B0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 90 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica Diagramas de Veitch-Karnaugh 91 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 4.21 Diseña el mínimo circuito capaz de dividir dos números naturales de dos bits cada uno (A1A0 y B1B0), para obtener su cociente y resto. 4.22 Una cafetera cuenta con cuatro entradas: INT, NA, NB y C. La señal INT enciende (1) y apaga (0) la cafetera. Las señales NA y NB indican el nivel de agua de la cafetera, NA es un sensor en lo alto del depósito de la cafetera y NB es un sensor en la parte baja del depósito de la cafetera, indicando si no hay agua (NA=0 y NB=0), hay poco agua (NA=0 y NB=1) y hay mucho agua (NA=1 y NB=1). La señal C indica si hay poco (0) o mucho café (1). Los fabricantes quieren añadir un 7 segmentos a la cafetera para que el usuario vea cómo van las cosas: x Si INT está a 0, el 7 segmentos dibuja un 0. x Si INT es 1 el 7-segmentos indica lo fuerte que está el café: suave, normal y fuerte: x Si no hay agua se enciende una E mayúscula de error, independientemente del café. x Si hay mucha agua y poco café, el café es suave y solo se excita el segmento d (segmento inferior). x Si hay mucho agua y mucho café o hay poco agua y poco café, el café es normal y se excitan los segmentos d y g (los dos segmentos inferiores en vertical). x Si hay poca agua y mucho café, el café es fuerte y se excitan los segmentos a, d y g (los tres segmentos centrales). x Las posibles situaciones imposibles deben ser tratadas como condiciones libres. Diseña el circuito lógico capaz de excitar los 7-segmentos. 4.23 Obtén el circuito mínimo capaz de obtener el C-9 de un numero BCD. 4.24 Implementa el mínimo circuito que active una de dos salidas: led rojo y led verde. El led verde se activará cuando la temperatura de entrada se encuentre entre [–3 , +4] ºC, y el rojo en el resto de los casos. La temperatura estará codificada con cuatro bits en binario puro con signo en complemento a 2. 4.25 Implementa el mínimo circuito capaz de visualizar en un 7segmentos el número de 1 seguidos que contiene una entrada 92 © Universidad de Deusto - ISBN 978-84-9830-784-9 4. Sistemas combinacionales a nivel de bit o de puerta lógica de 4 bits. Los bits se empiezan a contar desde la derecha y hacia la izquierda, téngase en cuenta que si se rompe la secuencia de 1’s solo se tendrán en cuenta los 1’s hasta dicha rotura de secuencia. No es necesario que el bit de la derecha sea un 1 para contar, se puede empezar por 0. 4.26 Implementa el mínimo circuito capaz de obtener el valor absoluto de un número de cuatro bits codificado en binario puro con signo en C-2. La entrada siempre estará dentro del rango [-5, +5] y la salida visualizará en un 7 segmentos. 4.27 Implementa el circuito mínimo capaz de sumar dos números de dos bits codificados en binario puro con signo en C-2. La suma siempres deberá estar entre [-2 , +2]. 93 © Universidad de Deusto - ISBN 978-84-9830-784-9 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI Introducción metodológica En este capítulo abordamos la descripción y diseño de y con sistemas combinacionales funcionales o de palabra. Estos sistemas son: codificador, decodificador, multiplexor, demultiplexor, comparador, sumador, restador, generador/detector de paridad, etc. A la hora de diseñar con estos sistemas el método no es sistemático, sino más intuitivo y desordenado. Cada alumno en cada caso puede seguir una orientación top-down o bottom-up, osea, de lo total a lo particular, o viceversa. Está claro que en los diseños fáciles esta elección no tiene sentido, pero si el diseño es complicado debemos tomar una estrategia general, en mi caso prefiero de lo particular a lo general: bottom-up. Una buena forma de afrontar estos diseños es pensando que el circuito final es una frase y que las palabras que la forman son los distintos bloques conocidos. Así pensemos en términos de palabras y en cómo conectarlas para conseguir la frase deseada. Palabras más comunes: Codificador: pasa de un código decimal humano a uno binario máquina. Comunica el exterior con el interior. Decodificador: el complementario del codificador. Además puede verse como un señalador que activa a uno de varios. Multiplexor: encaminador, selector. Es un if hardware. Quizá el más versátil de los bloques. Demultiplexor: complementario del multiplexor. Muy parecido al decodificador. Los demultiplexores no son muy comunes. Comparador: lo que indica su propia palabra. Sumador, restador, etc.: lo que indica su propia palabra. 95 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Consejos de diseño con bloques funcionales Antes de empezar a juntar palabras para formar frases, hay que desterrar una aproximación muy común en los alumnos a la hora de diseñar: pensar en términos de software. Estamos utilizando hardware, y si hay algo distinto al software es el hardware (a pesar de que el primero se basa en el segundo). Nunca pensemos en qué acción abordar en cada momento, nunca utilicemos ideas como orden, depués, antes, tiempo, etc.; en hardware todo va a la vez. Es muy común implementar todas las opciones en hardware, y de todas ellas sacar al exterior una sola de ellas. Por ejemplo, con dos líneas de control: sumar(00), restar(01), multiplicar(10) y dividir(11). En software solo aplicaríamos una de las operaciones, la resultante del case o if; mientras que en hardware las implementaremos todas, y a través del un multiplexor solo pasará una de ellas al exterior. Otro consejo tiene que ver con usar cuidadosamente las líneas de control de los bloques, principalmente EI (enable input). Si tenemos varios bloques podemos hacer que solo uno de ellos se despierte, quedando el resto dormidos, utilizando sus líneas de EI y seguramente un decodificador para ver qué bloque es el que se despierta. Pocos consejos más se pueden dar. En este tipo de diseños la paciencia, la experiencia, la creatividad y el rigor son pautas a seguir, y nunca olvidemos que siempre podemos y debemos comprobar que lo que hace nuestro diseño es lo que esperábamos. Solo un comentario más. Si sirve de consuelo, valga decir que este tipo de diseño está siendo sustituido por la lógica programable (y otros sistemas microprogramados). En este nuevo campo la intuición sigue siendo un referente, pero de forma más metódica. 96 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI Ejercicios 5.1 Dos números decimales A y B son introducidos mediante sendos selectores. Se desea ver en un 7-segmentos sólo el mayor de ellos. Si ambos resultaran iguales, no se visualizaría nada. 97 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.2 Dos números decimales A y B son introducidos mediante sendos selectores. Se desea ver en un 7-segmentos el resultado de la resta, A-B, sólo en el caso de que ésta haya resultado positiva o cero, en caso contrario no debe visualizarse nada. 98 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.3 Dos números decimales A y B son introducidos mediante sendos selectores. Se desea ver en un 7-segmentos el resultado de la resta, A-B o B-A, que resulte positiva, según sea A>B o B<A, respectivamente. 99 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.4 Tres números decimales A, B y C son introducidos mediante sendos selectores. Se desea ver en un 7-segmentos sólo el mayor de ellos. 100 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.5 Una cancha de baloncesto de un equipo pobre dispone de cuatro selectores decimales para los puntos del equipo local y visitante, pero sólo de dos 7-segmentos para visualizar los puntos. Diseñar un circuito que con un interruptor I visualice los puntos del equipo local (I=0) o del visitante (I=1). Añadir un indicador para que el público sepa qué puntos está viendo. 101 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.6 Obtener el valor absoluto de un número de cuatro bits codificado en binario puro con signo en complemento a 2. 102 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.7 Disponemos de las notas, N1 y N0, de un alumno codificadas en BCD. Diseñar el circuito que obtiene la nota final según las preferencias del profesor expresadas con las líneas de control C1C0: • C1C0=00 Nota media redondeada por defecto. • C1C0=01 Nota mínima. • C1C0=10 Nota máxima. • C1C0=11 Nota media redondeada por exceso. 103 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.8 Cuatro países, A, B, C y D, votan en un consejo. Visualizar en un 7-segmentos el resultado de la votación sabiendo que en caso de empate decide el voto de calidad de A. Además, el país anfitrión tiene un interruptor de trampa para dar la vuelta al resultado. 104 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.9 En una votación los países están separados por bloques: cuatro países en A y tres en B. En un 7-segmentos se visualizará el resultado de la votación: si hay mayoría en A ése es el resultado, pero si hay empate en A el resultado lo marca B. 105 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.10 Basándote en un comparador de cuatro bits en binario puro, diseña un comparador de cuatro bits en complemento a 2. 106 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.11 Visualizar en cuatro 7 segmentos, y según el valor de P1 y P2, el mes, el día, la hora, los minutos, los segundos y las décimas de segundo del día en curso, y también la hora y los minutos de la alarma. P1 P2 Visualizado 0 0 HH MM (horas minutos) 0 1 SS DD (segundos y décimas) 1 0 HH MM (alarma) 1 1 MM DD (mes y día) 107 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.12 Completa la tabla de verdad de un decodificador BCD-7 segmentos suponiendo que todas las líneas son activas por nivel bajo. LT RBI E3 E2 E1 E0 0 0 0 0 0 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 0 0 0 1 1 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1 1 1 1 1 0 0 1 1 1 0 0 1 1 1 0 1 1 1 0 BI / a b c d e f g 1 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0 1 0 0 0 0 1 1 0 1 1 0 0 1 1 1 1 1 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1 0 1 1 0 1 1 0 1 0 1 0 0 1 0 0 1 0 1 0 0 0 0 0 1 0 0 0 1 1 1 1 RBO 108 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.13 Tres números decimales A, B y C son introducidos mediante sendos selectores. Se desea ver en dos 7-segmentos los dos números mayores ordenados de izquierda a derecha. Completa el circuito para que los números pares no se visualicen. 109 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.14 Para entrar en un recinto hay que pasar dos puertas, P1 y P2. Para entrar por P1 hay que introducir un dígito BCD mayor o igual que 5 y para pasar por la puerta P2 hay que introducir un número que esté entre tres unidades por arriba o por debajo de la mitad del número introducido en la puerta P1. Por ejemplo, si introducimos 8, entramos por P1 y debemos meter un número entre 1 (4-3) y 7 (4+3). 110 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.15 Un expendedor de golosinas recibe por un lado, codificado en cuatro bits en binario puro, el dinero introducido y por otro recibe de cuatro microrruptores, G, Ch, R y P (gominolas, chicle, regaliza y pipas) el producto solicitado. Si cada producto anterior cuesta 6, 7, 8 y 9 pesetas, respectivamente, implementa el circuito que visualice en un 7-segmentos cuánto dinero falta o sobra, y en dos diodos led si se debe entregar el producto (LP=1) o si el usuario debe completar el dinero (LD=1). 111 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.16 En una votación hay cinco países: A y B con valor doble que C, D y E. En un 7-segmentos se verá un 1 o un 0, según se haya ganado o perdido la votación. Si los tres países de menos peso se opusieran al voto de A y B, entonces el resultado quedaría vetado, y no se vería nada en el 7-segmentos. Por ejemplo, si A y B votaran SÍ (4) y C, D y E votaran NO (3), entonces no se vería nada en el 7-segmentos, pero si A, B, C, D y E votaran SÍ (7 votos), por supuesto que se vería un 1 en el 7-segmentos. 112 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.17 Una planta química dispone de dos depósitos de 9 litros A y B para albergar un determinado líquido. Ambos depósitos cuentan con un sensor que indica el nivel de llenado en litros del mismo mediante un código en BCD (NA, NB respectivamente). Además existen dos bombas, una capaz de traspasar líquido del depósito A al B, a la que llamaremos Bomba1 y que se activa mediante la señal de control B1 y la otra que traspasa el líquido del depósito B al A a la que llamaremos Bomba2 y que se activa a través de la línea de control B2. Implementa un circuito que busque mantener ambos depósitos al mismo nivel. Además se debe mostrar la diferencia en litros existente entre ambos depósitos mediante un display de 7 segmentos. En la visualización no importa si tiene más líquido A que B, o viceversa. 113 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.18 Un equipo de fútbol busca animar a su equipo en el partido de vuelta de la copa, para que el equipo se clasifique necesita ganar por dos o más goles. Tenemos como entradas dos dígitos BCD: goles del equipo de casa (GEC) y goles del equipo visitante (GEV) y el club está dispuesto a pagar si somos capaces de hacer funcionar una sirena mientras el equipo esté clasificado. Además, el club quiere que se visualice en un 7 segmentos los goles de diferencia, pero solo si estos favorecen al equipo local. 114 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.19 Un circuito tiene tres leds como salida: GanaA, GanaB y RepP que se activan en base a los goles que han metido dos equipos A y B codificados en BCD, GolesA y GolesB. Si la diferencia entre los goles de A y B es dos o mayor que dos, entonces se activa el diodo GanaA, y viceversa para el diodo GanaB. Ahora bien, si la diferencia de goles es uno o nula, entonces se activa RepP, que significa que deben repetir el partido. 115 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.20 Dos motores, M1 y M2, de una planta de montaje deben girar aproximadamente a la misma velocidad para que el ensamblaje de las piezas se realice correctamente. Cada motor cuenta con un medidor de vueltas por segundo que indica la velocidad a la que gira expresada mediante un código BCD, VM1 y VM2. Implementar un circuito que active una señal sonora cuando la velocidad de giro de los motores difiera en más de 2 unidades. Asimismo siempre que dicha diferencia de velocidad sea mayor que cero (el cero no se visualizará), esta se mostrará en un display de 7 segmentos y se activará uno de los dos diodos led LM1 o LM2 para indicar cuál de los dos motores va más rápido. Además cuando los motores giren exactamente a la misma velocidad se encenderá un LED que indicará el funcionamiento óptimo del sistema. 116 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.21 Las dos ruedas A y B de un robot deben ir a la misma velocidad, para ello cada una dispone de un acelerador y de un freno. El sistema entrega la velocidad de giro de cada rueda en BCD, estando su valor entre 0 y 9: VA y VB. Para conseguir que ambas ruedas vayan a la misma velocidad se plantea como estrategia restar las velocidades, aplicar la diferencia al freno de la rueda rápida y lo mismo con el acelerador de la rueda lenta. Por ejemplo si A va a 9 rpm y B a 6 rpm, entonces A se frena con valor 3 y B se acelera con valor 3. El circuito debe obtener el valor del acelerador y el freno de cada rueda: AA, FA, AB y FB. Además se quieren visualizar dichos valores siempre y cuando sean distintos de 0. Así el usuario verá cuánto está frenando y acelerando cada rueda. 117 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.22 Cada cuadrado negro de la figura es un pulsador del usuario. El sistema por sí solo activa cada una de las filas (ABC) y columnas (DEF) según qué pulsador se haya activado. Teniendo en cuenta que solo se puede activar un pulsador (o ninguno), diseñar el circuito que excite una de las nueve salidas S8-0. P0 P1 P2 D P3 P4 P5 E P6 P7 P8 F A B 118 © Universidad de Deusto - ISBN 978-84-9830-784-9 C 5. Sistemas combinacionales a nivel de palabra o MSI 5.23 Diseñar el circuito capaz de sumar/restar dos números de cinco bits cada uno, A4-0 y B4-0, codificados en binario puro con signo en C-2. Además del resultado se deben obtener tres flags o indicadores de resultado: • FZ: flag de cero, se pone a 1 si el resultado es cero. • FS: flag de signo, se pone a 1 si el resultado es negativo. • FO, flag de overflow, se pone a 1 si el resultado ha desbordado el rango de los cinco bits. 119 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.24 B4-1 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Dada la tabla del código ASCII, diseñar el circuito capaz de indicar en la salida si la entrada se corresponde con un número o una letra, indicando en este último caso si se trata de minúscula o mayúscula. Las salidas serán cuatro indicadores: de número N, de letra, L, de mayúscula M y de minúscula m. B7-5 B7-5 000 001 NUL DEL SQH DC1 STX DC2 ETX DC3 EQT DC4 ENQ NAK ACK SYN BEL ETB BS CAN HT EM LF SUB VT ESC FF FS CR GS SO RS SI US B7-5 010 SP ! " # $ % & ' ( ) • + ' . / B7-5 011 0 1 2 3 4 5 6 7 8 9 : ; < = > B7-5 100 A B C D E F G H I J K L M N O B7-5 101 P Q R S T U V W X Y Z [ \ ] - 120 © Universidad de Deusto - ISBN 978-84-9830-784-9 B7-5 110 \ a b c d e f g h i j k l m n o B7-5 111 p q r s t u v w x y z : ' DEL 5. Sistemas combinacionales a nivel de palabra o MSI 5.25 Un contador genera una secuencia de tres bits que se repite: 000, 001, 010,....110, 111, 000, etc. Se dispone de un visualizador con 8 segmentos en forma de cruz y aspa, es decir, como una tarta cortada en ocho pedazos (cuatro verticales y cuatro diagonales). Diseñar el circuito capaz de activar los segmentos según los siguientes criterios: • Activar uno y solo uno cada vez. El del centro superior para el 000, el siguiente diagonal para el 001, y así hasta llegar al último diagonal para el 111. • Activar cada vez un segmento más empezando con el central para el 000, luego se activarán el anterior y el siguiente, y por último se activarán todos con la opción 111. 121 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.26 Dadas cuatro entradas de cuatro bits cada una visualizar en un 7-segmentos el resultado de la media por defecto. Si la media es superior a 9, no se visualizará. Comprueba la validez del circuito con al menos estos cuatro ejemplos: NA=7, NB=7, NC=7 y ND=7; NA=6, NB=4, NC=5 y ND=5; NA=7, NB=6, NC=7 y ND=6; NA=10, NB=14, NC=15 y ND=9 122 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.27 Se reciben cuatro notas de un alumno, A, B, C y D se debe visualizar en un 7 segmentos la nota media por defecto, es decir, sin redondeo. Para visualizar la nota tienes dos opciones: ver la nota media tal cual o que se vea: un 3 si la nota es suspenso, un 5 si la nota está entre 5 y 6, un 7 si la nota está entre 7 y 8, y 9 y 10 si las notas son 9 y 10 respectivamente. 123 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.28 Di si el circuito adjunto se comporta como un sumador completo FA (A, B y Cin son entradas, mientras que S y Cout son salidas). Da alguna explicación o ejemplo para explicar lo dicho. Basándote en el anterior, dibuja el esquema de un sumador 4+4 bits. Cout B A C Mx 2:1 0 1 S Cin 124 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.29 Dado el siguiente circuito determina si se trata de un sumador completo o de un restador de 1 bit e indica el nombre de cada una de sus entradas y salidas. 125 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.30 Indica cuáles de los siguientes circuitos obtienen la media por exceso de dos números de cuatro bits expresados en binario puro sin signo. 126 © Universidad de Deusto - ISBN 978-84-9830-784-9 5. Sistemas combinacionales a nivel de palabra o MSI 5.31 Introduce las entradas de la tabla en el circuito, obtén el resultado e indica de qué operador aritmético se trata. B1 B2 B0 A0 A2B2 B2 A1B1 B1 B0 A0B0 A1 B2 A1B2 A2B1 A1B0 FA FA FA B1 B0 A2 P5 A2B2 A2B1 A2B0 FA FA FA P4 P3 P2 A2-0 B2-0 010 (2) 110 (6) 111 (7) 111 (7) 000 (0) 000 (0) 110 (6) 110 (6) 001 (1) 010 (2) P1 P5-0 P0 decimal 127 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 5.32 Dados tres números en binario puro sin signo de cuatro bits cada uno A, B y C, indica qué resultado se obtiene a la salida del siguiente circuito. A3-0 B3-0 4 4 A B Comp 4 Bits A<B A=B A>B C3-0 4 A B Comp 4 Bits A<B A=B A>B A B Comp 4 Bits A<B A=B A>B A>C A>B B>C C2 C1 C0 (4) (2) (1) C3-0 B3-0 No Usada A3-0 A3-0 No Usada C3-0 B3-0 E0(000) E1(001) E2(010) E3(011) E4(100) E5(101) E6(110) E7(111) 128 © Universidad de Deusto - ISBN 978-84-9830-784-9 MPX 4X8:1 4 5. Sistemas combinacionales a nivel de palabra o MSI 5.33 a) Tres señales AC, AD y AU indican si nuestro boleto de lotería coincide con las centenas (AC), decenas (AD) y unidades (AU) del número premiado. El circuito debe indicar si tenemos el premio gordo (coinciden todos los dígitos), el segundo premio (coinciden sólo decenas y unidades) o el reintegro (únicamente coincide las unidades). Indica cuál o cuáles de los siguientes circuitos son correctos y por qué. (2,5 puntos). AC AD AV b) AC AD AV E1(2) E2(4) E0(1) Decodificador 3:8 S7 S6 S5 S4 S3 S2 S1 S0 PG 2P REINT REINT PG c) AC PG AD 2P 2P AV REINT 129 © Universidad de Deusto - ISBN 978-84-9830-784-9 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables Introducción metodológica En este capítulo practicaremos con los biestables, que son la base del diseño secuencial. Para completar los ejercicios que a continuación se relacionan bastará con saber qué es sincronismo y cómo se comporta cada biestable. Comportamiento de biestables La siguiente tabla resume el comportamiento de los biestables asíncronos, síncronos por nivel o por flanco. Esquema S Tabla R 1 0 1 1 Qt-1 1 1 0 0 0 0 Q=Q=1 CK 0 1 1 D X 0 1 Qt Qt-1 0 1 Q R-S R Q D Ck Q D Q Ck CK n n n n Q J J-K K Q D Ck Q D J 0 1 0 1 K 0 0 1 1 CK n D Qt 0 1 0 1 n Q T Ck T Q T Q Qt S CK n n T 0 1 Qt Qt-1 1 0 Qt-1 Qt Qt-1 Qt-1 131 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Obtención de un cronograma Para obtener un cronograma solo hay que tener delante las tablas anteriores, marcar cada cambio en la entrada y en el reloj y dibujar la salida correspondiente. Es un proceso que debe ser cuidadoso y ágil, y no olvidemos que un fallo se arrastra a lo largo de todo el cronograma. Análisis de un circuito secuencial básico El método es el visto para sistemas combinacionales: elegir unos bits de entrada y ver qué efecto tienen en las salidas, teniendo siempre presentes las tablas anteriores. 132 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables Ejercicios 6.1 Completa los dos cronogramas adjuntos para una báscula R-S asíncrona con puertas NAND. S R Qt Qt t S R Qt Qt t 133 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.2 Completa el cronograma adjunto para unas básculas J-K síncronas por flanco ascendente y descendente, respectivamente Q↑ y Q↓. Ck J K Q↑ ↑ Q↓ ↓ t 134 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables 6.3 Completa los dos cronogramas cuidadosamente. En el primero el maestro es activo por nivel bajo, y el esclavo por alto. En el segundo es al revés. Ck D QM QS Q↑ t Ck J QM QS Q↓ t 135 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.4 Completa los cronogramas siguientes correspondientes a biestables síncronos tipo D, por flanco y por nivel, respectivamente. Ck D Q↑ Q↓ t Enable D QNA t 136 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables 6.5 Completa el siguiente cronograma. Ck JSDT KR J-K Q↑ Q↓ R-S Q D Q↑ Q↓ QNA QNB T Q↑ Q↓ t 137 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.6 Completa el siguiente cronograma. Ck JSTD KR J-K Q↑ Q↓ R-S Q T Q↑ Q↓ D Q↑ Q↓ t 138 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables 6.7 Completa el siguiente cronograma. Ck SJDT RK R-S Q Q’ T Q↑ Q↓ J-K Q↑ Q↓ D Q↑ Q↓ t 139 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.8 Completa el siguiente cronograma. Ck SJDT RK R-S Q Q’ T Q↑ Q↓ J-K Q↑ Q↓ D Q↑ Q↓ t 140 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables 6.9 Completa el siguiente cronograma. Ck SJDT RK R-S Q Q’ T Q↑ Q↓ J-K Q↑ Q↓ D Q↑ Q↓ t 141 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.10 La tabla de verdad adjunta describe el comportamiento de una báscula tipo W-V. Completa el cronograma adjunto. Ck W V Q(t) Operación ↑ 0 0 0 Puesta a 0 ↑ 1 1 1 Puesta a 1 ↑ 0 1 Q(t-1) Reposo ↑ 1 0 Q’(t-1) Basculamiento X-↑ X X Q(t-1) No sincronizado Ck W V Q↑ Q↓ t 142 © Universidad de Deusto - ISBN 978-84-9830-784-9 6. Biestables 6.11 Completa las tablas de verdad que describen a los siguientes circuitos lógicos. Indica a qué biestable corresponde cada circuito y qué señales son A, B y C. B A B Q A B Q(t) 0 Operación Q A A B Q(t) 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Operación B A Q C A B C 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 Q(t) Operación 143 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.12 Completa las tablas de verdad que describen a los siguientes circuitos lógicos. Indica a qué biestable corresponde cada circuito y qué señales son A y B. A A T B Q D B Ck Q Q Ck A B Qt-1 T ↑ 0 0 ↑ 0 ↑ Q(t) Q Ck Ck A B Qt-1 T 0 ↑ 0 0 0 0 1 ↑ 0 0 1 0 1 0 ↑ 0 1 0 ↑ 0 1 1 ↑ 0 1 1 ↑ 1 0 0 ↑ 1 0 0 ↑ 1 0 1 ↑ 1 0 1 ↑ 1 1 0 ↑ 1 1 0 ↑ 1 1 1 ↑ 1 1 1 0 X X X 0 X X X 144 © Universidad de Deusto - ISBN 978-84-9830-784-9 Q(t) 6. Biestables 6.13 Completa el cronograma adjunto para el circuito de la figura. ¿Cuál es el cometido de este sencillo circuito lógico? Ent D Q Q1 D Q Ck Q Q2 Sal Q Ck Ent Q1 Q2 Sal t 145 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 6.14 Dado el cronograma de la figura, completa la tabla adjunta que describe el comportamiento de este biestable fantasma. Explica con palabras qué hace. ¿Puedes implementarlo usando algún biestable ya existente? Ck E1 E0 Q t CK E1 E0 ↑ 0 0 ↑ 0 1 ↑ 1 0 ↑ 1 1 Q Función 146 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores Introducción metodológica En este capítulo se van a abordar diversos aspectos del diseño secuencial. Primero practicaremos con registros y contadores, y luego abordaremos diseños de cierta complejidad que incluyan registros y/o contadores y/o bloques combinacionales. Diseño de sistemas secuenciales con bloques funcionales Lo dicho para sistemas combinacionales en el capítulo 5 es válido de nuevo ahora. El diseño vuelve a ser intuitivo y muy dependiente de la complejidad del diseño y de la experiencia del diseñador. Una vez más es muy importante tener claro qué hace cada bloque: Registro paralelo-paralelo: memorización de datos. Registro de desplazamiento: conversión serie-paralelo y paralelo-serie y control por rotación de bits. Contador: cuenta tiempo y eventos. Estos dispositivos también cuentan con líneas de EI y similares, que con un uso inteligente potencian enormemente a los registros y contadores. 147 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Ejercicios 7.1 Completa el cronograma adjunto correspondiente al esquema de la figura. Indica de qué contador se trata. El contador se incializa con Q2-0=000. CK D Q Q2 Q1 Q0 D Q Q D Q Q Ck Q0 Q1 Q2 t 148 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.2 Diseña un contador síncrono módulo 10 basándote en el contador síncrono BCD CI 74160. Haz lo mismo para los contadores de módulo 1000, 60 y 12 en BCD. 149 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.3 Diseña un contador síncrono módulo 10 que al llegar a 9 se detenga, reanudando la cuenta al activarse el Clear. Es decir, cuenta de 0 a 9 y se detiene. 150 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.4 Diseña un reloj basándote en un reloj de entrada de frecuencia 1 Khz. Visualiza la secuencia en 7-segmentos. 151 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.5 Diseña un contador síncrono módulo 10 que cuente bien al ritmo de un reloj o bien al ritmo de un pulsador. Para que cuente con el reloj un interruptor I debe ser 0, y contará al ritmo del pulsador (da igual flanco de subida que de bajada) cuando el interruptor sea 1. 152 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.6 Una puerta se abre automáticamente si recibe síncronamente por la señal de entrada la secuencia 1011. Esta secuencia debe darse en los últimos cuatro flancos de reloj. Utiliza en el diseño un registro de desplazamiento. 153 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.7 Visualiza en un 7-segmentos el dígito BCD que se recibe en serie y sincronizado con una señal de reloj. Si el dígito recibido fuera erróneo no se visualizará. 154 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.8 Se dispone únicamente de 10 microrruptores y cuatro pulsadores para cargar cuatro dígitos de entrada en BCD. La entrada quedará cargada en sendos registros paralelos. 155 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.9 Se desea automatizar la obtención del premio que corresponde a cada boleto de lotería de tres números. Un circuito recibe en serie bloques de tres bits binarios. Cada uno de estos bits indica si el dígito en cuestión es igual al dígito del número premiado. En cuanto al orden, primero se recibe el bit con el resultado de comparar las unidades, luego el de comparar las decenas y se acaba con el de las centenas. Se desea activar en la salida uno o ninguno de los tres diodos led que indican el premio obtenido, P1, P2 y P3. Se gana el P1 si sólo coincide la cifra de las unidades, se gana el P2 si coinciden las unidades y las decenas y se gana el gordo, el P3, si aciertan todos los cifras. Los premios no se acumulan. 156 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.10 Diseña un circuito capaz de multiplexar sobre cuatro 7segmentos el contenido de cuatro dígitos BCD. Esto es, para los cuatro 7-segmentos disponemos de 7 entradas y de cuatro de líneas de enable, una para cada 7-segmentos. Diseña el circuito de visualización si se parte de una señal de reloj de 200 hz. Repite lo mismo para un reloj de 1 Khz. 157 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.11 Un microbot tiene en una rueda cuatro marcas ópticas. Se desea activar una alarma cuando la rueda dé más de tres vueltas por segundo. Téngase en cuenta que la frecuencia del reloj es 100 hz. 158 © Universidad de Deusto - ISBN 978-84-9830-784-9 7. Registros y Contadores 7.12 Diseña con circuitos tipo MSI el circuito capaz de indicar que un usuario ha ganado el juego. El juego consiste en que el usuario accione un pulsador J al menos tres veces en un segundo. Para controlar el juego disponemos de un reloj de 10 Hz. Las salidas serán dos: por un lado un 7-segmentos mostrará cuántas veces se ha pulsado en el segundo en juego y por otro un zumbador se activará mientras el usuario no iguale o supere los tres pulsos de J en el segundo en juego, es decir, que pite mientras el jugador esté perdiendo. Añade un pulsador P para reiniciar el juego una vez finalizada una partida. 159 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 7.13 Diseña con circuitos tipo MSI el circuito capaz de abrir y cerrar la puerta de entrada de una empresa: M=01 abre, M=10 cierra y M=00 se para. La puerta tiene un sensor óptico que entrega un 1 cuando detecta a una persona, SP. En la situación anterior la puerta se abre durante un tiempo que va de 4 a 9 segundos, según lo introducido en cuatro microrruptores. Si una persona se para delante de la puerta (del sensor), la puerta está abierta todo el tiempo, y no solo los 4-9 segundos. Además de lo anterior, el sistema tiene un led que parpadea al ritmo de un segundo mientras se abre o cierra la puerta. El reloj, CK, tiene una frecuencia de 10 Hz. 160 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas Introducción metodológica En este capítulo practicarás el diseño de autómatas, tan de Moore como de Mealy. Autómatas: Sistemas secuenciales a nivel de bit Si los ejercicios del capítulo 4 eran combinacionales, los de este capítulo son los correspondientes secuenciales. El diseño de aquéllos y éstos se parece metodológicamente. En el diseño combinacional se partía de un texto del que obteníamos una tabla de verdad, y de ésta y tras una serie de manipulaciones obteníamos el circuito lógico. Pues bien, en los autómatas el método es muy parecido, sólo que del texto se obtiene el diagrama de transición de estado (DTE), y de éste el circuito lógico. Si en el diseño combinacional el paso más delicado era obtener la tabla de verdad (de su acierto dependía el resto), en los autómatas es obtener el DTE. El DTE es a los sistemas secuenciales lo que la tabla de verdad era para los combinacionales. Un DTE se compone de entradas, salidas, estados y transiciones. Determinar las dos primeras es relativamente fácil, pero determinar los estados puede ser una tarea difícil, que necesita de experiencia. Para obtener un DTE hay que tener en cuenta que: • a veces se puede conocer el número de estados a priori, normalmente no, • los estados coinciden con justamente eso: los estados de la evolución del autómata, • los estados a veces coinciden con los participios o gerundios que aparecen al leer o contar el enunciado, • de un estado deben salir en principio 2n transiciones, donde n es el número de entradas, • puede que haya transiciones imposibles, saliendo menos de 2n transiciones de cada estado, • en un autómata con entradas asíncronas, las transiciones de entrada a un estado suelen rebotar en él (autolazo), 161 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales • • • • • • • es muy interesante contar (narrar) la historia o evolución de un autómata para obtener su DTE, es muy corriente que la historia de un DTE no sea única, que haya varias, así podremos hablar de distintos escenarios, el autómata es algo dinámico, mientras que la tabla de verdad es estática, no puede haber transiciones idénticas saliendo de un mismo estado: es síntoma de que ese estado debe subdividirse en dos, un autómata no debe chirriar, debe ir suave; debe dar la sensación de que el DTE describe con normalidad al autómata, al encajar nuevas situaciones o escenarios al DTE en curso, éstas deben unirse a él con suavidad (sin chirriar), expresión de que el DTE está bien y una vez obtenido el DTE a partir del enunciado, también se puede ir al revés, leyendo las historias que el DTE cuenta. Diseño de un autómata Los autómatas pueden ser de Moore o de Mealy, y ambos tienen parecidos y diferencias. Para ahondar en las diferencias teóricas lo mejor es acudir al libro. Algunas diferencias prácticas son: • algunos enunciados piden Moore y otros Mealy, pero la mayoría son indiferentes al tipo de autómata, • en Mealy la salida es obtenida antes que en Moore; Mealy es más ágil y nervioso que Moore, que es más ordenado y tranquilo, • los estados en Mealy suelen o pueden ser más abstractos que en Moore, • los estados en Moore coinciden mejor con los participios y los gerundios antes comentados, • suele ser más cómodo obtener el DTE de Moore que el de Mealy, pero es cuestión de gustos, • Mealy suele o puede tener menos estados que Moore, es más económico, • en el diseño de Moore hay que plantear más tablas que en el de Mealy y • en muchos casos los circuitos de Moore y de Mealy se comportan de igual modo. 162 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas Una vez obtenido el DTE que describe al autómata, para llegar al circuito lógico correspondiente basta con seguir los pasos mostrados en la siguiente figura. Enunciado Textual Comprensión, Experiencia e Intuición Tabla de Transición de Estados Diagrama de Transición de Estados Reordenación Método de Equivalencia entre Estados Tabla de Transición de Estados Mínima Codificación de Estados Tabla de Transición de Estados Codificada Tablas de Verdad de los Biestables Tabla de Excitación de Biestables Diagramas de Veitch-Karnaugh Expresiones Simplificadas Implementación Circuito Lógico y Digital En esta nueva edición no se contempla el diseño “manual” de autómatas, ya que actualemente en ningún caso se hace así, y su aprendizaje no aporta mucho al alumno. 163 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales USO DE BOOLE-DEUSTO BOOLE está específicamente desarrollado para plantear, simular e implementar autómatas finitos deterministas, también llamados máquinas de estados finitas. Captura del autómata Lo primero que hay que hacer es activar la opción de Sistema Secuencial en la pantalla principal del BOOLE, apareciendo la figura 8.1. Figura 8.1 Pantalla principal para sistemas secuenciales Dentro de la pantalla principal habrá que activar la opción Nuevo dentro del menú Archivo. En la figura 8.2 se describe el autómata como de Mealy, con una entrada y una salida (no hace falta saber a priori cuántos estados tendrá el DTE). Figura 8.2 Descripción del autómata 164 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas En este momento se puede empezar a dibujar el DTE sobre la zona de trabajo. La paleta superior izquierda de la figura 8.1 es todo lo que nos hace falta. Por ejemplo, si hacemos clic sobre el círculo de la paleta, por cada clic en la zona de dibujo aparecerá un nuevo estado, etiquetado automáticamente por el BOOLE. Por ejemplo, en la figura 8.3 se han dibujado ya cinco estados. Figura 8.3 Dibujo de los cinco estados del autómata Ahora falta dibujar las transiciones. Para esto habrá que elegir la flecha pequeña de la paleta. Seguidamente al hacer clic sobre un estado (inicio) y sobre otro (destino), el BOOLE dibuja la transición. La figura 8.4 muestra el DTE con las transiciones. Figura 8.4 Captura de las transiciones del DTE 165 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Al dibujar las transiciones pueden darse situaciones mejorables (ver figura 8.4): • alguna flecha no pasa por donde nos gustaría o • alguna flecha está justamente sobre otra o • a alguna flecha no se le ve la punta (está debajo del estado) o • el estado no está donde nos gustaría, etc. Resumiendo, que nos gustaría modificar el aspecto del DTE. Pues simplemente hay que ir a la paleta, seleccionar la flecha grande, hacer clic (no doble clic) sobre el estado o la transición elegida y arrastrarlo hasta el nuevo lugar. La figura 8.5 muestra al DTE reordenado. Figura 8.5 Reordenación del DTE Como se puede comprobar con BOOLE, al mover un estado, se mueven las transiciones a él asociadas. Por otra parte, para mover un estado basta con agarrarlo por cualquier lado, pero para mover una transición justo hay que agarrarla por la flecha, si no no se mueve. En los autolazos, la flecha es el cuadradito pequeño. Al mover la flecha, podemos curvarla, girarla, etc. Queda una cuestión, ¿cómo agarrar una transición cuya flecha está debajo del estado? Pues no hay otra solución que mover el estado, coger la flecha y reordenarlo todo. La interface de captura del DTE es bastante ágil, pero no quiere ser completa. Es decir, puede que al lector le cueste o no pueda obtener el dibujo que quiere; en este caso es mejor ir al Paint u otros programas similares. 166 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas Para borrar un estado o transición basta con elegir la flecha grande de la paleta (si no no borra), hacer clic sobre el estado o la flecha de la transición y finalmente activar el botón derecho del ratón. En cualquier caso, el lector puede cargar, mover, modificar y borrar el DTE en el orden que le dé la gana. El mostrado hasta ahora es puramente descriptivo. Una vez cargado el aspecto gráfico del DTE, queda dar sentido al autómata, es decir, etiquetar los estados y transiciones. Simplemente hay que seleccionar la flecha grande de la paleta, hacer doble clic sobre el estado o la flecha de la transición elegida y escribir los bits deseados. La secuencia asociada a cada transición o estado puede tener 1, 0 o X, condiciones libres. Eso sí, BOOLE no permite transiciones por defecto, ni quitar alguna entrada, ni trucos por el estilo. Habrá que dibujar todo lo que queremos que pertenezca al DTE. En la figura 8.6 se puede ver el DTE ya completo. En él, además de etiquetar las transiciones, se han cambiado los nombres de los estados. El autómata de la figura es el detector de secuencias 1010 y 110 con solapamiento. Figura 8.6 DTE del autómata completamente descrito En este momento podemos activar la opción ¿Es determinista? o ¿Es correcto? del menú Resultados, y BOOLE nos dirá si falta alguna transición o si alguna esta duplicada. Lo primero puede ser normal (transición imposible) y lo segundo es un error. En la figura 8.7 se ve el mensaje de todo está correcto (por lo menos topológicamente). 167 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Figura 8.6 Comprobación del autómata cargado Procesado del autómata Una vez cargado el autómata hay que procesarlo, implementarlo. En este punto, BOOLE ofrece varios caminos, vayamos por el más común. Si se activa la opción Diseño del Autómata del menú Resultados se obtendrá la figura 8.7. En ella se ve todo el proceso de diseño: tablas de transición, de codificación, de excitación, ecuaciones booleanas, para f-f tipo D, tipo J-K, etc. La información que se ofrece es completa, e incluye no sólo el resultado (las expresiones simplificadas), sino también todo el proceso, todos los pasos. Así el lector podrá comprobar su proceso de diseño paso por paso. Figura 8.7 Pantalla de diseño de autómatas 168 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas El siguiente paso será ver el circuito lógico. Para ello bastará con activar la opción Con flip-flop tipo J-K dentro del menú Ver Circuitos (también se pueden elegir los f-f tipo D). La figura 8.8 muestra el circuito lógico del detector de secuencias diseñado. Figura 8.8 Circuito lógico con flip-flop tipo J-K El proceso ha finalizado, pero BOOLE todavía nos ofrece el poder capturar el circuito y las tablas generadas para copiarlas o imprimirlas. Esta opción es muy cómoda, sobre todo para documentar el ejercicio resuelto. Simulación de un autómata Otra posibilidad es simular el autómata capturado. Este paso es muy importante, y muchas veces es olvidado: siempre tenemos prisa por diseñar, por obtener el circuito, sin preocuparnos de comprobar la validez del DTE. BOOLE ofrece cuatro modos de simulación: normal o Detallada y Batch o Interactiva. Las más interesantes de momento son las simulaciones Interactiva o Batch normales, no las detalladas. Al elegir Simulación Batch dentro del menú Resultados, el lector se encontrará con la figura 8.13. En ella debe escribir los valores que asocia a la entrada en cada flanco de reloj. 169 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Figura 8.13 Pantalla de simulación batch de autómatas En la figura se puede ver que se van a simular 9 filas, que la dos primeras son de RESET, y que luego el usuario puede ir dando valor a la entrada E0 mediante simples clic de ratón. En este paso es muy importante que la secuencia de entrada elegida sea buena, que analice bien al DTE, que lo retrate. La entrada debe contener todas las situaciones que queramos controlar en el DTE. Al pulsar Iniciar Simulación (y las subsiguientes opciones) se irá viendo la simulación. Se podrá ver el estado en el que se encuentra el autómata y la salida correspondiente. La figura 8.14 muestra el resultado de la simulación. 170 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas Figura 8.14 Simulación batch completada para el detector de secuencia En la figura 8.14 se puede ver que el DTE funciona correctamente, y que la salida se pone a 1 cuando lo recibido es 110 o 1010, permitiendo el solapamiento. Además, la simulación nos muestra por dónde ha ido el DTE, por qué estados. Esta pista o camino de estados viene muy bien cuando hay que corregir el DTE (cuando está mal), ya que nos dice por dónde ha ido. Al simular, podemos guardar la simulación con su secuencia de entrada, para volverla a probarla después de modificar el autómata. Además, podemos imprimir o copiar el resultado de la simulación. Todo en formato texto, para que podamos editarlo. La figura 8.15 muestra el Log de la simulación anterior. 171 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Figura 8.15 Log de la simulación batch En cuanto a la simulación Interactiva, en ella el usuario va introduciendo la entrada sobre la marcha, según se le va ocurriendo. Esta técnica es más ágil, incluso es más divertida, pero parece más responsable hacerlo de forma batch. En cualquier caso, también se puede acceder al Log y salvarlo, imprimirlo y copiarlo. La figura 8.16 muestra lo que ve el usuario: según va metiendo datos se van encendiendo los estados por los que pasa el autómata. Figura 8.16 pantalla de la simulación Interactiva En la parte izquierda de la figura 8.16 se ven los controles de la simulación. RESET para reiniciar la simulación, E0 para cambiar la entrada con clics de ratón y CLK para generar un flanco de reloj y que 172 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas el DTE simule. Con la práctica se denomina rápidamente este modo de simulación. Por último, la simulación Detallada se distingue de la Normal, en que la primera permite al usuario cambiar el valor de la entrada entre flancos. Es decir, permite ver el comportamiento asíncrono del autómata. Esta forma de simular tiene sentido sobre todo para destacar la diferencia que hay entre un autómata de Mealy y uno de Moore. Por lo demás, todo es igual a la simulación vista hasta ahora. Antes de pasar al siguiente punto es conveniente recalcar la importancia de la simulación, que nos dará una imagen clara de lo que hace nuestro autómata, no de lo que pensábamos que iba a hacer. Simular es verificar, y nadie implementa sin haber verificado el diseño en la medida de lo posible. En los ejercicios no se han planteado simulaciones mediante BOOLE para no cargar innecesariamente el libro, pero bien puede hacerlas cada lector por su cuenta. 173 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales Ejercicios 8.1 Diseña el autómata de Moore capaz de detectar tres o más unos consecutivos en la línea de entrada. Diagrama de transición de estados 174 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.2 Diseña el autómata de Moore capaz de detectar en la línea de entrada la secuencia 1011, teniendo en cuenta posibles solapamientos en la secuencia. Diagrama de transición de estados 175 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.3 Diseña el autómata de Moore capaz de detectar tres o más unos o ceros consecutivos en la línea de entrada. Diagrama de transición de estados 176 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.4 Diseña el autómata Moore capaz de detectar en la línea de entrada las secuencias 1111 y 11011, teniendo en cuenta posibles solapamientos en las secuencias, así como el paso de una secuencia a otra. Diagrama de transición de estados 177 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.5 Diseña el autómata de Moore capaz de detectar en la línea de entrada las secuencias 1010 o 110, permitiendo solapamientos y paso entre secuencias. Diagrama de transición de estados 178 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.6 Diseña el autómata Moore capaz de detectar en la línea de entrada las secuencias 101 y 010, permitiendo solapamientos y paso entre secuencias. Diagrama de transición de estados 179 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.7 Diseña el autómata Moore capaz de detectar el posible error en la transmisión de un mensaje a través de una línea serie. El código de transmisión es el Manchester que asocia a cada bit a transmitir dos bits, así el cero se codifica como 0-1, y el 1 como 1-0. Para iniciar la transmisión o reiniciarla después de un error se dispone de un pulsador P. Diagrama de transición de estados 180 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.8 Diseña el autómata de Moore que implemente un contador módulo 4 reversible según la línea de control MODO; si vale 1 cuenta ascendentemente, si vale 0 descendentemente. Cuando se produzca el paso de un modo a otro se empezará por el primer estado de la nueva secuencia. Diagrama de transición de estados 181 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.9 Diseña el autómata Moore que implemente un contador módulo 8 según la línea de control MODO; si valiera 1 contaría ascendentemente, si valiera 0 no contaría, manteniéndose en su estado. En el paso de reposo (MODO=0) a contaje el nuevo estado será el posterior al actual, por ejemplo de 4 en reposo se pasará a 5. Diagrama de transición de estados 182 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.10 Diseña el autómata de Mealy que implemente un sumador serie. Los bits llegan por dos líneas bit a bit, de menor a mayor peso, en la salida se debe obtener la suma de los bits en curso, teniendo en cuenta los acarreos. Diagrama de transición de estados 183 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.11 Diseña el autómata de Moore que implemente un sumador serie. Diagrama de transición de estados 184 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.12 Obtén el autómata Moore correspondiente a un registro de tres bits de desplazamiento a la derecha. Haz lo mismo para un un desplazamiento a la izquierda y para uno derecha/izquierda con línea de CONTROL. Diagrama de transición de estados 185 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.13 Diseña el automáta Moore capaz de generar el bit de paridad par desde los 1’s para un mensaje de tres bits. El mensaje se recibe en serie bit a bit, cada tres bits la salida deberá tomar el valor correspondiente al criterio enunciado, durante los dos primeros bits, arbitrariamente, la salida valdrá cero. Diagrama de transición de estados 186 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.14 Diseña el automáta Moore capaz de generar el bit de paridad par desde los 1’s para cuatro bits. El mensaje se recibe en serie bit a bit, cada cuatro bits la salida debe tomar el valor correspondiente al criterio enunciado, durante los tres primeros bits, arbitrariamente, la salida valdrá cero. Diagrama de transición de estados 187 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.15 Diseña el autómata Moore que se comporte como un codificador 4:2 con prioridad. Los cuatro de bits de entrada se recibirán secuencialmente empezando por el de menos peso. Obtén asimismo únicamente el diagrama de transición de estados si la entrada en serie comenzara por el bit de más peso. Diagrama de transición de estados 188 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.16 Diseña el autómata de Moore que se comporte como un comparador. En todo instante el autómata indicará si la secuencia A es mayor, menor o igual que la secuencia B. Ambas secuencias se recibirán en serie empezando por el bit de menos peso. Piensa en cómo sería el autómata si se empezara por el bit de más peso. Diagrama de transición de estados 189 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.17 Un limpiaparabrisas tiene pulsadores de marcha y paro -M y P-. Si se pulsa M se activa, si se pulsa P se para, además es prioritario el pulsador de parada. Implementa el autómata Moore capaz de controlar el limpiaparabrisas. Diagrama de transición de estados 190 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.18 Un limpiaparabrisas idéntico al anterior, pero dispone de un detector detector de reposo –R-, de tal forma que cuando activamos la parada, ésta no se produce hasta que el limpiaparabrisas haya alcanzado la posición de reposo. Diseña el autómata Moore que controle el limpia. Diagrama de transición de estados 191 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.19 Un limpiaparabrisas con detector de reposo R y un único pulsador P. Si se pulsa pasa al estado contrario que estaba, y ahí se mantiene hasta que estando en reposo el pulsador éste se vuelva a activar, pasando por tanto al estado contrario. El limpia no se para hasta alcanzar el reposo. Diseña el autómata Moore que controle el limpia. Diagrama de transición de estados 192 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.20 Una puerta se abre al activar un pulsador. La apertura se produce hasta que alcanza el tope de apertura, detectado por el sensor A. A partir de ese momento se produce el cierre de la puerta, hasta alcanzar el tope de cierre, detectado por el sensor C, y en ese momento se produce la parada. Diseña el autómata Moore que controle la puerta. Diagrama de transición de estados 193 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.21 Un depósito de agua que da servicio al consumo dispone de dos bombas de llenado B1 y B2 y de dos sensores de nivel, inferior y superior, respectivamente. Si el nivel estuviera por debajo del inferior se activarían ambas bombas, si el nivel estuviera por encima del superior nos se activarían las bombas y si el nivel estuviera entre el superior y el inferior se activaría una única bomba, aquella que lleve más tiempo inactiva. Diseña el autómata Moore que controle B1 y B2. Diagrama de transición de estados 194 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.22 Hay que controlar las puertas de cristal de un edificio. Disponemos de un detector de personas P, de un detector de puerta abierta A y de un detector de puerta cerrada C. Si viene un persona se abre la puerta. Si la puerta empieza abrirse, completa su ciclo entero aunque desaparezca la persona. Si sigue apareciendo gente la puerta permanece abierta continuamente. Si cuando estaba cerrándose la puerta aparece una persona, la puerta vuelve a abrirse, completando un nuevo ciclo. Diseña el autómata Moore que controle el motor de las puertas. Diagrama de transición de estados 195 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.23 Un motor dispone de dos pulsadores PA y PP, de arranque y parada, respectivamente. Si el motor estuviera quieto y se pulsara PA, el motor no giraría hasta que se soltara PA, y viceversa, si el motor estuviera girando y se pulsara PP, el motor no se pararía hasta que se soltara PP. Es decir, la activación o desactivación se produce por paso de 1 a 0. Repetir el ejercicio con un único pulsador P: si el motor estuviera girando la activación del pulsador lo pararía, y su estuviera parado la activación del pulsador lo arrancaría. Diseña el autómata Moore que controle el motor. Diagrama de transición de estados 196 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.24 En un desvío de trenes se desea automatizar el cambio de vía. Si el tren es largo debe ir por la vía A (A=1) y si es corto por la vía B (B=1). Para saber si un tren es corto o largo disponemos de dos detectores ópticos (E y S) separados entre sí 50 metros: si en algún momento los detectores están ON el tren es largo, siendo corto en caso contrario. Supóngase que mientras se mide un tren otro no puede entrar en la zona de medidad y que el desvío está suficentemente lejos como para que todo vaya bien. Diseña el autómata Moore que controle las vías A y B. Diagrama de transición de estados 197 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.25 Un microbot se usa para recoger las piezas fabricadas por el operario en B y llevarlas a A para empaquetarlas. Así el microbot va de A a B, el operario tiene un pulsador P y el microbot tiene dos bumpers (BA y BB). El microbot está en A en reposo y al pulsar P el operario va hacia a B para coger la pieza, al llegar a B retorna a A para llevar la pieza y detenerse hasta un próximo pulso en P, pero si mientras está regresando de B a A se pulsara de nuevo P, entonces el microbot regresaría a B para recoger una nueva pieza y luego volver a A. Es decir, P inicia el ciclo y P lo interrumpe para volver a B. Controlar el motor del microbot con dos salidas S10: quieto (S10=00), deAaB (S10=01) y deBaA (S10=10). Diagrama de transición de estados 198 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.26 Un secador de pelo, S, en un vestuario tiene un pulsador, P, y un detector de persona bajo el secador, D. Cuando se pulsa (P=1) y hay alguien debajo (D=1), el secador se activa, y lo seguirá haciendo mientras haya alguien debajo, aunque se suelte el pulsador. El secador se para al no haber nadie debajo. Controlar la activación del secador. Diseña el autómata Moore que controle el secador. Diagrama de transición de estados 199 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.27 Diseña un contador módulo cuatro controlado por un pulsador P, por cada pulso el contador aumenta en uno su valor. Plantea dos soluciones, una que cuenta al apretar el pulsador y otra que lo hace al soltar el pulsador. Modifícalo para que cuente de 0 a 3 y se pare, recomenzando la cuenta con un pulsador de inicio, PI. Diagrama de transición de estados 200 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.28 Para abrir una caja fuerte se dispone de dos pulsadores, P1 y P0. Si se pulsa P1 (nivel alto) se genera un 1, y si se pulsa P0 (nivel alto) se genera un 0. La caja fuerte se abrirá con la secuencia 110011. En cuanto la secuencia sea errónea, se activará la salida de AL de alarma. Para intentar una nueva clave, habrá que reiniciar con Clear. Diseña el autómata Moore que controle la apertura de la caja fuerte. Diagrama de transición de estados 201 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.29 En un juego con dos jugadores cada uno dispone de un pulsador, PA y PB, gana aquel que pulse antes que el otro después de oir/ver una señal del juez. El resultado se visualizará en dos diodos led, LA y LB, según quién gane. El juego no recomenzará hasta activar el Clear. Modificar el diseño para incluir un pulsador de Inicio y otro para el juez, J. Además habrá un nuevo diodo que se active al pulsar el juez para indicar partida en juego. Diseña el autómata Moore que diga quién gana. Diagrama de transición de estados 202 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.30 La unidad de control de un computador necesita recibir como primer flanco del reloj uno ascendente. Diseña el circuito que tiene como entradas las señales de Clear y Ck y que debe obtener como salida una nueva señal de reloj CK’ cuyo primer flanco, tras la activación del Clear, sea uno ascendente. Diseña el autómata Moore que genera Ck’. Diagrama de transición de estados 203 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.31 Se desea automatizar la obtención del premio que corresponde a cada boleto de lotería de tres números. Un circuito recibe en serie bloques de tres bits binarios. Cada uno de estos bits indica si el dígito en cuestión es igual al dígito del número premiado. En cuanto al orden, primero se recibe el bit con el resultado de comparar las unidades, luego el de comparar las decenas y se acaba con el de las centenas. Se desea activar en la salida uno o ninguno de los tres diodos led que indican el premio obtenido, P1, P2 y P3. Se gana el P1 si sólo coinciden las unidades, se gana el P2 si coinciden las unidades y las decenas y se gana el gordo, el P3, si aciertan todos los dígitos. Diseña el autómata Moore que controle P1, P2 y P3. Diagrama de transición de estados 204 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.32 Diseñar el autómata capaz de generar un pulso de nivel 1 y duración 1 pulso de reloj por cada pulso de una señal externa y duración t>1 pulso de reloj. Es decir, convertir un pulso de duración t en un pulso de duración T. Trabaja con tres opciones: • Detectar el flanco de subida. • Detectar el flanco de bajada. • Detectar el flanco de subida y de bajada. Diagrama de transición de estados 205 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.33 Copiar en la salida la señal de entrada, pero con un flanco de retardo. Diseña el autómata Moore que obtiene la anterior salida. Diagrama de transición de estados 206 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.34 Una línea de transmisión está a nivel alto en reposo y transmite bloques de tres bits. Para enviar un bloque de tres bits, primero la línea pasa a 0, luego vienen los tres bits, luego pasa a 0 de nuevo, para quedar finalmente a 1 en reposo. El autómata a diseñar debe recibir la información y presentarla en pararlelo acompañada de un bit de error cuando en la transmisión se incumplan las condiciones de transmisión. Diseña el autómata Moore que controle la transmisión. Diagrama de transición de estados 207 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.35 Un sistema de alarma tiene un detector de personas, cuando detecta una, la alarma se pone a 1, y así se queda aunque desaparezca la persona. Para parar la alarma el guarda deberá activar un pulsador de rearme, PR. En este caso la alarma volverá a 0, y así se quedará hasta que detecte una nueva persona. Diseña el autómata Moore que controle la alarma. Diagrama de transición de estados 208 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.36 Obtén el DTE del autómata capaz de controlar las duchas de entrada a una piscina: si la salida DUCHAS se pone a 1, éstas se activan, en caso contrario no. El pasillo con duchas tiene dos sensores: uno de entrada, E, y uno de salida, S. Las duchas deben activarse cuando alguien entrando desde los vestuarios se encuentre entre E y S, mientras que si la persona va desde las pisicinas al vestuario, las duchas no deberán activarse en ningún caso, aunque esté entre E y S. Considérese que nunca habrá más de una persona en el pasillo de las duchas, o sea, que todos entran y salen de uno en uno, y que nunca se mezclan en el pasillo. Diseña el autómata Moore que controle la activación de las duchas. Diagrama de transición de estados 209 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.37 Obtén el DTE capaz de controlar la única salida de una cafetera (CAF). La cafetera cuenta con un pulsador de arranque y un detector de jarra de café. Al pulsar, la cafetera se enciende y así se queda hasta que no se retire la jarra, lo que conlleverá su apagado. Además, la cafetera jamás debe funcionar en ausencia de jarra, ya que se desbordaría el café. Diseña el autómata Moore que controle la cafetera. Diagrama de transición de estados 210 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.38 Un motor es capaz de no girar (00), girar a la derecha (01) y girar a la izquierda (10). Se desea controlar las dos salidas del motor con dos entradas: un pulsador de marcha (P) y un detector de reposo. El motor se va a usar para agitar una coctelera, cuando el barman pulse P el motor dará una vuelta a la derecha hasta volver a quedar en reposo, si quisiera otra vuelta, debería volver a pulsar P, y en este caso la vuelta sería a izquierdas, asegurando una correcta agitación del cóctel. Resumiendo, al pulsar da una vuelta a la derecha hasta volver a alcanzar el reposo y detenerse, al volver a pulsar da una vuelta a la izquierda hasta volver a alcanzar el reposo y detenerse, un nuevo pulso volvería a girar la coctelera a la derecha, y así sucesivamente. Diseña el autómata Moore que controle el motor de la coctelera. Diagrama de transición de estados 211 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.39 Dibujar el DTE de un autómata capaz de detectar errores en la transmisión de un mensaje de 7 bits + 1 con bit de paridad par desde los unos. La entrada está a estado alto "1" mientras no se transmite nada (en reposo). Un bit a cero indica el comienzo de la transmisión de los 8 bits (7+1). Al acabar el mensaje, la línea vuelve a quedar en estado alto o de reposo. Diseña el autómata Moore que controle la transmisión serie. Diagrama de transición de estados 212 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.40 Dibujar el DTE de un autómata capaz de automatizar la obtención de vino tinto. Se dispone de mosto de cuatro tipos de uva, muy bueno, bueno, regular y malo, MMB, MB, MR y MM. Cada botella se llena en 8 segundos de mezcla de los diferentes mostos según la siguiente tabla: • VINO TINTO FINO: 8 segundos de MMB. • VINO TINTO BUENO: 1 segundo de MMB, 6 segundos de MB y uno de MR. • VINO TINTO DE MESA: 4 segundos de MB, 3 segundos de MR y uno de MM. • VINO TINTO NORMAL: 3 segundos de MR y cinco de MM. El reloj, CK, evoluciona a 1Hz. Diseña el autómata Moore que controle la activación de los motores de los diferentes mostos. Diagrama de transición de estados 213 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.41 Se dispone de un teclado con dos entradas ENTRA y SALE y una tecla de INICIO. Para indicar ENTRA o SALE primero se pulsa INICIO y luego se pulsa una tecla durante el tiempo que sea. Se debe generar un pulso 0-1-0 en la salida adecuada, SENTRA y SSALE. El resto del tiempo ambas salidas quedarán a 0. Además se debe excitar una salidad de ERROR cuando éste se dé. Dibujar el DTE capaz de gestionar las entradas frente a las tres salidas. Diagrama de transición de estados 214 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.42 Se dispone de tres entradas T, X e Y para obtener las salidas MXY y MYX. La primera se pone a 1 si X es mayor que Y, y viceversa para MYX. Los datos X e Y se reciben en serie y son comparados por cada bloque de dos bits. La entrada T indica si se reciben empezando por el bit de menos peso (T=0) o por el de más peso (T=1). Mientras se reciben los bits las salidas estarán a cero. NOTA: durante una tanda de bits el cambio de T no afecta. Imaginemos que queremos que la salida mantenga el valor de la anterior comparación mientras se recibe la nueva tanda de dos bits, es decir, que el resultado de la comparación se mantenga durante los dos ciclos de reloj siguientes a la recepción, que son en los que se recibe la nueva tanda, ¿puede hacerse con este autómata? ¿y con otro redefinido? ¿qué solución es válida? Diagrama de transición de estados 215 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.43 Diseña el autómata capaz de obtener la suma de dos entradas A y B que se reciben en serie empezando por el bit de menos peso. Además el sistema dispone de una entrada EM que indica con 1 cuéndo empieza la suma, cuando EM=0 la suma finaliza y la salida es 0 hasta que comienza una nueva suma con EM=1. Además de lo anterior se dispone de un registro de desplazamiento para almacenar la suma bit a bit. Añade al autómta la salida correspondiente que permita controlar el registro. Una pregunta final, ¿se podría diseñar el autómata si A y B empezarán por el bit de más peso? Diagrama de transición de estados 216 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.44 Se dispone de una entrada E cíclica cuyo nivel alto dura 1 ciclo de reloj y el bajo dura 5 ciclos de reloj. Diseña el autómata que obtiene en la salida SE, la entrada en la que 1 y 0 duran tres ciclos de reloj cada uno. Diagrama de transición de estados 217 © Universidad de Deusto - ISBN 978-84-9830-784-9 Ejercicios de sistemas digitales 8.45 • • • • • Obtén el DTE capaz de controlar el llenado de un depósito de agua. El depósito está conectado a dos bombas de agua que se activan por medio de sendas señales digitales, de tal forma que la activación de la salida “BA” pone en funcionamiento la bomba A y la activación de la salida “BB” activa la bomba B. La activación cualquiera de las 2 bombas provoca la introducción de agua en el depósito, siendo el llenado del mismo mucho más rápido cuando ambas bombas funcionan a la vez. Para la activación de las bombas, el depósito cuanta con dos pulsadores PA (encargado de la activación de la bomba A) y PB (encargado de provocar la puesta en marcha de la bomba B). Además el depósito cuenta con un sensor (SLL) que indica cuando el depósito está lleno. El funcionamiento sigue las siguientes pautas: Si el depósito está lleno ninguna bomba funciona, ocurra lo que ocurra en los pulsadores. Para activar por ejemplo la bomba A, se pulsa PA; una vez activada, así sigue aunque se suelte el pulsador, o sea, como un pulsador normal. El llenado del depósito siempre empieza con la bomba A (PA=1); si se pulsa PB antes que PA, no funciona ninguna bomba. Primero se activa la bomba A y luego si hace falta, la bomba B. Una vez que se ponen en marcha una o las dos bombas, estas no se paran hasta llenar el depósito. Debe considerarse imposible el que se pulsen los dos pulsadores a la vez. No hay más situaciones imposibles. Diagrama de transición de estados 218 © Universidad de Deusto - ISBN 978-84-9830-784-9 8. Autómatas 8.46 • • • • • Obtén el DTE que controla el funcionamiento de una alarma antirrobo con una salida ALARMA. La alarma cuenta con dos pulsadores y un sensor de movimiento: PR, SM y PP. El funcionamiento es como sigue: Para que la alarma funcione, primero debe estar armada, es decir, hay que pulsar PR. Una vez activado PR, la alarma está lista para funcionar. Si la alarma está activada y el SM detecta algún movimiento, entonces la alarama se activa. Si la alarma no está armada, entonces no sonará en ningún caso, aunque se detecte algún movimiento. Una vez que la alarma está activada así se queda hasta que se activa el pulsador PP que la para. Es decir, aunque desaparezca el movimiento, la alarma sigue activada. Una vez detenida la alarma, para que vuelva a estar disponible es necesario rearmarla, es decir, una vez detenida , esta no se activa de nuevo ante un movimiento si antes no es rearmada. Es imposible pulsar PP y PR a la vez. Todas las demás situacione son posibles. Diagrama de transición de estados 219 © Universidad de Deusto - ISBN 978-84-9830-784-9 Cerca de 200 ejercicios cubren el análisis y diseño de sistemas digitales combinacionales y secuenciales: tablas de verdad, diagramas de Veitch-Karnaugh, bloques MSI, cronogramas, autómatas, etc. Cada bloque de ejercicios viene precedido de los métodos que los resuelven. El sw educativo BOOLE-DEUSTO facilita al lector la resolución interactiva de los ejercicios y puede ser descargado en: http://paginaspersonales.deusto.es/zubia Universidad de Deusto • • • • • • • •