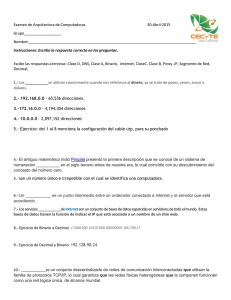

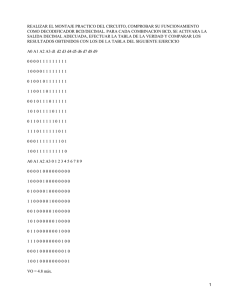

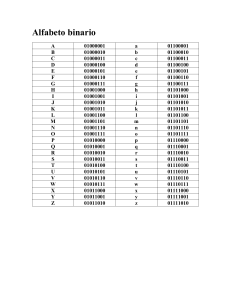

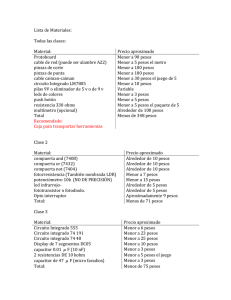

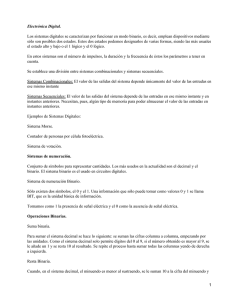

APUNTE: SISTEMAS DIGITALES ÁREA DE EET Página 1 de 44 Confeccionado por: Ricardo Muñoz Toledo Docente Inacap Derechos Reservados Titular del Derecho: INACAP N° de inscripción en el Registro de Propiedad Intelectual # ___ . ____ de fecha ___-___-___. © INACAP 2002. Página 2 de 44 ÍNDICE Sistemas Numéricos .......................................................................................................................................................... 7 Sistema decimal............................................................................................................................................................. 7 Notación posicional ....................................................................................................................................................... 7 Sistema binario .............................................................................................................................................................. 7 Conjuntos de bits ....................................................................................................................................................... 8 Dígitos más y menos significativos ........................................................................................................................... 8 Sistema hexadecimal ..................................................................................................................................................... 8 Conversión de bases ...................................................................................................................................................... 8 Conversión de un entero decimal a binario ............................................................................................................... 8 Conversión de decimal a hexadecimal ...................................................................................................................... 9 Conversión de binario a decimal ............................................................................................................................... 9 Conversión de hexadecimal a decimal ...................................................................................................................... 9 Conversión de hexadecimal a binario...................................................................................................................... 10 Conversión de binario a hexadecimal...................................................................................................................... 10 Álgebra de Boole............................................................................................................................................................. 11 Operación AND........................................................................................................................................................... 11 Operación OR.............................................................................................................................................................. 11 Complemento .............................................................................................................................................................. 11 Propiedades del álgebra de Boole................................................................................................................................ 12 Leyes y teoremas del álgebra de Boole ....................................................................................................................... 12 Compuertas lógicas ......................................................................................................................................................... 14 Compuerta YES........................................................................................................................................................... 14 Compuerta NOT .......................................................................................................................................................... 14 Compuerta AND.......................................................................................................................................................... 15 Compuerta OR............................................................................................................................................................. 16 Compuertas lógicas derivadas ......................................................................................................................................... 17 Compuerta NAND....................................................................................................................................................... 17 Compuerta NOR.......................................................................................................................................................... 17 Compuerta XOR.......................................................................................................................................................... 18 Compuerta XNOR ....................................................................................................................................................... 18 Lógica combinacional ..................................................................................................................................................... 19 OR dentro de AND...................................................................................................................................................... 19 AND dentro de OR...................................................................................................................................................... 19 NOT dentro de AND ................................................................................................................................................... 19 NOT dentro de OR ...................................................................................................................................................... 20 Compuertas lógicas comerciales ..................................................................................................................................... 20 7408 Quad 2-input AND gate................................................................................................................................. 20 4081 Quad 2-input AND gate.................................................................................................................................. 20 7432 Quad 2-input OR gate..................................................................................................................................... 20 4071 Quad 2-input OR gate..................................................................................................................................... 20 7404 Hex inverter .................................................................................................................................................... 21 4049 Hex inverter .................................................................................................................................................... 21 7400 Quad 2-input NAND gate............................................................................................................................... 21 4011 Quad 2-input NAND gate............................................................................................................................... 21 7402 Quad 2-input NOR gate.................................................................................................................................. 21 4001 Quad 2-input NOR gate.................................................................................................................................. 21 7486 Quad 2-input XOR gate.................................................................................................................................. 21 4030 Quad 2-input XOR gate.................................................................................................................................. 21 4077 Quad 2-input XOR gate.................................................................................................................................. 22 7411 Triple 3-input AND gate ................................................................................................................................ 22 Página 3 de 44 7410 Triple 3-input NAND gate.............................................................................................................................. 22 7421 Dual 4-input NAND gate................................................................................................................................ 22 4073 Quad 3-input AND gate.................................................................................................................................. 22 4078 8-input NOR gate ........................................................................................................................................... 22 4068 8-input NAND gate ........................................................................................................................................ 22 Equivalencias................................................................................................................................................................... 22 Mapas de Karnaugh......................................................................................................................................................... 24 Mapa de Karnaugh minterm de 3 variables............................................................................................................. 24 Mapa de Karnaugh minterm de 4 variables............................................................................................................. 24 Mapa de Karnaugh maxterm de 3 variables ............................................................................................................ 24 Mapa de Karnaugh maxterm de 4 variables ............................................................................................................ 24 Ejemplos de agrupaciones ....................................................................................................................................... 24 Códigos binarios.............................................................................................................................................................. 25 Código BCD ................................................................................................................................................................ 25 Conversión decimal a BCD ..................................................................................................................................... 25 Ejemplo ................................................................................................................................................................... 25 Conversión de BCD a decimal ................................................................................................................................ 25 Ejemplo ................................................................................................................................................................... 25 Código de Gray ........................................................................................................................................................... 25 Codificadores................................................................................................................................................................... 26 74147 Decimal to BCD priority encoder..................................................................................................................... 26 Decodificadores............................................................................................................................................................... 26 Decodificador básico de 2 a 4 líneas ........................................................................................................................... 26 Tabla de verdad ....................................................................................................................................................... 26 7442 BCD to decimal decoder .................................................................................................................................... 26 Tabla de verdad ....................................................................................................................................................... 26 Decodificadores BCD a 7 segmentos .............................................................................................................................. 27 Display de 7 segmentos ............................................................................................................................................... 27 4511 BCD to 7 seg decoder/driver .............................................................................................................................. 27 Tabla de verdad ....................................................................................................................................................... 27 Pines de Control ...................................................................................................................................................... 27 Decodificador para display cátodo común .................................................................................................................. 28 Cálculo de las resistencias ....................................................................................................................................... 28 7447 BDC to 7 seg decoder/driver .............................................................................................................................. 28 Terminales de Control ............................................................................................................................................. 28 Multiplexores................................................................................................................................................................... 28 Multiplexor de 4 a 1 líneas .......................................................................................................................................... 28 Tabla de funcionamiento ......................................................................................................................................... 28 Esquema equivalente al multiplexor ....................................................................................................................... 28 Cronograma de una transmisión .............................................................................................................................. 28 Demultiplexores .............................................................................................................................................................. 29 Demultiplexor de 1 a 4 líneas...................................................................................................................................... 29 Tabla de funcionamiento ......................................................................................................................................... 29 74LS138 Decodificador / Demultiplexor de 3 a 8 líneas ............................................................................................ 29 74138 Diagrama interno .......................................................................................................................................... 29 74138 Tabla de funcionamiento .............................................................................................................................. 30 74154 Decodificador / Demultiplexor......................................................................................................................... 30 Tabla de funcionamiento ......................................................................................................................................... 30 Circuitos comparadores ................................................................................................................................................... 31 7485 Comparador de magnitud de 4 bits..................................................................................................................... 31 Circuito comparador de 8 bits ..................................................................................................................................... 31 Circuitos sumadores ........................................................................................................................................................ 31 Página 4 de 44 Semisumador (Half-adder) .......................................................................................................................................... 31 Circuito lógico de un semisumador ............................................................................................................................. 31 Sumador completo (Full-adder) .................................................................................................................................. 31 Circuito sumador completo ......................................................................................................................................... 32 Circuito sumador de 4 bits........................................................................................................................................... 32 7483 4-Bit Full-adder. ................................................................................................................................................. 32 Circuito sumador de 8 bits........................................................................................................................................... 32 Circuito subtractor de 4 bits ........................................................................................................................................ 32 74181 Unidad aritmética / lógica (ALU)..................................................................................................................... 33 (Aritmetic Logic Unit)................................................................................................................................................. 33 Flip-flops ......................................................................................................................................................................... 34 Lógica combinacional y lógica secuencial .................................................................................................................. 34 Flip-flop SR NOR ....................................................................................................................................................... 34 Circuito lógico......................................................................................................................................................... 34 Símbolo lógico del flip-flop NOR........................................................................................................................... 34 Tabla de funcionamiento ......................................................................................................................................... 34 Cronograma para un flip-flop SR NOR................................................................................................................... 34 Flip-flop SR NAND .................................................................................................................................................... 34 Circuito lógico......................................................................................................................................................... 34 Símbolo lógico del flip-flop NAND........................................................................................................................ 34 Tabla de funcionamiento ......................................................................................................................................... 34 Cronograma para un flip-flop SR NAND................................................................................................................ 34 Flip-flop SR síncrono .................................................................................................................................................. 35 Circuito lógico......................................................................................................................................................... 35 Símbolo lógico ........................................................................................................................................................ 35 Tabla de funcionamiento ......................................................................................................................................... 35 Flip-flop SR síncrono con preset y clear ..................................................................................................................... 35 Circuito lógico......................................................................................................................................................... 35 Símbolo lógico ........................................................................................................................................................ 35 Tabla de funcionamiento ......................................................................................................................................... 35 Flip-flop tipo D............................................................................................................................................................ 35 Circuito lógico......................................................................................................................................................... 35 Símbolo lógico ........................................................................................................................................................ 35 Tabla de funcionamiento ......................................................................................................................................... 36 Flip-flop J-K ................................................................................................................................................................ 36 Símbolo lógico ........................................................................................................................................................ 36 Tabla de funcionamiento ......................................................................................................................................... 36 Flip-flop J-K disparado por flanco .............................................................................................................................. 36 Tabla de funcionamiento ......................................................................................................................................... 36 4027 Dual edge triggered J-K flip-flop ....................................................................................................................... 36 7476 dual edge triggered J-K flip-flop ........................................................................................................................ 36 Tabla de funcionamiento ......................................................................................................................................... 36 Contadores....................................................................................................................................................................... 37 Condensador de desacoplo .......................................................................................................................................... 38 Contadores síncronos .................................................................................................................................................. 38 Circuitos integrados contadores .................................................................................................................................. 38 4520 Doble contador binario asíncrono .................................................................................................................. 38 4040 Contador binario asíncrono ............................................................................................................................ 38 7493 Contador binario asíncrono ............................................................................................................................ 38 Contadores de décadas ................................................................................................................................................ 39 4518 Dual decade counter ....................................................................................................................................... 39 7490 Decade counter ............................................................................................................................................... 39 Página 5 de 44 Contadores conectados en cascada .............................................................................................................................. 39 Programación de contadores........................................................................................................................................ 40 EJEMPLO: .............................................................................................................................................................. 40 Contadores síncronos .................................................................................................................................................. 41 74193 Sincronous Up/Down binary counter ........................................................................................................... 41 Conexión en cascada de 2 contadores reversibles ................................................................................................... 43 Bibliografía...................................................................................................................................................................... 44 Página 6 de 44 Sistemas Numéricos Un sistema numérico consiste en un conjunto ordenado de símbolos ó guarismos empleados en la representación de números, con reglas definidas para operaciones matemáticas sobre esos símbolos, tales como la adición y la substracción. En general, una determinada cantidad, se puede expresar de la siguiente forma: N r = a n −1 a n − 2 .... a j .... a1 a0 , a −1 a − 2 .... a − m Nr = n −1 Σ aj ⋅r j j =− m Sistema decimal Un sistema numérico recibe su nombre de acuerdo a la cantidad de símbolos que se utilizan para representar una cantidad. En el caso del sistema numérico que usamos a diario, se usan diez (10) símbolos por lo que recibe el nombre sistema decimal y se dice que tiene base o rádix igual a diez (10). Los símbolos usados son: “0”, “1”, “2”, “3”, “4”, “5”, “6”, “7”, “8” y “9”. Éste sistema derivó del sistema numérico indoarábigo y posiblemente se adoptó porque contamos con diez dedos en las manos. Para diferenciar un número decimal de uno con otra base, se escribe con letras subíndices el valor de la base a la derecha del número, como ejemplo: 6810. Los números están compuestos por uno o más dígitos, que son cada uno de los símbolos usados para formar un número. Por ejemplo, el número 69 tiene dos (2) dígitos; el número 155 posee tres (3) dígitos. Notación posicional En un sistema de notación posicional, como lo es el sistema decimal, el valor representado por cada símbolo componente de un número es diferente conforme a su posición. La cantidad representada por cada símbolo depende fundamentalmente de su valor absoluto (cantidad de unidades representadas por el símbolo) y de su posición relativa a la coma que ocupa dentro de un número. Se considera posición cero como el primer dígito a la izquierda de la coma. Por ejemplo, en el sistema decimal, el símbolo 3 representa una cantidad diferente en el número 4310 que en el número 3410. En el primer caso, el número 3 se encuentra en la posición cero y representa tres (3) unidades, en cambio en el segundo caso, el número 3 se encuentra en la posición uno, donde representa treinta (30) unidades. Cabe señalar que al no existir coma, se supone como posición cero el primer dígito de la derecha. Donde: r = base. rj = factor de multiplicación del símbolo. aj = símbolo perteneciente al conjunto de símbolos del sistema. n = número de dígitos de la parte entera. m = número de dígitos de la parte fraccionaria. an-1 = dígito más significativo. a-m = dígito menos significativo. Ejemplo: 2 −1 83,2710 = Σ a j ⋅ 10 j −2 1 83,2710 = Σ a j ⋅ 10 j −2 83 ,27 10 = 7 ⋅ 10 −2 + 2 ⋅ 10 −1 + 3 ⋅ 10 0 + 8 ⋅ 10 1 Sistema binario El sistema binario es importante motivo de estudio debido a que todos los Sistemas Digitales operan únicamente con números binarios. El sistema binario tiene base igual a dos (2) y los símbolos empleados son “0” y “1”. En el lenguaje de los Sistemas Digitales cada dígito recibe la denominación de bit, que es la contracción de las palabras, del idioma inglés, binary digit (dígito binario). Para denotar un número binario, se indica con el subíndice igual a 2, como se muestra en el siguiente ejemplo: 1001012. Página 7 de 44 Conjuntos de bits Sistema hexadecimal Se utilizan con nombre propio a determinados conjuntos de dígitos en binario, los más usados son: El sistema hexadecimal tiene base igual a dieciséis (16) y sus símbolos son: “0”, “1”, “2”, “3”, “4”, “5”, “6”, “7”, “8”, “9”, “A”, “B”, “C”, “D”, “E” y “F”. Cada símbolo hexadecimal representa una cantidad equivalente en el sistema decimal de acuerdo como se muestra en la siguiente tabla: Nibble: Conjunto de cuatro bits. Esto no representaría una estructura interesante si no fuera por dos razones: El código BCD, que estudiaremos más adelante, y los números hexadecimales. Se requieren cuatro bits para representar un sólo dígito BCD ó hexadecimal. Byte: Conjunto de 8 bits y se simboliza con la letra “B”. El byte es una importante unidad de medida de cantidad de información, usada en muchas áreas relacionadas con la electrónica y comunicaciones entre otras. El byte es la unidad básica de capacidad de los medios de almacenamiento de información digital, tales como memorias, CDROM, disquetes y discos duros entre otros. Cabe señalar que en el lenguaje de Sistemas Digitales y computación, a un conjunto de 1.024 bytes se le llama kilobyte (kB), a un conjunto de 1.024 kilobytes es igual a un megabyte (MB) y un gigabyte (GB) es igual a un conjunto de 1.024 megabyte. Word: Un word (palabra) es un conjunto de 16 bits. Dword: Un Dword ó Doubleword (palabra doble) es un conjunto de 32 bits. Símbolo hexadecimal 0 1 2 3 4 5 6 7 8 9 A B C D E F Cantidad expresada en decimal 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 Conversión de bases Qword: Un Qword ó Quadword (palabra cuádruple) es un conjunto de 64 bits. Evidentemente, en muchas oportunidades tendremos la necesidad de convertir un número en su equivalente con base diferente. A continuación de detallarán las formas más usuales para convertir: Dígitos más y menos significativos Conversión de un entero decimal a binario En un número entero, se llama dígito más significativo al que posee la posición con mayor valor, mientras que el dígito menos significativo es el que se encuentra en la posición cero. En los Sistemas Digitales, no siempre se presentan los números con el dígito más significativo a la izquierda, como estamos acostumbrados a hacerlo con los números decimales. Se usan únicamente con números binarios las siglas MSB, (Most Significant Bit) para señalar el dígito más significativo y LSB (Least Significant Bit) para señalar el bit menos significativo. Ejemplo: MSB 100112 = LSB 110012 El método más usado para realizar esta conversión es el denominado como divisiones sucesivas cuyo desarrollo consiste en: 1. Dividir por 2 la parte entera del número decimal a convertir. 2. Dividir por 2 sucesivamente la parte entera del cociente de la división anterior hasta obtener cociente igual a cero (0). 3. El cociente de cada división se multiplica por 2. El resultado de cada multiplicación corresponde a un dígito del número binario, siendo el bit menos significativo el resultado de la primera multiplicación y el más significativo el de la última. Página 8 de 44 En el siguiente ejemplo, se convierte el número decimal 27 en el binario 11011(2710 → x2): La conversión de un número binario a uno decimal se realiza usando el método del polinomio ponderado, esto es que el número decimal es igual a la suma de los productos entre el valor de cada dígito binario y la potencia de 2 correspondiente a su posición. 27 : 2 = 13 , 5 0,5 · 2 = 1 13 : 2 = 6,5 0,5 · 2 = 1 6 :2= En el siguiente ejemplo se convierte a decimal el número binario 11011 (101012 → x10): 3,0 0 ·2=0 3 :2= 1,5 x10 = 101012 0,5 · 2 = 1 1 :2= x10 = 1 ⋅ 2 4 + 0 ⋅ 2 3 + 1 ⋅ 2 2 + 0 ⋅ 2 1 + 1 ⋅ 2 0 x10 = 1 ⋅ 16 + 0 + 1 ⋅ 4 + 0 + 1 ⋅ 1 0,5 0,5 · 2 = 1 1 1 0 1 1 MSB 2 LSB Conversión de decimal a hexadecimal Esta conversión se puede realizar mediante divisiones sucesivas, al igual que la conversión de decimal a binario con la diferencia que en vez de dividir por 2 y luego multiplicar por 2, se divide por 16 y luego se multiplica por 16. Los resultados de las multiplicaciones que son mayores que 9 se reemplazan por el símbolo hexadecimal correspondiente. En el siguiente ejemplo se muestra cómo convertir a hexadecimal el número decimal 698 (69810 → x16): 698 : 16 = Conversión de hexadecimal a decimal Esta conversión se realiza de un forma similar que la conversión de binario a decimal. El número decimal es igual a la suma de los productos entre el valor decimal de cada dígito hexadecimal y la potencia de 16 correspondiente a su posición. En el siguiente ejemplo se muestra como convertir el número hexadecimal 2F3 en el decimal 755 (2F316 → x10): x10 = 2 ⋅ 16 2 + 15 ⋅ 16 1 + 3 ⋅ 16 0 x10 = 2 ⋅ 256 + 15 ⋅ 16 + 3 ⋅ 1 2 , 6875 x10 = 512 + 240 + 3 0,6875 · 16 = 11 = B 2 : 16 = x10 = 16 + 4 + 1 x10 = 21 x10 = 2 F 32 43 , 625 0,625 · 16 = 10 = A 43 : 16 = Conversión de binario a decimal x10 = 755 0 , 125 0,125 · 16 = 2 2 B A 16 Página 9 de 44 Conversión de hexadecimal a binario Conversión de binario a hexadecimal Los números hexadecimales son usados en los Sistemas Digitales por la sencilla razón que basta un (1) dígito hexadecimal para representar la misma cantidad que con cuatro (4) dígitos binarios, como se muestra en la siguiente tabla: Para convertir un número binario entero en hexadecimal, primero se deben formar grupos de 4 bits a partir de la derecha hacia la izquierda y luego cada grupo se debe reemplazar por el símbolo hexadecimal equivalente de acuerdo con la tabla anterior. Si el último grupo de la izquierda no contempla 4 bits, se debe completar 4 bits agregando ceros (“0”) a la izquierda hasta completarlos. Número hexadecimal 0 1 2 3 4 5 6 7 8 9 A B C D E F Número binario 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 En el siguiente ejemplo se convierte a hexadecimal el número binario 10110010102 (10110010102 → x16): 10 1100 1010 2 0010 1100 1010 2 C A 16 Ésta característica hace que sea muy fácil convertir un número hexadecimal en binario y viceversa. Nótese que por razones prácticas, en la tabla anterior, se han representando los ceros (“0”) a la izquierda del número binario hasta completar 4 dígitos. Para convertir un número hexadecimal en binario, simplemente se debe reemplazar cada dígito hexadecimal por cuatro dígitos binarios equivalente a su símbolo de acuerdo a la tabla anterior. En el siguiente ejemplo se cómo convertir a binario el número hexadecimal C3A (C3A16 → x2): C 3 A 16 1100 0011 1010 1100 0011 1010 2 Página 10 de 44 Álgebra de Boole Operación OR Los Sistemas Digitales están compuestos por circuitos lógicos digitales que son componentes electrónicos que manipulan información binaria. Una manera de describir el comportamiento de éstos circuitos es mediante el uso de un álgebra (notación matemática) que especifica la operación de éstos. El álgebra utilizada se llama álgebra boleana ó álgebra de Boole y es una herramienta fundamental para el análisis y el diseño. La operación OR recibe su nombre de la conjunción “O”. Su símbolo en el álgebra de Boole es el de la suma del álgebra convencional (“+”) y su tabla de verdad se muestra a continuación: El álgebra de Boole es un sistema algebraico cerrado que contiene elementos que pueden asumir dos estados perfectamente diferenciados que son “0” y “1”, y tres operaciones lógicas denominadas AND, OR y complemento. Operación AND La operación AND recibe su nombre de la conjunción “Y”. Su símbolo en el álgebra de Boole es el de la multiplicación del álgebra convencional (“·”). Podríamos definir una operación mediante una tabla que exprese el resultado de la operación frente a cada posible combinación que puedan asumir los operadores. Esta tabla se denomina tabla de verdad (truth table). La siguiente tabla de verdad expresa la operación AND entre los operadores x e y: x 0 0 1 1 y 0 1 0 1 x⋅ y 0 0 0 1 Nótese en la tabla que la función x ⋅ y es igual a “1” solamente cuando la variable x es igual a “1” y la variable y es igual a “1”. x 0 0 1 1 y 0 1 0 1 x+ y 0 1 1 1 Nótese en la tabla que la función x + y es igual a “1” cuando la variable x es igual a “1” o la variable y es igual a “1”. En forma genérica, en una operación con n operadores la función OR será igual a “1” cuando uno ó más de los operadores son igual a “1”. Complemento El complemento de una variable que es igual a “0” es “1” y el de una variables que es igual a “1”, es “0”. El símbolo del complemento de una variable x es x y se lee “x negado”. El complemento de una variable x se muestra en la siguiente tabla de verdad: x x 0 1 1 0 En forma genérica, en una operación con n operadores la función AND será igual a “1” solo si todos los operadores son igual a “1”, por éste motivo a la operación AND se le llama también “todo o nada”. Página 11 de 44 Propiedades del álgebra de Boole Leyes y teoremas del álgebra de Boole El álgebra de Boole reúne diversas propiedades que nos permitirán manipular ecuaciones lógicas. A continuación se expresan las más importantes leyes y teoremas del álgebra de Boole, con sus correspondientes demostraciones : 1. Conmutatividad a) b) x+ y = y+ x. x⋅ y = y⋅ x. 1. Teorema de idempotencia a) x+ x = x . x+x = x 0+0 = 0 1+1 = 1 x 0 1 2. Distributividad a) b) x ⋅ (y + z) = x ⋅ y + x ⋅ z . x + y ⋅ z = (x + y ) ⋅ (x + z ) . b) x⋅x = x . x 0 1 3. Asociatividad x + ( y + z ) = (x + y ) + z . b) x ⋅ ( y ⋅ z ) = (x ⋅ y ) ⋅ z . x⋅ x = x x ⋅0 = 0 x ⋅1 = 1 a) 4. Identidad 2. Teorema de los elementos dominantes a) x +1 = 1. a) 0 + x = x . b) 1 ⋅ x = x . 5. Para cada elemento x del álgebra, existe un b) b) 1 = 0 . x + x = 1. b) x ⋅ x = 0 . a) 0 1 0 +1=1 1+1 = 1 x x ⋅0 0 ⋅0 = 0 1⋅ 0 = 0 0 1 0 =1. 6. Axiomas del complemento x +1 x ⋅0 = 0 . elemento denominado x (complemento), tal que: a) x 3. Ley involutiva x = x. x x x 0 1 1 0 0 1 Página 12 de 44 4. Teorema de absorción 6. Leyes de De Morgan x+ x⋅ y = x a) x 0 0 1 1 y 0 1 0 1 x⋅ y x + x⋅ y 0 0 0 1 0 0 1 1 x ⋅ (x + y ) = x b) x y x+ y 0 0 1 1 0 1 0 1 0 1 1 1 x ⋅ (x + y ) 0 0 1 1 x y x+ y x x⋅ y x+ x⋅ y 0 0 1 1 0 1 0 1 0 1 1 1 1 1 0 0 0 1 0 0 0 1 1 1 x+ y x⋅ x + y 1 1 0 1 0 0 0 1 ( ) x y x⋅ y 0 0 1 1 0 1 0 1 0 0 0 1 y x+ y x y x⋅ y x⋅ y 0 0 1 1 0 1 0 1 0 1 1 1 1 1 0 0 1 0 1 0 1 0 0 0 0 1 1 1 b) x+ x⋅ y = x+ y b) x En general: x + y + z + .... = x ⋅ y ⋅ z ⋅ .... 5. Teorema del consenso a) x+ y = x⋅ y a) x⋅ y = x + y x y x⋅ y x y x+ y x+ y 0 0 1 1 0 1 0 1 0 0 0 1 1 1 0 0 1 0 1 0 1 1 1 0 0 0 0 1 En general: x ⋅ y ⋅ z ⋅ .... = x + y + z + .... x⋅ x + y = x⋅ y x 1 1 0 0 ( ) Página 13 de 44 Compuertas lógicas La importancia del álgebra de Boole en los Sistemas Digitales es que ésta se puede asociar con los circuitos eléctricos y electrónicos que operan bajo régimen de conmutación. El elemento básico de los circuitos lógicos digitales se llama compuerta lógica (logic gate). Una compuerta lógica es un circuito electrónico que se usa para realizar una función boleana. Compuerta YES En el siguiente ejemplo, se muestra un circuito compuesto por una batería, un pulsador normalmente abierto (A) y una ampolleta (Y): 2. Cuando está conectada la ampolleta luce. Consideraremos como “1” cuando la ampolleta se encuentre bajo esta condición. Estado de la ampolleta No luce Luce Y 0 1 A partir de estas observaciones, podemos elaborar una tabla que nos exprese qué estado asumirá la ampolleta ante los posibles estados en que se pueda encontrar el interruptor: A 0 1 A Y 0 1 Éste comportamiento podemos expresarlo en el álgebra de Boole como: Y=A El símbolo usado en los circuito electrónicos digitales para esta función se muestra en la siguiente figura y se denomina compuerta YES: Y A Estableceremos que el interruptor puede asumir solamente dos estados: Y 1. Cuando el interruptor está sin pulsar, éste se encuentra abierto por lo que no conduce. Consideraremos como “0” cuando el interruptor no se encuentre sin presionar. En la figura anterior, la letra “A” denota la entrada de la compuerta y la letra “Y” denota la salida. 2. Cuando se pulsa el interruptor éste se cierra y se establece la conducción. Consideraremos como “1” cuando el interruptor se encuentre presionado. Compuerta NOT Estas dos condiciones las podríamos expresar en la siguiente tabla: Estado del interruptor Sin presionar Presionado A continuación se presenta el circuito anterior pero usando un pulsador normalmente cerrado: A A 0 1 También la ampolleta puede asumir solamente dos estados: Y 1. Cuando no está conectada la ampolleta no luce. Consideraremos como “0” cuando la ampolleta se encuentre bajo esta condición. Página 14 de 44 Continuaremos considerando que el interruptor sin presionar equivale a que la variable “A” sea igual a “0” (A=0) y cuando esté presionado la variable “A” sea igual a “1” (A=1), pero el efecto que tiene sobre “Y” es distinto. En efecto, mientras no presionemos el interruptor, la ampolleta lucirá y cuando lo presionemos, la ampolleta no lucirá. Si elaboramos una tabla de verdad ante todos los posibles combinaciones que puedan asumir los estados de las variables A y B, verificaremos que el comportamiento de este circuito es análogo a la operación Booleana AND: A 0 0 1 1 Si lo expresamos en una tabla de verdad obtendríamos: A 0 1 Y 1 0 Éste comportamiento se expresa en el álgebra de Boole como: B 0 1 0 1 Y 0 0 0 1 La expresión algebraica de ésta tabla es: Y = A⋅ B Y=A El símbolo esquemático electrónico para esta función se muestra en la siguiente figura y se denomina compuerta NOT: A El símbolo esquemático electrónico se muestra en la siguiente figura y se denomina compuerta AND: A Y Y B Compuerta AND En el siguiente circuito se encuentran dos pulsadores normalmente abiertos conectados en serie. Determinaremos cómo el comportamiento de este circuito está asociado a una operación del álgebra de Boole: La operación AND se puede realizar con 2 o más variables. Como ejemplo, se muestra el siguiente circuito, que contiene 3 contactos normalmente abiertos: A A B B C Y Y Analizando el circuito, verificaremos que la única posibilidad para lograr que luzca la ampolleta es que ambos pulsadores se encuentren presionados, es decir Y=1 cuando A=1 y B=1. Página 15 de 44 La tabla de verdad que muestra el comportamiento del circuito es: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y 0 0 0 0 0 0 0 1 La siguiente figura muestra el símbolo de la compuerta lógica AND de 3 entradas: A B C Algebraicamente expresaremos: Y = A+ B El símbolo electrónico se muestra en la siguiente figura y se denomina compuerta OR: A Y B Al igual que la operación AND, la operación OR puede tener 2 o más variables de entrada. Como ejemplo se muestra un circuito con 3 contactos normalmente abiertos en paralelo: Y A B C Compuerta OR Un circuito con interruptores normalmente abierto conectados en paralelo es equivalente a la operación OR del álgebra de Boole: A B Y En este circuito se cumple que la salida Y será igual a “1” cuando cualquiera o ambos interruptores se encuentres presionados, por lo tanto su tabla de verdad coincide con la función OR del álgebra de Boole: A 0 0 1 1 B 0 1 0 1 Y 0 1 1 1 Y La tabla de verdad que muestra el comportamiento del circuito es: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 Y 0 1 1 1 1 1 1 1 La siguiente figura muestra el símbolo de la compuerta lógica OR de 3 entradas: A B C Y Página 16 de 44 Compuertas lógicas derivadas Mientras que las tres operaciones básicas AND, OR y NOT son suficientes para llevar a cabo todas las posibles operaciones y funciones lógicas, algunas combinaciones son muy usadas, a tal grado que han recibido su propio nombre y símbolo lógico. Éstas combinaciones de compuertas son NAND, NOR, XOR y XNOR, y se detallan a continuación: El siguiente circuito lógico de contactos tiene el comportamiento de una compuerta NAND: A B Y Compuerta NAND El símbolo de la compuerta NAND se muestra en la siguiente figura: Compuerta NOR A Y El símbolo de la compuerta NOR se muestra en la siguiente figura: B La compuerta NAND tiene el comportamiento de una compuerta AND cuya salida ha sido complementada. Esto es lo que representa el círculo en el símbolo, por lo tanto una compuerta NAND es equivalente a la combinación entre una compuerta AND y una compuerta NOT, como se muestra en la siguiente figura: A A⋅ B A⋅ B B A Y B En forma análoga a la compuerta NAND, una compuerta NOR equivale a la conexión entre una compuerta OR y una compuerta NOT: A A+ B A+ B B El comportamiento de la función NAND se expresa en la siguiente tabla de verdad: A 0 0 1 1 B 0 1 0 1 Y 1 1 1 0 La expresión algebraica de la compuerta NAND es: El comportamiento de la función NOR se expresa en la siguiente tabla de verdad: A 0 0 1 1 B 0 1 0 1 Y 1 0 0 0 Y = A⋅ B Página 17 de 44 El siguiente circuito lógico de contactos tiene el comportamiento de una compuerta NOR: Compuerta XNOR A A B El comportamiento de la función XOR se expresa en la siguiente tabla de verdad: Y Compuerta XOR El símbolo esquemático de la compuerta OR exclusiva ó simplemente XOR se muestra en la siguiente figura: A 0 0 1 1 Y B El comportamiento de la función XOR se expresa en la siguiente tabla de verdad: B 0 1 0 1 Y 0 1 1 0 La siguiente figura muestra un circuito de lógica de contactos que realiza la función XOR: B 0 1 0 1 Y 1 0 0 1 XNOR equivale a la conexión entre una compuerta XOR y una compuerta NOT: A A A 0 0 1 1 Y B A⊕ B A⊕ B B La siguiente figura muestra un circuito de lógica de contactos que realiza la función XNOR: A B Y A B Y Página 18 de 44 Lógica combinacional AND dentro de OR En los circuitos de lógica combinacional, la respuesta a la salida de un circuito está en función de los estados lógicos presentes en las entrada y de la función lógica realizada. Circuito en lógica de contactos: A A continuación se muestran circuitos lógicos básicos que valen la pena reconocer para un mejor estudio de los Sistemas Digitales: C B Y OR dentro de AND Circuito en lógica de contactos: Expresión boleana: A B Y = A⋅ B + C Circuito lógico con compuertas: C A A⋅ B Y A⋅ B + C B C Expresión boleana: Tabla de verdad: Y = ( A + B) ⋅ C Circuito lógico con compuertas: A A+ B (A + B)⋅ C B C Tabla de verdad: A 0 0 0 0 1 1 1 1 B 0 0 1 1 0 0 1 1 C 0 1 0 1 0 1 0 1 A+ B ( A + B) ⋅ C 0 0 1 1 1 1 1 1 0 0 0 1 0 1 0 1 A B C A⋅ B A⋅ B + C 0 0 0 0 1 1 1 1 0 0 1 1 0 0 1 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 1 1 0 1 0 1 0 1 1 1 NOT dentro de AND Circuito en lógica de contactos: A B Y Página 19 de 44 Expresión boleana: Compuertas lógicas comerciales Y = A⋅ B 7408 Quad 2-input AND gate Circuito lógico con compuertas: A A⋅ B B B VCC=14, GND=7 Tabla de verdad: A B B A⋅ B 0 0 1 1 0 1 0 1 1 0 1 0 0 0 1 0 4081 Quad 2-input AND gate NOT dentro de OR Circuito en lógica de contactos: A VCC=14, GND=7 B 7432 Quad 2-input OR gate Y VCC=14, GND=7 Expresión boleana: Y = A+ B 4071 Quad 2-input OR gate Circuito lógico con compuertas: A A+ B B B Tabla de verdad: VCC=14, GND=7 A B B A+B 0 0 1 1 0 1 0 1 1 0 1 0 1 0 1 1 Página 20 de 44 7404 Hex inverter 7402 Quad 2-input NOR gate VCC=14, GND=7 VCC=14, GND=7 4049 Hex inverter 4001 Quad 2-input NOR gate VCC=14, GND=7 VCC=16, GND=8 7486 Quad 2-input XOR gate 7400 Quad 2-input NAND gate VCC=14, GND=7 VCC=14, GND=7 4030 Quad 2-input XOR gate 4011 Quad 2-input NAND gate VCC=14, GND=7 VCC=14, GND=7 Página 21 de 44 4077 Quad 2-input XOR gate 4078 8-input NOR gate VCC=14, GND=7 VCC=14, GND=7 7411 Triple 3-input AND gate 4068 8-input NAND gate VCC=14, GND=7 7410 Triple 3-input NAND gate VCC=14, GND=7 VCC=14, GND=7 Equivalencias Con el fin de reducir la cantidad de circuitos integrados que conforman un circuito lógico, es válido reemplazar algunas compuertas por otras que puedan cumplir la misma función. A continuación se muestran algunas equivalencias que son válidas para considerar en el diseño de circuitos lógicos digitales: 1. (A ⋅ B)⋅ C = A ⋅ B ⋅ C 2. (A + B) + C = A + B + C 3. A⋅ B ⋅ B = A⋅ B 7421 Dual 4-input NAND gate VCC=14, GND=7 4073 Quad 3-input AND gate VCC=14, GND=7 Página 22 de 44 4. A+ B+ B = A+ B VCC 12. A + 1 = A 5. 1⋅ A⋅ B = A ⋅ B VCC 6. A+ B+1= A+ B 7. 1⊕ A = A VCC 8. A⊕0 = A 9. A⋅ A = A 10. A + A = A 11. 1 ⋅ A = A Página 23 de 44 Mapa de Karnaugh maxterm de 4 variables Mapas de Karnaugh Los mapas de Karnaugh es un método gráfico para simplificar ecuaciones de forma maxterm y minterm, a partir de una tabla de verdad. C+D Mapa de Karnaugh minterm de 3 variables C C A⋅ B A⋅ B A⋅ B A⋅ B C+D C+D Ejemplos de agrupaciones Mapa de Karnaugh minterm de 4 variables C⋅D C+D A+ B A+ B A+ B A+ B C⋅D C⋅D 1 1 1 1 1 1 1 1 1 1 1 C⋅D A⋅ B A⋅ B A⋅ B A⋅ B 1 1 1 1 1 1 1 1 1 1 1 1 C A+ B A+ B A+ B A+ B 1 1 1 C 1 1 1 1 1 Mapa de Karnaugh maxterm de 3 variables 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 Página 24 de 44 Códigos binarios Ejemplo Código BCD Conviértase el siguiente número binario en su equivalente BCD: Los números BCD (Binary Coded Decimal) ó decimal codificado en binario, son ampliamente usado en los Sistemas Digitales con el fin de simplificar la conversión e interpretación de números decimales convertidos en binario y viceversa. Conversión decimal a BCD Para convertir un número decimal en BCD, se reemplaza cada dígito decimal por 4 dígitos binarios equivalentes de acuerdo a la siguiente tabla, de forma análoga a la conversión de hexadecimal a binario. Decimal 0 1 2 3 4 5 6 7 8 9 0 0 0 0 0 0 0 0 1 1 BCD 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 0 1 0 1 0 1 Nótese que en la tabla anterior, no existen los binarios 1010, 1011, 1100, 1101, 1110 y 1111. Ejemplo Conviértase el número 6910 en su equivalente BCD: 6 9 10 0110 1001 BCD Conversión de BCD a decimal La conversión de un número BCD a decimal se realiza en forma análoga a la conversión de un número binario en hexadecimal, es decir: Se forman grupos de 4 bits y luego se reemplaza cada grupo por un dígito decimal. 0001 1001 0110 1000 BCD 1 9 6 8 10 Nótese en el ejemplo, que si el grupo más significativo no completa 4 dígitos, éste se debe completar con dígitos igual a cero. Código de Gray Existen algunas situaciones dentro de los Sistemas Digitales en donde es necesario que en una cuenta binaria cambie un solo bit de estado entre números consecutivos. Esto no sucede al usar los números binarios estudiados hasta ahora. Como ejemplo, los siguientes números binarios son consecutivos pero entre uno y otro existen 3 bits que cambian de estado: 00112 a 01002. En el código de Gray entre números consecutivos cambia de estado solamente un bit a la vez, como se muestra en la siguiente tabla: 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Binario 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 Gray 0 0 0 0 0 1 0 1 1 1 1 1 1 0 1 0 1 0 1 0 1 1 1 1 0 1 0 1 0 0 0 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0 Un ejemplo de aplicación del código de Gray es en el Control de posicionamiento de máquinas ó motores, en Página 25 de 44 donde un sistema de detectores llamados encoders informan al Sistema de Control la posición de la máquina ó posición angular de un servomotor. Tabla de verdad Inputs A B L L L H H L H H Codificadores 74147 Decimal to BCD priority encoder Outputs Out1 Out2 Out3 Out4 H L L L L H L L L L H L L L L H 7442 BCD to decimal decoder Outputs Inputs 1 H X X X X X X X X L 2 H X X X X X X X L H 3 H X X X X X X L H H 4 H X X X X X L H H H 5 H X X X X L H H H H 6 H X X X L H H H H H 7 H X X L H H H H H H 8 H X L H H H H H H H 9 H L H H H H H H H H D H L L H H H H H H H C H H H L L L L H H H Decodificadores Decodificador básico de 2 a 4 líneas A Out1 B Out2 Out3 B H H H L L H H L L H A H L H L H L H L H L Tabla de verdad BCD inputs A3 A2 A1 A0 0 L L L L L L L L H H L L H L H L L H H H L H L L H L H L H H L H H L H L H H H H H L L L H H L L H H H L H L H H L H H H H H L L H H H L H H H H H L H H H H H H Decimal outputs 1 H L H H H H H H H H H H H H H H 2 H H L H H H H H H H H H H H H H 3 H H H L H H H H H H H H H H H H 4 H H H H L H H H H H H H H H H H 5 H H H H H L H H H H H H H H H H 6 H H H H H H L H H H H H H H H H 7 H H H H H H H L H H H H H H H H 8 H H H H H H H H L H H H H H H H 9 H H H H H H H H H L H H H H H H Out4 Página 26 de 44 Decodificadores BCD a 7 segmentos Tabla de verdad Display de 7 segmentos a b f g e DISPLAY CÁTODO COMÚN d c DISPLAY ÁNODO COMÚN a a b b c c d d e e f f g g COM Pines de Control COM 4511 BCD to 7 seg decoder/driver BI (Blanking Input): Cuando esta entrada es activa todos las salidas pasan a un nivel inactivo. LT (Lamp Test): Cuando esta entrada es activa, todos las salidas son activas. LE (Latch Enable): Cuando esta entrada es inactiva, en la salida permanecerá el número decodificado que estaba presente en la entrada en el instante en que LE pasara de estado activo a inactivo. Driver significa que las salidas son capaces de entregar en sus salidas suficiente corriente para encender los LEDs. Página 27 de 44 Decodificador para display cátodo común LT (Lamp Test) Cuando esta entrada se activa, todos los segmentos se encienden. RBI (Ripple Blanking Input): Entrada para conexión en cascada del Blanking Input. La utilidad consiste en no encender los display que contienen ceros a la izquierda del número. Multiplexores Multiplexor de 4 a 1 líneas A B D1 Cálculo de las resistencias + V − VD R= ID Si usamos valores prácticos como: VD=1,5V. ID=10mA. entonces: R = 100 ⋅ ( +V − 1,5 )Ω Out D2 D3 D4 Tabla de funcionamiento Entradas A B 0 0 0 1 1 0 1 1 Salidas Out D1 D2 D3 D4 Esquema equivalente al multiplexor 7447 BDC to 7 seg decoder/driver (display ánodo común) D1 D2 D3 D4 A 0 A 0 B 1 A 1 B 0 A 1 B 0 Out B 1 Cronograma de una transmisión Terminales de Control BI (Blanking Input): Cuando esta entrada está activa, todos los segmentos se apagan. Página 28 de 44 A Demultiplexores B D1 Demultiplexor de 1 a 4 líneas D2 D3 A D4 B Out D1 D D1 D2 D3 D4 D2 D3 D4 Tabla de funcionamiento Entradas A B 0 0 0 1 1 0 1 1 D1 D 0 0 0 Salidas D2 D3 0 0 D 0 0 D 0 0 D4 0 0 0 D 74LS138 Decodificador / Demultiplexor de 3 a 8 líneas 74138 Diagrama interno Página 29 de 44 74138 Tabla de funcionamiento 74154 Decodificador / Demultiplexor Tabla de funcionamiento Página 30 de 44 Circuitos comparadores Circuitos sumadores 7485 Comparador de magnitud de 4 bits Semisumador (Half-adder) Half adder A B Σ Cout Tabla de sumar 2 bits A B Cout Σ 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 0 Circuito comparador de 8 bits Σ = A⊕ B Cout = A ⋅ B Circuito lógico de un semisumador A B Σ Cout Sumador completo (Full-adder) A 0 0 0 0 1 1 1 1 Tabla de sumar 3 bits B Cin Cout 0 0 0 0 1 0 1 0 0 1 1 1 0 0 0 0 1 1 1 0 1 1 1 1 Σ 0 1 1 0 1 0 0 1 Página 31 de 44 Circuito sumador completo Circuito sumador de 8 bits Full adder Half adder Cin A B Half adder A B A B Σ Σ Cout Σ Cout Cout Full adder A B Cin Σ Cout Circuito sumador de 4 bits A3 B3 A2 B2 A1 B1 A0 B0 A B Cin A B Cin A B Cin A B FA Cout Σ Σ4 FA FA Cout Σ Σ3 HA Cout Σ Σ2 Σ1 Cout Σ Circuito subtractor de 4 bits Σ0 7483 4-Bit Full-adder. 10 8 3 1 11 7 4 16 13 A1 A2 A3 A4 Σ1 Σ2 Σ3 Σ4 9 B1 B2 B3 B4 Cout 14 6 2 15 Cin A minus B =A plus B plus C in Σ=A plus B plus Página 32 de 44 Circuito sumador/subtractor de 4 bits Control Function 0 1 A plus B A minus B 74181 Unidad aritmética / lógica (ALU) (Aritmetic Logic Unit) Página 33 de 44 Flip-flops Tabla de funcionamiento Lógica combinacional y lógica secuencial S R Q Q En los circuitos de lógica combinacional, los estados que adquieren las salidas está en función de los estados de las entradas y de la operación realizada por el circuito. Dentro de los circuitos lógicos combinacionales se encuentran los circuitos comparadores, sumadores, codificadores, decodificadores, multiplexores y demultiplexores entre otros. L L H H L H L H Qn L H L Qn En los circuitos lógicos combinacionales se cumple que para cierta combinación de estados de entrada el estado esperado en las salidas será siempre igual. En los circuitos lógicos secuenciales los estados en las salidas no solo dependen de la combinación de los estados de las entradas y de la función realizada si no que además, depende de la secuencia en que estas cambian de estado. Entonces, para una misma combinación de los estados de entrada, pueden existir diferentes estados en las salidas. Todo depende de la secuencia de cambios de los estados de las entradas. Los flip-flops son los elementos fundamentales de la lógica secuencial y son unidad básica para formar los circuitos contadores, registros y memorias. Qn y Qn son los estados de Q y Q respectivamente, antes de presentarse las condiciones indicadas. Cronograma para un flip-flop SR NOR S R Q Q Flip-flop SR NAND Circuito lógico S Flip-flop SR NOR Circuito lógico H L L Acción Memory Reset Set Indeterminada Q Q R Símbolo lógico del flip-flop NAND Tabla de funcionamiento Símbolo lógico del flip-flop NOR Acción S R Q Q L L L H Qn L Qn H H L H L Reset H H L L Memory Indeterminada Set Cronograma para un flip-flop SR NAND Página 34 de 44 Circuito lógico S PR R S Q Q CLK Q Q R CLR Flip-flop SR síncrono Este flip-flop permite conmutar las salidas solamente con la presencia de una señal de sincronismo denominada reloj ó clock (CLK). Símbolo lógico S R CLK S Q R R Q Símbolo lógico S Q CLK R Q Tabla de funcionamiento Q CLK Circuito lógico S PR CLR Q Tabla de funcionamiento CLK S R PR CLR Q Q X L L L L Qn Qn H H L L L H L H L H L L L H L X X H L H L L X X L H L H H H H X X L L X X X H H L L Flip-flop tipo D CLK S R Q Q H H L L L H Qn L Qn H H H L H L H H H L L L X X Qn Qn En el flip-flop tipo D (Data), con el flanco de la señal de sincronismo, la salida Q adquirirá el estado de la entrada D. Circuito lógico Flip-flop SR síncrono con preset y clear Este es un flip-flop SR síncrono al que se la han incorporado dos nuevas entradas asíncronas, denominadas preset (PR) y clear (CLR). Con estas nuevas entradas se puede “setear” ó “resetear” las salidas en forma independiente de la señal de sincronismo. Símbolo lógico Página 35 de 44 Tabla de funcionamiento Tabla de funcionamiento CLK D Q Q J K CLK Q Q Acción L X Qn Qn L L ↑ Qn Qn H L L H L H ↑ L H H H H L H L ↑ H L Memoria Reset Set Toggle Memoria Memoria H H ↑ Qn Qn Flip-flop J-K X X H Qn Qn Produciendo la realimentación desde las salidas hasta unas nuevas entradas en un flip-flop S-R síncrono, se puede lograr que cuando ambas entradas (set y reset) sean activas, no se produzca el estado no permitido (Q y Q . Lo que sucede bajo estas condiciones de entrada, es que las salidas adquieren los estados contrarios a los que existían antes de presentarse estas condiciones. Este modo de operar se denomina toggle. X X L Qn Qn Qn y Qn son los estados de Q y Q respectivamente, antes del flanco ascendente de la entrada CLK. 4027 Dual edge triggered J-K flip-flop En este flip-flop, la entrada set se denomina “J” y la entrada reset “K”. Símbolo lógico J Q 7476 dual edge triggered J-K flip-flop CLK K Q Tabla de funcionamiento J K CLK Q Q L L H Qn Qn L H H L H H L H H L H H H Qn Qn SD CD X X L Qn Qn L H L H H H H H L L H H H H Flip-flop J-K disparado por flanco El flip-flop J-K disparado por flanco (Edge triggered JK flip-flop) se aprovechan los retardos producidos por la propagación de las compuertas con que está constituido para cambiar los estados de las salidas solo con un flanco de la entrada de reloj. Tabla de funcionamiento J K Q Q X X X X X X h h l h h l l l H L H L H H Qn H L Qn L H Qn Qn Operación Preset Clear Indeterminada Toggle Reset Set Memoria Las letras con minúscula (l, h) indican el estado de la entrada referenciada en el instante anterior a la transición de alto a bajo de la señal de reloj. Página 36 de 44 tendremos que por cada flanco descendente de Q0, existirá solo un cambio de estado. Contadores La operación en el modo toggle del flip-flop J-K es fundamental para el funcionamiento de los circuitos denominados contadores, puesto que con esta manera de conmutar se logra “contar” en binario los impulsos del reloj y/o dividir frecuencia. En el siguiente cronograma, se muestra la conmutación en la salida Q con los flancos del reloj , cuando un flipflop J-K está en el modo toggle (nótese que la entrada de reloj es bajo activa por lo que la salida Q cambiará con los flancos descendentes de CLK). CLK Q 1 ciclo de CLK 1 ciclo de Q 2 ciclos de CLK Del cronograma anterior se puede desprender que: 1. Las conmutaciones de Q sólo se producen con el flanco descendentes de CLK. 2. El período de la señal de salida Q tiene el doble de tiempo que la señal de entrada CLK, por lo que la salida Q tiene la mitad de la frecuencia que CLK. 3. Por cada dos ciclos de CLK solo se obtiene un ciclo en la salida Q. En el siguiente circuito se han conectado dos flip-flops J-K en modo toggle y en cascada, es decir, la salida Q del primero se conecta a la entrada CLK del segundo. H J H K H J H K Q Q0 Q Q1 En la salida Q0, encontraremos que por cada flanco descendente de la señal CLK, de entrada, se producirá solo un cambio de estado. La salida Q0 es la entrada CLK del siguiente flip-flop por lo que en la salida Q1 CLK Q0 Q1 0 1 2 3 4 5 6 7 8 9 Se puede completar una tabla con los estados de las salidas en los diferentes períodos de la señal CLK: Período Entre instantes 0 y 1 Entre instantes 1 y 2 Entre instantes 2 y 3 Entre instantes 3 y 4 Entre instantes 4 y 5 Entre instantes 5 y 6 Entre instantes 6 y 7 Entre instantes 7 y 8 Entre instantes 8 y 9 Q1 L L H H L L H H L Q0 L H L H L H L H L Nótese que en cada período se presentan Q0 y Q1 como un número binario de dos bits que al siguiente período se incrementa en 1. La cuenta se incrementa hasta alcanzar el máximo con solo dos bits y luego se reinicia desde cero, indefinidamente. Esta forma de contar, donde la cuenta máxima corresponde a todas las salidas en estado alto y luego la cuenta es cero, se denomina cuenta natural. En Q0 podemos encontrar la frecuencia del reloj dividida en 2 y en Q1 está dividida por 4. Conectando varios flip-flops J-K, en modo toggle en cascada se logran los circuitos contadores, cuya cuenta máxima depende de la cantidad de flip-flops que contenga. Este tipo de contadores se denominan contadores asíncronos (ripple counters). Los contadores asíncronos, tienen limitaciones en la velocidad de operación y se caracterizan porque la salida de un flip-flop J-K sirve como señal de reloj para el siguiente. Esto produce latencias debidas a los tiempos de propagación de cada flip-flop que van en aumento en la medida que aumenta la cantidad de flipflop utilizados, haciendo que aparezcan, en algunos instantes, pulsos imprevistos (glitch) que no corresponden a la cuenta correcta. Página 37 de 44 Circuito interno equivalente de cada contador Algunos ejemplos de éstos son los TTL 7490, 7493, 74193 y los CMOS 4020, 4040 y 4518 entre otros. H J H K H J La cuenta máxima en decimal que puede alcanzar un contador se puede determinar mediante la siguiente ecuación: H K H J C10 = 2n –1 H K Donde: C10: es la cuenta máxima decimal. n: es la cantidad de flip-flops que contiene el contador. H J H K Se pueden conectar circuitos integrados contadores en cascada con el fin de obtener cuentas superiores a la que puede llegar un circuito por si solo. Condensador de desacoplo Cabe señalar que los circuitos integrados de lógica secuencial como los flip-flops, contadores, registros de desplazamientos y memorias entre otros, siempre deben llevar en paralelo a sus terminales de alimentación, un capacitor de 100nF, para desacoplar los ruidos que se puedan transmitir por los conductores de la alimentación. CLK EN Q Q0 CLR R Q1 Q CLR Q Q2 CLR Q Q3 CLR 4040 Contador binario asíncrono Contadores síncronos En los contadores síncronos, la señal de reloj se aplica simultáneamente a cada flip-flop, siendo el tiempo de propagación igual en cada salida, permitiendo frecuencias de reloj superiores a las que permiten los contadores asíncronos. 7493 Contador binario asíncrono Circuitos integrados contadores 4520 Doble contador binario asíncrono Página 38 de 44 Circuito interno equivalente H J H K H J H K H J H K H J H K 7490 Decade counter Q Q0 CLK0 CLR Q Q1 Este circuito integrado contiene un flip-flop J-K que solamente divide por 2 y otros 3 flip-flops J-K que están programados para dividir por 5. Normalmente se juntan estos con el fin de obtener un contador decimal. CLK1 MR1 CLR Q Q2 CLR MR2 Q Q3 GND=10; VCC=5. CLR Contadores conectados en cascada Contadores de décadas Los contadores de décadas (decade counters) están programados para contar, con 4 bits, una década decimal (0~9) o, que es lo mismo, una cuenta BCD. Básicamente, para ampliar la capacidad de un circuito contador, basta con conectar dos o más contadores como se muestran en las siguientes figuras: 4518 Dual decade counter Diagrama de tiempo CLK EN Q0 Q1 Q2 Q3 0 1 2 3 4 5 6 7 8 9 0 1 2 3 4 Página 39 de 44 Los terminales reset se unen para formar una señal de control reset en común. La cascada se realiza conectando el bit más significativo del primer contador, a la entrada de reloj del segundo contador. Se pueden conectar tantos contadores como se necesite, tomando en consideración que al estar conectados en cascada (ripple) se producirán mayores retardos de propagación que limitarán su funcionamiento con altas frecuencias de reloj. Para evitar los problemas mencionados anteriormente, se deben usar contadores síncronos. EJEMPLO: El siguiente contador (4040) está programado para contar hasta MSB1012 (510). La programación se realiza decodificando el numero MSB1102 (610) mediante la utilización de una compuerta AND. En la siguiente figura se muestran dos contadores BCD conectados para contar hasta el número 9910. Nótese como el bit más significativo del dígito menos significativo (LSD) es usado como entrada de reloj para el siguiente contador. Solo cuando Q2 y Q3 sean nivel alto, la salida de la compuerta será nivel alto y realizará un reset a IC1, por lo que la cuenta siguiente será cero, entonces la salida de la compuerta será nivel bajo. Esto nos dice que la salida de compuerta será nivel alto solo durante un pequeño intervalo de tiempo y que su duración depende de los tiempos de propagación de ambos circuitos integrados. En Q3 encontraremos un ciclo completo por cada 6 ciclos completos de la señal entrante de reloj. Recuerde que el CI 4518 tiene una entrada alto-activa de reloj y una entrada de habilitación que es utilizada como entrada de reloj bajo-activa. Diagrama de tiempo CLK Q1 Programación de contadores La programación de contadores es necesaria para el funcionamiento de circuitos como relojes, temporizadores y otros en donde es necesario dividir frecuencia. Q2 Q3 Cuenta 0 1 2 3 4 5 0 1 2 3 4 5 0 1 2 La idea es que la máxima cuenta del contador se diferente (siempre menor) a la cuanta máxima de acuerdo con la cantidad de flip-flops que contenga. La programación de contadores se realiza mediante la decodificación de un número con los bits de salida. Este número debe ser una unidad mayor que el de la cuenta a la que se requiere alcanzar. Página 40 de 44 Contadores síncronos 74193 Sincronous Up/Down binary counter GND=10; VCC=5. Circuito lógico Página 41 de 44 Este es un contador binario ascendente y descendente síncrono. La cuenta ascendente se produce cuando la señal de reloj (clock) es aplicada en el terminal señalado como CPU (Count Pulse Up). La cuenta es descendente cuando la señal de reloj se aplica en la entrada CPD (Count Pulse Down). Ambas entradas de sincronismo trabajan con la transición de bajo a alto de la señal de sincronismo, por lo que si es necesario mantenerlas inactivas se deben dejar en nivel bajo. La entrada MR (Master Reset) es una entrada asíncrona que limpia el contador, es decir que todas las salidas pasan a nivel bajo. La entrada PL (Parallel Load) es asíncrona y realiza la "carga paralela" es decir que el número presente en las entradas D0 a D3 es traspasado a las salidas Q0 a Q3 respectivamente. Esto se hace con el fin de poder contar a partir de un número preestablecido en las entradas D0 a D3. Las salidas TCU (Terminal Count Up) - que equivale a un carry- y TCD (Terminal Count Down)- que equivale a un borrow- se usan para la conexión en cascada. Tabla de funcionamiento Diagrama de tiempo Página 42 de 44 Conexión en cascada de 2 contadores reversibles Con la conexión que se muestra a continuación, se puede contar reversiblemente entre 010 y 25510. Si se desea contar en BCD se pueden reemplazar los circuitos integrados por el 74192 (Sincronous Reversible Decimal Counter), entonces la cuenta puede estar comprendida entre 0010 y 9910. Página 43 de 44 Bibliografía www.modelo.edu.mx/univ/virtech/prograc/cbyn01.htm www.ulbrajp.com.br/~tecnobyte/sisnum1.htm www.ing.ula.ve/~araujol/sd/clases/clases.htm www.play-hookey.com/digital/basic_gates.html Página 44 de 44