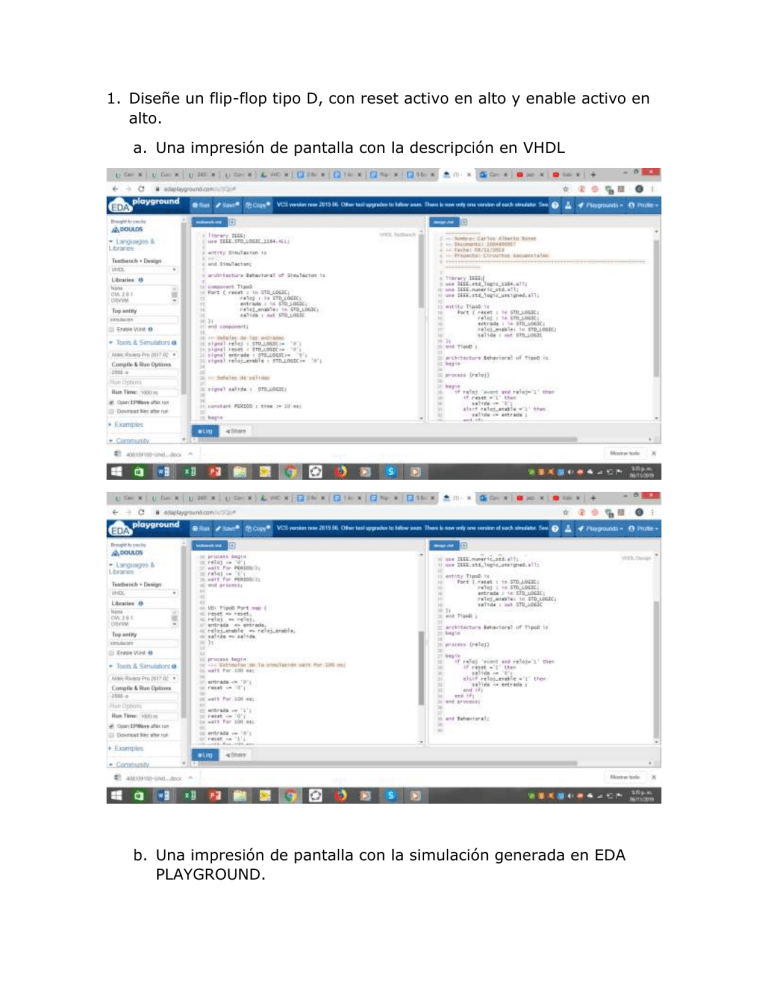

1. Diseñe un flip-flop tipo D, con reset activo en alto y enable activo en alto. a. Una impresión de pantalla con la descripción en VHDL b. Una impresión de pantalla con la simulación generada en EDA PLAYGROUND. 2. Diseñe un registro de 8 bits con reset activo en alto. a. Una impresión de pantalla con la descripción en VHDL b. Una impresión de pantalla con la simulación generada en EDA PLAYGROUND. 3. Diseñe un flip-flop tipo T con enable. a. Un diagrama de bloques. b. Una impresión de pantalla con la descripción en VHDL c. Una impresión de pantalla con la simulación generada en EDA PLAYGROUND. 4. Diseñe un contador ascendente módulo N, donde N corresponde a su edad. a. Un diagrama de bloques diseñado por el estudiante. b. Una impresión de pantalla con la descripción en VHDL c. Una impresión de pantalla con la simulación, en el cual se evidencie el correcto funcionamiento del diseño. 5. Diseñe un contador descendente módulo M, donde M es su edad. El diseño debe incluir: a. Un diagrama de bloques diseñado por el estudiante. b. Una impresión de pantalla con la descripción en VHDL c. Una impresión de pantalla con la simulación, en el cual se evidencie el correcto funcionamiento del diseño.