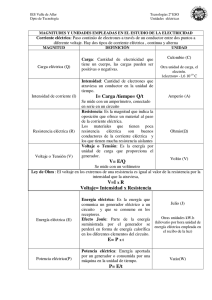

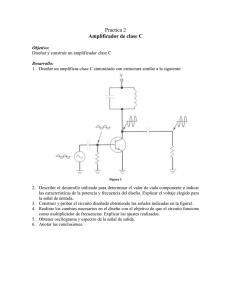

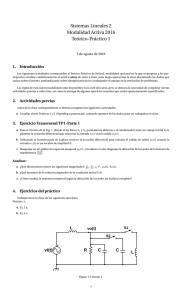

Practicas-de-Electronica-Septima-Edicion-Paul-B-Zbar-Albert-P-Malvino-Michael-A-Miller-copia

Anuncio