apuntes-sobre-los-circuitos-parte3

Anuncio

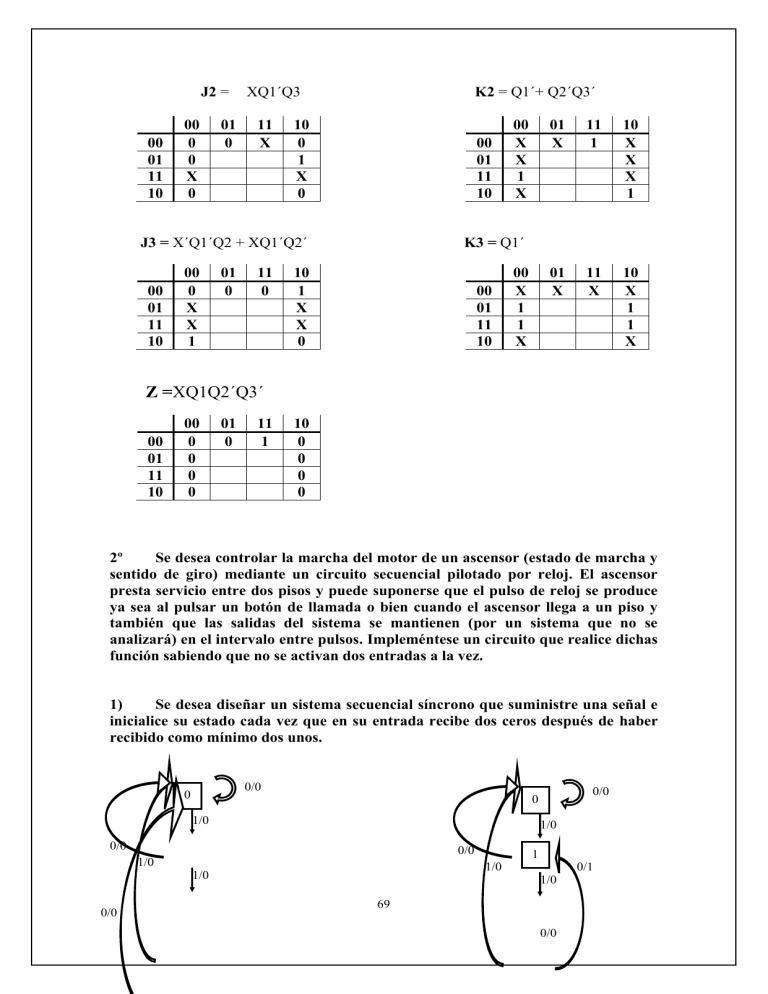

J2 = 00 01 11 10 00 0 0 X 0 01 0 XQ1´Q3 11 X K2 = Q1´+ Q2´Q3´ 10 0 1 X 0 00 01 11 10 J3 = X´Q1´Q2 + XQ1´Q2´ 00 01 11 10 00 0 X X 1 01 0 11 0 00 X X 1 X 01 X 11 1 10 X X X 1 01 X 11 X 10 X 1 1 X K3 = Q1´ 10 1 X X 0 00 01 11 10 00 X 1 1 X Z =XQ1Q2´Q3´ 00 01 11 10 00 0 0 0 0 01 0 11 1 10 0 0 0 0 2º Se desea controlar la marcha del motor de un ascensor (estado de marcha y sentido de giro) mediante un circuito secuencial pilotado por reloj. El ascensor presta servicio entre dos pisos y puede suponerse que el pulso de reloj se produce ya sea al pulsar un botón de llamada o bien cuando el ascensor llega a un piso y también que las salidas del sistema se mantienen (por un sistema que no se analizará) en el intervalo entre pulsos. Impleméntese un circuito que realice dichas función sabiendo que no se activan dos entradas a la vez. 1) Se desea diseñar un sistema secuencial síncrono que suministre una señal e inicialice su estado cada vez que en su entrada recibe dos ceros después de haber recibido como mínimo dos unos. 0/0 0 1/0 1/0 0/0 0/0 1/0 1 1/0 1/0 0/0 0/0 0 0/1 1/0 69 0/0 1 1/0 2 2 1/0 0/0 3 3 1/0 0/1 4 Después de simplificar quedaría de la siguiente manera. 0 1 Codificación de estados: 0 1 2 3 0/0 0/0 3/0 1/1 1/0 2/0 2/0 0/0 0=00 1=01 2=10 3=11 t+1 X Q1Q2 Q1Q2 J1K1 J2K2 Z 0 1 0 1 0 1 0 1 00 00 01 01 10 10 11 11 00 01 00 10 11 10 00 01 0X 0X 0X 1X X0 X0 X1 X1 0X X1 X1 X1 1X 0X X1 X0 0 0 0 0 0 0 0 1 J1 = 0 1 00 0 0 01 0 X XQ2 11 0 X K1 = 1 10 0 1 00 01 J1 =X´Q1 0 1 00 0 X 01 1 X 11 0 X 00 X X 01 X 1 11 X 1 10 X X 11 X 0 10 1 1 K1 = X´+ Q1´ 10 X X 00 01 Z =XQ1Q2 70 00 X 1 01 X 1 0 1 00 0 0 01 0 0 11 0 1 10 0 0 2) Se dispone de dos números en binario, A y B, apareciendo simultáneamente un bit de cada número, comenzando por el menos significativo, con cada pulso de reloj. Diseñar un circuito secuencial pilotado por cada pulso de reloj que vaya detectando si A>B ó A<B o A=B. El tiempo, durante el cual se realiza la comparación, está gobernado por la presencia de una señal externa, x(x=”1”). Durante el tiempo en el que x no esté presente (X=”0”) el sistema debe responder independientemente de las últimas comparaciones realizadas, para cuando vuelva a ser x=”1” comenzar una nueva comparación. Por lo que yo entiendo, se tratará de una secuencia de dos dígitos binarios que será : 0001-10-11, que por este orden también serán los estados 0, 1, 2, 3. También doy valores: A<B=01 A>B=10 A=B=00 1/1 0 0/0 1/1 1 0/0 0/0 2 1/1 0/0 3 t+1 X Q1Q2 Q1Q2 J1K1 J2K2 Z 0 1 0 1 0 1 00 00 01 01 10 10 01 00 10 01 11 10 0X 0X 1X 0X X0 X0 1X 0X X1 X0 XI 0X 0 1 0 1 0 1 71 AB 0 1 00 01 10 11 1/0 2/0 3/0 0/0 0/1 1/1 2/1 3/1 0 1 11 11 00 00 X1 X1 X1 X1 0 1 J1 = XQ1´ 0 1 00 0 1 01 X X K1 = Q2 11 X X 10 0 0 0 1 J2 =X´ 0 1 00 X X 01 0 1 11 0 1 10 X X 01 1 1 11 X 1 10 X 0 K2 = X´+`Q2 00 1 X 01 X X 11 0 X 10 0 X 01 0 0 11 1 1 10 1 1 0 1 00 X 1 Z =X 0 1 00 0 0 3) Un sistema de detección de temperatura proporciona cuatro niveles codificados en binario (00, 01, 10, 11). Se activa una alarma cuando detecta el nivel 3 11 ó cuando detecta el nivel 2 10 en 2 ciclos seguidos de reloj y debe desaparecer cuando se detecta el nivel 00 ó el nivel 01 en dos ciclos consecutivos de reloj. Implementar dicho sistema. Teniendo en cuenta que los estados de las temperaturas tendrán tres formas de evolución (subir, bajar y quedar constante) daremos valores a esas tres formas y quedan para SUBIR=11, BAJAR =00 y ESTABILIZAR=01 0 00/0 01/0 11/0 01/0 1 11 00/0 11/0 2 00/1 01/1 0 1 2 3 11/1 3 01/1 72 0/0 1/0 2/1 00 1/0 2/0 3/0 01 0/0 1/0 2/1 3/1 X Q1Q2 00 11 01 00 11 01 00 11 01 00 11 01 00 00 00 01 01 01 10 10 10 11 11 11 Q1Q2 J1K1 J2K2 01 00 00 10 01 01 11 10 10 0X 0X 0X 1X 0X X1 X0 X0 X0 1X 0X X1 X1 X0 1X 1X 0X X1 11 X0 X0 0 0 0 0 0 0 0 1 1 1 0 1 J1 =X1X2Q1´Q2 00 00 01 11 10 J2 = 0 X X K2 = X1X2Q2´+ X1´X2´Q1Q2´ 01 0 0 X X 11 0 1 10 X X1X2Q2´+ X1´X2´Q1Q2´ 00 00 01 11 10 X X 1 Z 01 0 X X 0 11 1 X X1X2 Q1Q2 00 00 01 11 10 X X 1 01 0 X X 0 11 1 X 10 1 K2 =X1X2Q1´Q2+ X1´X2´ 10 00 01 11 10 1 00 X 1 1 X 01 X 0 0 X 11 10 1 X Z= X1´Q1Q2+X2Q1Q2´ 00 01 11 10 00 0 0 1 0 01 0 0 1 1 11 0 0 0 1 10 4) Disponemos de un montacargas con pulsadores de subida S, bajada B, y paro P: para modificar el sentido de la marcha es preciso activar previamente el pulsador de parado y no responde al pulsado simultáneo de varios conmutadores. 73 Sendos topes fin de carrera Ti y Ts le impiden continuar subiendo o bajando cuando alcanza los extremos del recorridos. Implementar un autómata síncrono que controle dicho montacargas. Como en el enunciado ya dice que los pulsadores sólo pueden ser pulsados no simúltaneamente, las únicas posibles entradas pueden ser: 100 = bajar, 010 = subir, 001 = parar. Como en realidad no sé a que puedo llamar salida “1”, lo que haré será asignar como salidas “1” cuando los sensores t1 y t2 sean acticados. Los estados son los de siempre y como siempre les daremos valores: Codificación de estados: 0 0=00 1=01 2=10 3=11 001/1 100/0 010/1 001/0 1 010/0 2 En el grafo lo que haré será empezar desde el estado cero, donde el estado de salida será siempre “1”. Lo mismo pasará con el estado tres. Al estar situado en el extremo de los estados siempre su 0 salida será “1”. 0 1 2 3 100 1/0 2/0 3/1 010 0/1 1/0 2/0 3 001 0/1 1/0 2/0 3/1 Q1Q2 Q1Q2 J1K1 J2K2 Z 100 010 001 100 010 001 100 010 001 00 00 00 01 01 01 10 10 10 01 0X 1X 00 10 00 01 11 01 10 0X 1X 0X 0X X0 X1 X0 0X X1 X1 X0 1X 1X 0X 0 0 1 0 1 0 1 0 0 001/0 100/1 010/0 X 74 100/0 001/1 100 010 001 11 11 11 J1 = X1X2X3 Q1Q2 000 10 11 001 X0 X0 010 00 0X 01 0X 0X 11 X0 X0 10 X0 X1 001 010 K1 = X1X2X3 000 Q1Q2 00 100 101 110 111 101 110 111 101 110 111 0X 1X X0 011 0X 100 1X 01 X0 X1 11 X0 X1 10 0X 1X 001 010 Z= X1X2X3 000 Q1Q2 00 011 0 0 1 X1 X0 X1 1X 011 100 1 0 0 01 0 1 0 11 1 0 0 10 0 1 1 Paso de continuar que me canso ... 5) Diseñar un sistema que detecte el número de personas presentes en una sala sabiendo que existe un solo acceso que es a la vez entrada y salida y que las personas entran y salen de una en una y con una mínima distancia entre ellas. Un par de células fotoeléctricas a y b permiten detectar la salida o entrada de personas y el sentido en que cruzan dicho acceso. 6) Diseñar un circuito secuencial síncrono de una entrada que permita detectar la secuencia de información 11100. Para ello dispondrá de una salida que se pondrá a uno cuando detecte esta secuencia, momento en el cual quedará enclavada dicha salida, mientras tan sola salida permanecerá a cero. 7) Realizar un autómata síncrono con las siguientes especificaciones: el circuito debe detectar la secuencia de entradas 00-01-11-10 correspondientes a las entradas A y B, estas combinaciones sólo se tendrán en cuenta al producirse una transacción en la señal de reloj, y además sólo tiene que estar presente cada combinación durante un único impulso. Este circuito dispone de unas salida que quedará enclavada a valor 1 detectada esta combinación; En cualquier otro caso la salida será cero. 8) Realizar la síntesis del circuito lógico de control (síncrono) de un motor de acuerdo con las siguientes especificaciones: a) Si el interruptor (A) está desactivado, el circuito lógico ha de inhibir el arranque del motor. b) Si el interruptor (A) está activado: 75 Al pulsar (B) el motor debe girar a la Izd. Y seguirá girando cuando se suelte. Al pulsar el motor debe girar a la derecha y seguirá girando cuando se suelte. Si (B) Y (C) son pulsados simultáneamente, el motor girará a la izquierda. En el estado inicial, el motor se encuentra parado y no hay ninguna entrada activada. 9) Un muñeco de juguete funciona por control remoto. La caja de control posee dos pulsadores (A y B), de tal forma que, en estado de reposo, el muñeco no se mueve. Si se presiona el pulsador “A”, el muñeco se moverá hacia delante, continuando el movimiento al dejar de presionar dicho pulsador. Si se actúa sobre ambos pulsadores simultáneamente, se moverá hacia atrás, continuando así al dejar de pulsarlos. Finalmente si se pulsa “B” el muñeco se parará. Implementar el circuito como síncrono. - 10) Un circuito secuencial tiene dos entradas (x1, x2) y dos salidas (Z1,Z2). Las entradas representan un número binario natural de dos bits, N. Si el valor presente de N es mayor que el valor inmediatamente anterior, entonces, Z1 = 1. Si dicho valor es menor, entonces la salida Z2=1. En cualquier otro caso, Z1 = Z2 = 0. Se pide: a) b) Implementar el circuito como autómata de Mealy. ¿Cuántos estados tendría el circuito como autómata de Moore? 11) Información codificada en “BCD” natural es enviada en serie por una línea (x) sincronizada con los impulsos de un reloj, llegando primero el bit de mayor peso. Diseñar el circuito que genere la señal de error en el instante en que se reciba el cuarto bit cuando la combinación sea errónea, es decir que no pertenezca al código. En ese mismo momento el sistema ha de retornar al estado inicial para comenzar otro ciclo de detección de error. 12) Un circuito secuencial tiene una entrada “X” y una salida “Z”. Por “X” se transmiten pulsos positivos de 1, 2, ó 3 ciclos de duración. Desde un pulso al siguiente “X” permanece a “0” un mínimo de 10 ciclos. La salida “Z” se pondrá a 1 tras terminar el pulso de entrada y permanecerá en 1 durante 3 ciclos se el pulso de “X” duró un ciclo, durante 2 ciclos si “X” duró 2 y durante 1 ciclo si “X” duró 3. En otros casos “Z” es cero. 16) Diseñe un chequeador de paridad para caracteres de 4 bits enviados en serie. El circuito recibirá, partiendo de un estado inicial, 4 bits en serie por una línea de entrada, “X”; coincidiendo con el cuarto “bit”, la salida del circuito será 1, si y sólo si el número total de unos recibidos ha sedo par. Tras la recepción del cuarto bit, el circuito volverá a aceptar en la entrada un nuevo carácter de 4 bits. 76 1 0/0 0/0 2 1/0 0/0 1/0 3 Est. A 1 2 3 4 5 6 0/0 1/0 4 0/0 5 1/0 6 1/1 0/0 01 P. E. 1 2 1 3 4 3 1 5 1 6 4 3 01 Salida 0 0 0 0 0 0 0 0 0 1 0 0 Nos damos cuenta que el tres y el seis son iguales y por lo tanto se pueden simplificar y por ello nos deshacemos del Nº 6. 0/0 0/0 1 1/0 2 0/0 1/0 0/0 Como tenemos 5 estados, tenemos que utilizar 3 variables (A, B, C). 1/0 3 0/0 4 5 BC XA 00 01 11 10 BC XA 00 01 11 1/0 00 0X X1 X1 0X 01 0X --0X 11 0X --1X 10 0X --0X 00 1X 0X 0X 01 X1 --- 11 X1 --- 10 X0 --- BC XA 00 01 11 10 77 00 0X 0X 1X 0X 01 X0 --1X Ja = B’ X A’ Ka = 1 Jb = XC + AX Kb = C Jc = XBC Kc = 1 11 X1 --X1 10 X0 --X0 10 1X X0 X1 0X Ahora haremos por “Moore”. 000/0 0 1 100 001/0 1 0 010/0 1 0 011/0 . 1 100/0 Cronograma tipo “Moore” Clock Qa Qb Qc X Z Cronograma tipo “Mealy” Clock Qa Qb Qc Z X AUTOMATAS ASINCRONOS Comb. Mem. 78 0 101/1 a) Asícrono de realimentación directa. La función del elemento de memoria lo localizará el retablo de las puertas. Yit Xt Comb. Retar. Y1(T + At) Yit Estado estable: Y1(T + At) Yit Yit = y Y1’(t + At) Y1’(t + At) variable de estado Y1(t + At) = variable de excitación b) Asíncronos “R-S” “R-S” Comb. Pasos para la implementación de autómatas síncronos: a) b) c) d) e) f) Diseño del diagrama de fases indicando los estados estables e inestables. Tabla de funcionamiento. Simplificación Codificación de la tabla de fases. Estudio de carreras críticas Implementación 79 AUTOMATAS ASINCRONOS 1) Diseñar en sistema secuencial asíncrono con dos variables de entrada X1, X2 Y una variable de salida Z que ha de actuar según las siguientes especificaciones: a) Si la variable X1 toma el valor lógico 1, la salida Z del sistema pasa al estado lógico 1 independientemente del estado en que se encuentre y continúa en él aunque la variable X1 vuelva al estado lógico 0. Sucesivas conmutaciones de la variable X1 no cambian el estado de la salida. Si la variable X2 toma el valor lógico 1, la salida Z del sistema pasa al estado continúa en él aunque la variable X vuelva al estado lógico 0. Sucesivos cambios de X2 no modifican la salida b) X1 X2 A B C D 00 1 01 3 - 3 4 1 4 11 - 10 2 2 2 - Z 0 1 1 0 Simplificación: Se pueden simplificar aquellos líneas que tengan el mismo estado o que en una de ellos se dé la situación no existe. Al simplificar líneas, siempre predominararán los estados estables sobre los inestables. En este caso vemos con claridad que el apartado “B” y “C” se pueden simplificar. Quedaría de la siguiente manera: X1 X2 B-C A-B 00 3 1 01 4 11 - 10 2 2 Z 1 0 B-C = 0 A-B = 1 80 Interpretación: 01/0 00/1 01/0 0 0 10/1 00/0 10/1 Tabla de fases: X1 X2 0 1 00 E E 01 I E 11 - 10 E I Z 1 0 Simplificación de los mapas de “Karnaugh”: X1 X2 0 1 00 0 1 01 1 1 11 - 10 0 0 Z 1 0 Y COMB. Y X Y Y = X2 + X1’ y = X2’ o X’1y X’2 Y Y X’1 2) Un sistema secuencial asíncrono posee dos entradas de impulsos X1 y X2 (ambas entradas no pueden estar nunca en estado uno simultáneamente) y una 81 salida Z. A partir de un estado inicial en el cual X1 = X2 = Z = 0, la salida Z ha de tomar el valor uno si se aplican dos impulsos sucesivos a la entrada X1 sin que se aplique ninguno a la entrada X2. La salida volverá a cero cuando X2 pase al estado uno. Se especifica que X1 Y X2 no pueden cambiar simultáneamente. Implementa dicho sistema. Según indica el problema, las entradas son: X1 y X2 La salida: Z X1 X2 00 1 01 3 4 X1 X2 00 01 10 X1X2 Y1Y2 00 01 11 10 4 3 1 4 3 00 01 1 3 4 4 3 11 - 10 2 11 - 10 2 00 00 10 01 00 11 - 10 01 01 10 00 - 10 Y1 = X1´X2´+ X2´Y1Y2´ Y2 = X1X2´Y1´ Z 0 0 1 0 1 2 5 5 Z 0 0 1 2 5 Simplifico y doy valores X1X2 Y1Y2 00 01 11 10 00 0 1 01 0 1 0 11 10 0 0 1 Z = X1´X2´+ X2´Y1Y2 3) El producto final de una fabricación son barras metálicas cuya longitud ha de ser inferior o igual a L. Para hacer la selección del producto terminado se utiliza un sistema constituido por una cinta transportadora que hace pasar las barras entre dos detectores fotoeléctricos separados por una distancia “L” y constituidos por un emisor y un receptor de luz. La salida de los receptores de luz adopta dos niveles de tensión diferenciados según esté o no una barra situada entre él y su emisor respectivo. Se asigna por convenio el estado uno lógico a la salida cuando la barra está situada delante del detector y el estado cero en el caso contrario. Después del segundo detector existe una trampilla accionada por un motor M. Si la barra tiene una longitud mayor que L, se ha de excitar M y abrir una trampilla para dejar caer la barra. En caso contrario no ha de excitarse M. Una vez pasada 82 la barra el motor M ha de volver a desexcitarse y el sistema quedará preparado para realizar una nueva detección. La distancia que separa las dos barras sometidas a verificación es tal que nunca podrá entrar una en la zona de detección mientras se está comprobando la anterior. El problema consiste en diseñar un sistema secuencial asíncrono cuyas entradas sean las salidas de los detectores, que denominaremos X1 y X2 y cuya salida Z accione al motor M. 4) Una vía férrea con tráfico en ambos sentidos corta a una carretera en la cual se coloca una barrera gobernada por la salida Z de un autómata asíncrono. A 500 m del punto de cruce se colocan dos detectores X2 y X2 respectivamente. A partir de un estado inicial en el que Z = 0 ésta debe pasar al estado uno cuando se acerca un tren en cualquier sentido, al rebasar la máquina los 500 m del cruce y debe volver al estado cero cuando el último vagón se aleja de dicha distancia independientemente de la longitud del tren. Implementar dicho autómata. El ejercicio dice que se trata de uno sóla vía férrea que puede ser circulada en los dos sentidos. Por ese motivo las señales X1 y X2 serán las que se levante la barrera o se baje. Empezaremos por un estado inicial en el cual no han pasado trenes y por lo tanto la barrera está levantada (1). X1 X2 00 1 01 2 4 X1 X2 0 1 4 2 1 2 00 01 1 4 2 2 11 - 10 3 11 - 10 3 Z 1 0 0 3 Z 1 0 3 83 Simplificamos y damos valores Ahora lo que pasaremos a hacer es ir tomando los valores estables, primero, y los de transacción después, sus respectivas salidas y “Qt+At” que será la salida de los estados de transacción. Las salidas de estos estados serán las mismas que las de sus estados estables. X1 X2 00-1 01-2 10-3 00-4 01-2 10-3 Z 1 1 0 0 0 1 Q 1 1 0 0 0 1 Qt+1 1 1 0 0 1 0 “Q” Es siempre igual a la salida. Tomando como salidas en un instante t+1 hacemos “Karnaugh”. X2 X1 Z 00 0 1 0 1 01 1 1 11 10 0 0 Qt+1 = X´2X´1 + X´2Z 5) Antes de poner en marcha una máquina han de realizarse unas determinadas operaciones en secuencia, lo cual se detecta mediante los microinteruptores M1 y M2. Si dichas operaciones se realizan en la secuencia correcta, M2 se cerrará estando M1 abierto, pero después de haberse cerrado esta último previamente. La inhibición de la puerta en marcha de la máquina se realiza mediante la variable Z que solamente deberá activarse (adoptar el estado lógico uno) si M1 y M2 han realizado la secuencia correcta simultáneamente. M1 M2 100 001 1 = cerrado 0 = abierto 00 01 11 10 2 1 3 2 Z 0 0 00 01 11 10 00 1 9 3 2 01 5 4 3 2 84 Z 0 0 - 4 3 2 0 5 4 3 - 0 5 6 - 2 0 7 6 8 - 1 7 6 - 10 1 - 6 8 10 1 1 9 3 - 0 7 - 8 10 1 11 10 5 7 6 6 8 2 10 0 1 Simplificación Damos valores Pasamos a implementar: M1M2 Y1Y2 00 01 11 10 00 00 11 11 10 01 00 01 10 10 11 01 01 -10 M1M2 Y1Y2 10 01 01 01 10 00 01 11 10 00 0 0 0 1 01 0 0 0 1 11 0 0 -1 10 0 0 0 1 Carrera crítica Y1 = Y1 M1 + M’1 Y1 + M’1 M’2 Y2 Y2 = M1 Y´1+ Y´1 Y2+ M’2 Y2 Se asignan sus estados estables. Z = M2Y1 + Y1’ Y2 Recordemos que se trata de un circuito combinacional de entrada y otro de salida por que como nos quedaron más de una variable y por lo tanto no podemos hacer coincidir Z con Yn. 6) Diseñar un autómata que controle una puerta automática para el acceso de carros guiados a un supermercado sabiendo los siguientes datos: a) b) En el sistema existen dos finales de carrera C y A que indican si la puerta está completamente cerrada o abierta, respectivamente. En el estado inicial, la puerta está completamente cerrada. La presencia de un carro en las proximidades de la puerta es detectada por una célula. Si el carro llega a la zona de detección la puerta comienza a abrirse. Mientras haya un carro en dicha zona la puerta permanecerá abierta. Cuando el carro abandone dicha zona la puerta se cerrará, pero si la abandona antes de que la puerta esté completamente abierta, ésta se abrirá completamente y seguidamente se cerrará. Si se está cerrando y llega un carro, la puerta se abrirá. 85 Primero vamos a dar valores: Abriendo = Cerrando = Manteniendo = 11 00 01 acp 000 001 010 011 100 101 110 111 Z1 Z2 0 1 1 2 3 1 1 2 5 4 0 1 3 7 0 0 6 4 0 0 7 3 6 4 6 1 1 5 3 Si simplificamos y damos valores nos quedaría así: acp 000 001 010 011 100 101 110 111 Z1 Z2 4 0 1 00 5 3 1 2 3 0 0 01 7 6 4 3 1 1 10 5 2 6 Acp Y1Y2 000 00 01 11 10 00 01 11 10 00 01 11 10 10 01 001 010 011 100 101 00 00 10 01 00 01 01 Y1 =(A´C´P´+ A´CP)Y2´ Y2 = AC´P´Y1´+ AY1´Y2+AC´P´Y1Y2´+ C´Y1Ý2 10 00 10 01 000 001 010 011 100 101 1 I 1 1 000 001 010 011 100 101 1 1 1 1 1 Z1 = A´C´P´Y1Y2´+ A´C´PY1´Y2´+ A´CPY1Y2´+AC´P´Y1´Y2 Z2 = A´C´P´Y1Y2´+ AÝ1´Y2´A´CPY1Y2´+AC´Y1Ý2 1 EJERCICIO DE MANOLO (hecho en clase): Diseñar un circuito que realiza las siguientes transferencias de registros: 86 Si X es IMPAR A B+C Si X es PAR A B-C Visto el anunciado pasamos a desarrollar el problema paso por paso: Tomamos A, B, C Y X como registros de 8 bits y lo desarrollamos en forma de algoritmo. Inicio (carga de algorimos) X BUS DE ENTRADA A BUS DE ENTRADA B BUS DE ENTRADA C BUS DE ENTRADA If X Impar then go to Impar A B-C Go to fin Impar A B+C END Ahora pasaríamos a hacer el diagrama de bloques. A B C Búffer X S/R Entrada Salida Rst Clock Ctrl.Unit La Unidad de Control lo que hace es generar dos señales dependiendo se es “0” ó “1” (par o impar). Como salidas vamos a tener: C0 C1 C2 C3 X A B C Bus de entrada. Sumador/restador. Bus de entrada. Bus de entrada. 87 C4 C5 0/1 1 0/1 resta/suma. Búffer de imperación. So Cargar X S1 Cargar A S2 Cargar B S3 S4 S5 S3 cargaría los pares y S4 los impares (X’ = par) Estado So S1 S2 S3 S4 S5 X B C X A F Acción co, c1, c2, c3, c4, c5, BD 1 0 0 0 0 0 BD 0 0 1 0 0 0 B 0 0 0 1 0 0 AB 0 1 0 0 1 0 BC 0 1 0 0 0 0 Salida 0 0 0 0 0 1 Q2Q1Q0 X0 X0’ Est. Actual Próx. Est. 000 001 010 011 100 001 010 0 1 1/1 0 0 101 101 co, c1, c2, c3, c4, c5 1 0 0 0 0 0 0 0 1 0 0 0 0 0 0 1 0 0 0 1 0 0 1 0 0 1 0 0 0 0 88 S0 S1 S2 S3 S4 MEMORIAS DIGITALES Son sistemas que permiten el almacenamiento de información binaria durante algún tiempo. Según esto podemos estudiar: - - Memorias semiconductoras: permiten almacenamiento de información binaria utilizando semiconductores Memorias y soportes magnéticos Ferritas Memorias semiconductoras Tipos: Atendiendo a la forma de acceso a la información: - Acceso directo: Permiten el acceso a cualquier posición de memoria independientes de su situación. Acceso secuencial: en ellas para acceder a un bloque de información hay que desplazar todos aquellos bloques que se encuentren delante de este. Atendiendo a la estructura interna: Memorias de acceso aleatorio (RAM): se caracterizan por poder acceder a cualquier posición de memoria con un mismo tiempo de retardo. Dentro de estas, atendiendo a la permanencia de información (parámetro que mide la diferencia entre el tiempo necesario para leer un bloque de información menos el tiempo necesario para escribir un determinante bloque de información). TL - ---- TE Memoria activas o de lectura escritura (R/W) (volátiles): Aquí el tiempo de lectura es similar al de escritura. TL TE - Memorias pasivas: el tiempo de escritura es mucho mayor que el de lectura. dTL 89 >> TE Memoria activas o de lectura escritura (R/W) (volátiles): Atendiendo a la permanencia de la información (parámetros que miden el tiempo que permanece una información desde que se ha introducido por la entrada): Memoria SRAM: Se denominan memorias estáticas y el tiempo de permanencia de la información viene limitado exclusiva por la tensión de alimentación. Memoria DRAM: memorias dinámicas y el tiempo de permanencia de la información es de algunos milisegundos. Atendiendo a la operación de lectura/escritura: Memoria de lectura/escritura no simultánea: en estas memorias o bien leémos o bien escribimos pero no las dos cosas a la vez. Memoria de lectura/escritura simultánea: en ellas es posible leer, escribir o las dos operaciones sobre posiciones de memoria diferentes. Memoria de acceso múltiple: en ellas es posible leer, escribir o las dos operaciones sobre posiciones de memoria diferentes. Memorias pasivas Memoria ROM Son memorias en las que el tiempo de escritura es infinito. No se puede grabar en ellas. Chip-set N1 N2 Output enable Memoria programables (PROM) Son aquellas en las que el tiempo de escritura es mucho mayor que el de lectura pero admiten programarlas una vez que Te >> Tl Memorias reprogramables (RPROM) 90 EPROM tiempo de escritura >> tiempo lectura pero admiten el borrado y la posterior programación tantas veces como sean necesarias. Este tipo de memoria se borra con rayos ultravioletas. Estas se utilizan mucho más que las PROM y ROM. N2 N1 Líneas de E/S. Chip-enable Grabación de memoria: CE = 0 OE/Vp = 25 V (lo normal son 5V) QE Vp (rec.) EEPROM son similares a las EPROM pero se pueden borrar aplicando una tensión más elevada de lo habitual. N2 Escritura: N1 WE 21 V 5V M T P X Vp N2 CE WR = 0 CE = 0 0E = 0 OE = 1 memoria. OE OE Vp = 21 Borra la FLASH la diferencia con las anteriores consiste en que el borrado no se realiza posición a posición sino de forma global. Memorias de forma aleatoria para: FIFO Son memorias en las que el primer bloque de información que entran es el primero que sale. LIFO Son memorias en las que el último bloque de información que entra es el primero en salir. REGISTROS DE DESPLAZAMIENTO Memorias asociativas: 91 Organización de memorias (Vamos a estudiar las memorias RAM/activas/lectura/escritura no simultáneas). Posición de memoria 0 D E C O D I F I C A D O R M N-1 O O N-1 O N-1 R/W terminal de lectura/escritura aquí se selecciona si se lee o se escribe). Salida del decodificador para elegir la posición de memoria. Esto es lo que se llama ORGANIZACIÓN 2D Ahora vamos a ver la ORGANZACIÓN 3D 2 M/S M/S M/S D E C D E C 1 O N-1 si las dos entradas son “1”, está activo ( selección 2 M/S) 1 O N-1 O N-1 2 M/S ZM Con el primer decodificador se selecciona la posición de todas las hojas. El segundo se escoge las hojas. 92 Podemos acceder a Zm posiciones de memoria (2m/z·2m/z = 2m) Memorias dinámicas Memoria SRAM Se basan en unas células cuyo fundamento es un contador Lo que hago es regenerar cada ciertos milisegundo. Tienes que refrescar la memoria. Las memorias dinámicas se han utilizado para construir memorias de alta capacidad detectando la gran sencillez de sus células componentes. 1 Memorias de alta capacidad (gran número de vías de dirección) Direccionamos por un lado las filas y por otro las columnas. 2 n/2 Mem ni R Ras F 2 n/2 R.C. 2 n/2 Cas Para ver la forma de operación vemos un cronograma: A0/2 n/z-1 Ras Cas W 93 1 A0-N1-1 N2/ 2 N1 Ras Cas W Dá pulsos en la línea RAS. Para refrescar la memoria ponemos: CAS = 1; W=1 RAS = Idea general: X Búffer Para refrescar todas las posiciones de memoria y no sólo las columnas utilizaremos un contador y un multiplexor. 2 líneas Cont. S0-1 MTP N2/ 2 Registro N2 N2/ 2 94 N2/ 2 Modos de refresco 1) Modo rafága Primero realizo el refresco de toda la memoria (pulsos en RAS). Luego tengo un espacio de tiempo para utilizar la memoria (operación de lectura-escritura). El micro determina el tiempo que refresca la memoria o el tiempo que la utilizo. RAS 2) Modo distributivo Ciclos de refresco más pequeñas y durante más instantes puedo utilizar la memoria (refresco una pequeña posición-leo). RAS EJERCICIOS A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 A15 A14 A13 A12 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 Direcciones de memoria del primer bloque (son los que tengo que fijar). Dirección (start)........1000 (bin.) er 1 bloque de 4K 0 1 0 1 0 1 0 1 Dirección (end)..........1FFF (hexadecimal) 95 Dirección (start)........2000 (bin.) o 2 bloque de 4K Dirección (end)..........2FFF (hexadecimal) Dirección (start)........3000 (bin.) 3er bloque de 4K Dirección (end)..........3FFF (hexadecimal) Dirección (start)........4000 (bin.) o 2 bloque de 4K Dirección (end)..........4FFF (hexadecimal) A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Inicio 0 0 0 0 0 0 0 1 0 1 1 0 1 0 1 0 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X Implementación utilizando decodificadores (Decod. 3-8) Q1 A15 (Cs)´ EN Q2 A11-0 Decod. (Cs)´ DO-7 A12 A13 A14 Q3 (Cs)´ Q4 (Cs)´ A15 D Ejercicio 3 96 1000 2000 3000 4000 Fin 1FFF 2FFF 3FFF 4FFF 2kx4 8kx8 4096 11 A15 A14 A13 A12 A11 A10 A9 0 0 0 0 1 1 1 1 0 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 0 0 0 0 8k A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 4096 2k 2k 2k 2k La implementación podrá ser de dos maneras: “0” OE N EN Dec. 2-4 A14 A15 OE N D0-7 D 3-8 A11 A12 A13 OE N A13 A14 A15 OE N A11 A12 A0-10 OE N A13 A14 Ejercicio 4 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Inicio Fin 0 0 0 0 0 0 0 0 0 1 X X X X X X X X X X X X X X X X X X X X X X 0000 0800 07FF 0FFF 1 1 1 0 1 1 1 1 1 1 0 1 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X B000 E000 F000 BFFF EFFF PFFF 97 A11 A12 A13 A14 A15 A10-0 A12 A13 A14 A11-0 Ejercicio 5 40 K de memoria RAM 16 K de memoria ROM Bloques de memoria ROM: 16Kx4 = Bloques de memoria RAM: 16Kx8 = Bloques de memoria RAM: 4Kx8 = 1 bloque 16K =16K 2 bloques16K=32K 2 bloques 16K=8K-40K A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 1 1 1 0 1 0 1 1 X X X 0 0 X X X 0 1 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X Implementaremos con un decodificador 2-4 para las líneas A15 y A14. ROM ROM EN A14 A15 Dec . RAM A13-0 R EN A12 A13 A11-0 Dec . R R 98 D0-3 D0-7 D4-7 X X X X X Ejercicio 6 A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 0 0 0 0 0 0 0 0 0 1 X X X X X X X X X X X X X X X X X X X X X X 1 0 1 0 X X X X X X X X X X X X 1 1 1 1 1 1 0 1 0 1 X X X X X X X X X X X X X X X X X X X X X X “0” A12 A13 A14 A11 A12 D H 0000 0800 1000 A000 B000 E800 8000 07FF 0FFF 9FFF AFFF EFFF EFFF FFFF A10-0 A12 A11-0 A11 A12 00 01 10 11 A11-0 Ejercicio 7 Sistema microordenador con capacidad de direccionamiento de 64K, dispone de los siguientes elementos: - Pastilla 1: EPROM monitor de 2K situado en 0000-07FF Pastilla 2: EPROM monitor de 2K situado en 0800-0FFF Pastilla 3: RAM no volátil de 2K situado en 1000-17FF Pastilla 4: Datos de teclado display, situado en 1800-1FFF Pastilla 5: RAM básica de 256 bytes situado en 2000-20FF Zona libre desde la posición 2100-27FF Pastilla 6: RAM de amplicación de 256 situado en 2800-28FF Zona libre desde la posición 2900-2FFF Pastilla 7: EPROM de 4K situado en la posición 3000-3FFF Zona libre 4000-fff Implementar el mapa de memoria con un decodificador de dos chips-sets de selección y la lógica adicional necesaria. A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Inicio 99 Fin 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 1 0 0 1 0 1 0 X X X X 0 X X X X 0 X X X X 0 X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X X 0000 0800 1000 1800 2000 07FF 0FFF 17FF 1FFF 20FF 0 0 1 0 1 0 0 0 X X X X X X X X 2800 28FF 0 0 1 1 X X X X X X X X X X X X 3000 3FFF Para seleccionar decodificador A15 A14 A11 A12 A13 D 3-8 A10-0 Porque en A11 en la pastilla 7 es X = 1,0. A10 A9 A8 A10 A9 A8 F 100 T 101

![[b]COMUNICACION A 4458 22/12/2005](http://s2.studylib.es/store/data/002780163_1-5ae174279cd785ca2d9644a7d1334a68-300x300.png)

![[b]COMUNICACION A 4445. 23/11/2005](http://s2.studylib.es/store/data/002386278_1-932efd3b73c8fa4c283214c63cd11a22-300x300.png)