35 - Universidad La Salle

Anuncio

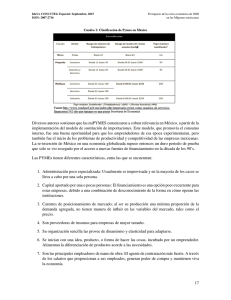

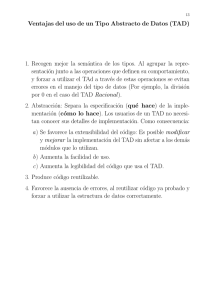

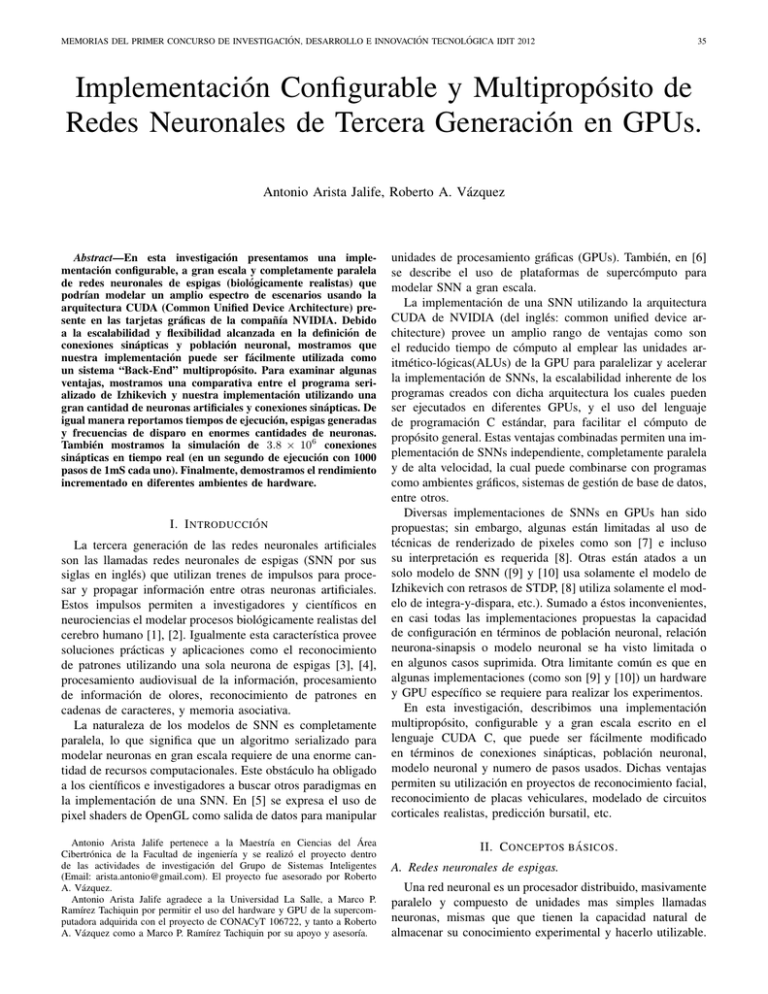

MEMORIAS DEL PRIMER CONCURSO DE INVESTIGACIÓN, DESARROLLO E INNOVACIÓN TECNOLÓGICA IDIT 2012 35 Implementación Configurable y Multipropósito de Redes Neuronales de Tercera Generación en GPUs. Antonio Arista Jalife, Roberto A. Vázquez Abstract—En esta investigación presentamos una implementación configurable, a gran escala y completamente paralela de redes neuronales de espigas (biológicamente realistas) que podrı́an modelar un amplio espectro de escenarios usando la arquitectura CUDA (Common Unified Device Architecture) presente en las tarjetas gráficas de la compañı́a NVIDIA. Debido a la escalabilidad y flexibilidad alcanzada en la definición de conexiones sinápticas y población neuronal, mostramos que nuestra implementación puede ser fácilmente utilizada como un sistema “Back-End” multipropósito. Para examinar algunas ventajas, mostramos una comparativa entre el programa serializado de Izhikevich y nuestra implementación utilizando una gran cantidad de neuronas artificiales y conexiones sinápticas. De igual manera reportamos tiempos de ejecución, espigas generadas y frecuencias de disparo en enormes cantidades de neuronas. También mostramos la simulación de 3.8 × 106 conexiones sinápticas en tiempo real (en un segundo de ejecución con 1000 pasos de 1mS cada uno). Finalmente, demostramos el rendimiento incrementado en diferentes ambientes de hardware. I. I NTRODUCCI ÓN La tercera generación de las redes neuronales artificiales son las llamadas redes neuronales de espigas (SNN por sus siglas en inglés) que utilizan trenes de impulsos para procesar y propagar información entre otras neuronas artificiales. Estos impulsos permiten a investigadores y cientı́ficos en neurociencias el modelar procesos biológicamente realistas del cerebro humano [1], [2]. Igualmente esta caracterı́stica provee soluciones prácticas y aplicaciones como el reconocimiento de patrones utilizando una sola neurona de espigas [3], [4], procesamiento audiovisual de la información, procesamiento de información de olores, reconocimiento de patrones en cadenas de caracteres, y memoria asociativa. La naturaleza de los modelos de SNN es completamente paralela, lo que significa que un algoritmo serializado para modelar neuronas en gran escala requiere de una enorme cantidad de recursos computacionales. Este obstáculo ha obligado a los cientı́ficos e investigadores a buscar otros paradigmas en la implementación de una SNN. En [5] se expresa el uso de pixel shaders de OpenGL como salida de datos para manipular Antonio Arista Jalife pertenece a la Maestrı́a en Ciencias del Área Cibertrónica de la Facultad de ingenierı́a y se realizó el proyecto dentro de las actividades de investigación del Grupo de Sistemas Inteligentes (Email: [email protected]). El proyecto fue asesorado por Roberto A. Vázquez. Antonio Arista Jalife agradece a la Universidad La Salle, a Marco P. Ramı́rez Tachiquin por permitir el uso del hardware y GPU de la supercomputadora adquirida con el proyecto de CONACyT 106722, y tanto a Roberto A. Vázquez como a Marco P. Ramı́rez Tachiquin por su apoyo y asesorı́a. unidades de procesamiento gráficas (GPUs). También, en [6] se describe el uso de plataformas de supercómputo para modelar SNN a gran escala. La implementación de una SNN utilizando la arquitectura CUDA de NVIDIA (del inglés: common unified device architecture) provee un amplio rango de ventajas como son el reducido tiempo de cómputo al emplear las unidades aritmético-lógicas(ALUs) de la GPU para paralelizar y acelerar la implementación de SNNs, la escalabilidad inherente de los programas creados con dicha arquitectura los cuales pueden ser ejecutados en diferentes GPUs, y el uso del lenguaje de programación C estándar, para facilitar el cómputo de propósito general. Estas ventajas combinadas permiten una implementación de SNNs independiente, completamente paralela y de alta velocidad, la cual puede combinarse con programas como ambientes gráficos, sistemas de gestión de base de datos, entre otros. Diversas implementaciones de SNNs en GPUs han sido propuestas; sin embargo, algunas están limitadas al uso de técnicas de renderizado de pixeles como son [7] e incluso su interpretación es requerida [8]. Otras están atados a un solo modelo de SNN ([9] y [10] usa solamente el modelo de Izhikevich con retrasos de STDP, [8] utiliza solamente el modelo de integra-y-dispara, etc.). Sumado a éstos inconvenientes, en casi todas las implementaciones propuestas la capacidad de configuración en términos de población neuronal, relación neurona-sinapsis o modelo neuronal se ha visto limitada o en algunos casos suprimida. Otra limitante común es que en algunas implementaciones (como son [9] y [10]) un hardware y GPU especı́fico se requiere para realizar los experimentos. En esta investigación, describimos una implementación multipropósito, configurable y a gran escala escrito en el lenguaje CUDA C, que puede ser fácilmente modificado en términos de conexiones sinápticas, población neuronal, modelo neuronal y numero de pasos usados. Dichas ventajas permiten su utilización en proyectos de reconocimiento facial, reconocimiento de placas vehiculares, modelado de circuitos corticales realistas, predicción bursatil, etc. II. C ONCEPTOS B ÁSICOS . A. Redes neuronales de espigas. Una red neuronal es un procesador distribuido, masivamente paralelo y compuesto de unidades mas simples llamadas neuronas, mismas que que tienen la capacidad natural de almacenar su conocimiento experimental y hacerlo utilizable. 36 MEMORIAS DEL PRIMER CONCURSO DE INVESTIGACIÓN, DESARROLLO E INNOVACIÓN TECNOLÓGICA IDIT 2012 Esta peculiar caracterı́stica le otorga a una red neuronal la habilidad de aprender y generalizar: Una red neuronal puede entregar resultados precisos sin necesidad de haber sido entrenado especı́ficamente para recibir una determinada entrada [11]. La tercera generación de las redes neuronales artificiales, son llamadas redes neuronales de espigas (SNN), las cuales introducen un nuevo concepto llamado “potencial de acción” o “espiga”: un abrupto y temporal cambio del potencial de la membrana que se propaga a través de otras neuronas[2]. Los trenes de espigas pueden ser considerados como las unidades elementales de intercambio de información entre las neuronas. El número de espigas (su tasa de disparo) y también sus tiempos son los transportadores de información, debido a que no hay diferencia entre un disparo y otro. Uno de los modelos de SNN más populares es el modelo de Izhikevich [1] que alcanza la fidelidad del modelo biológico de HodgkinHuxley y la eficiencia computacional del modelo de integray-dispara. El sistema usado de dos dimensiones de ecuaciones diferenciales ordinarias, se define como: v 0 = 0.04v 2 + 5v + 140 − u + I u0 = a {b (v − vr ) − u} ifv ≥ vpeak then v ← c, u ← u + d (1) En donde I es la corriente de entrada de la neurona (directamente inyectada dentro de ella), 0 es la d/dt, v representa el potencial de la membrana de la neurona, u representa la variable de recuperación de la membrana, a representa la escala de tiempo de la variable de recuperación u, b representa la sensibilidad de la variable de recuperación u, c representa el valor de reinicio post-disparo de la variable v, d representa el valor de reinicio post-disparo de la variable u y vpeak es el rango de disparo de la espiga de la neurona. B. Common Unified Device Architecture de NVIDIA. Gracias a la creciente demanda de gráficos de alta definición en el mercado, las unidades de procesamiento de gráficos (GPU por sus siglas en inglés) se han transformado en procesadores multinúcleo, multihilo y altamente paralelos. Para facilitar la programación en paralelo en GPUs, NVIDIA creó la arquitectura CUDA junto con algunas ampliaciones al lenguaje C estándar y un compilador. Creando ası́ un nuevo lenguaje llamado CUDA C. Estas arquitecturas y caracterı́sticas fueron desarrolladas para proveer una forma fácil y flexible de explotar el inherente paralelismo de las GPUs de NVIDIA. La arquitectura CUDA en una GPU contiene un número incrementado de ALUs. Esto permite el particionado de un algoritmo en múltiples bloques que pueden ser tratados como entidades separadas. De igual manera, dichos bloques de procesamiento pueden ser divididos en piezas más pequeñas llamadas hilos de ejecución para resolver el algoritmo en paralelo y a la vez cooperativamente. III. N UESTRA IMPLEMENTACI ÓN DE REDES NEURONALES DE ESPIGAS . Nuestra implementación consiste en dos subsistemas: un editor de conexiones sinápticas y un modelador de SNNs. El editor de conexiones sinápticas genera una topologı́a neuronal y todos los pesos sinápticos en un archivo binario. La conectividad y los pesos sinápticos pueden editarse para crear cualquier topologı́a requerida. Igualmente, el editor de conexiones sinápticas puede definir el número de sinapsis, el tamaño de la población neuronal, y los diferentes tipos de comportamiento en el modelo neuronal. El modelador de SNNs recibe una serie de parámetros contenidos en un solo archivo de configuración; gracias a esto, varios archivos pueden ser creados para modelar distintas simulaciones y escenarios. Con estos parámetros, el modelador de SNNs reserva la memoria necesaria en RAM para generar un arreglo dinámico de estructuras neuronales (structs). Ésta estructura neuronal contiene una variable de la membrana de potencial, una variable de recuperación de la membrana, un arreglo sináptico de longitud fija, una pila de bitácora de disparos de longitud fija y un apuntador auxiliar a la pila. Opcionalmente, los parámetros del modelo pueden ser guardados dentro de la estructura en lugar de almacenarse en un valor de solo lectura, estático y aplicado para todas las neuronas. Dichos valores pueden ser modificados para adaptarse a un tipo de comportamiento neuronal particular. El modelador de SNNs una vez que ya tiene reservada la memoria necesaria crea una copia del arreglo dinámico en la memoria global de la GPU. Despues de ello, cada neurona en la GPU es asignada a un hilo de ejecución y bloque de tal manera que pueda comenzar un procedimiento de simulación de tres pasos: 1) Modelo neuronal: Cada hilo aproxima la solución para su respectiva ecuación diferencial ordinaria, utilizando un vector de entrada talámica, su respectivo valor de la membrana potencial y los parámetros del modelo. 2) Evaluación neuronal: Cada hilo y bloque evalúa el valor del potencial de la membrana y determina si la neurona ha entrado en un estado de disparo, si un disparo fue generado el paso donde ocurrió el disparo es guardado en la bitácora de disparos de la neurona. Si la pila de cualquier neurona está llena, todas las pilas de las neuronas son copiadas a RAM y después sobreescritas en la GPU. 3) Cálculo de la entrada del próximo paso: Si una neurona entra en un estado de disparo, cada hilo y bloque realiza una suma vectorial paralela entre la entrada del siguiente paso y el arreglo de pesos sinápticos. Al final de la simulación todos los datos recolectados (tiempo de ejecución y las bitácoras de disparo acumuladas) son transferidos de la RAM de la GPU a RAM ordinaria y finalmente escritos en el archivo de salida correspondiente. IV. R ESULTADOS E XPERIMENTALES Realizamos un grupo de experimentos aplicando el modelo de redes neuronales de espigas de Izhikevich en nuestra implementación para realizar comparativas empleando el mismo hardware: Un procesador Intel Xeon de 8 núcleos a 2.6 GHz con 24 GB de RAM y una tarjeta gráfica NVIDIA Tesla c2050 con una RAM interna de 2687 Mbytes y 448 núcleos de ARISTA et al.: IMPLEMENTACIÓN CONFIGURABLE Y MULTIPROPÓSITO DE REDES NEURONALES 37 cantidad posible de conexiones sinápticas con mil pasos ocupando un tiempo de ejecución tan bajo como fuera posible. Los resultados en la tabla II claramente demuestran que aún una enorme cantidad de conexiones puede ser simulada en un muy bajo tiempo, permitiendo cualquier aplicación posible de redes neuronales de espigas que requieran una respuesta rápida y una enorme cantidad de neuronas simultáneamente. TABLE II R ESULTADOS DE LAS PRUEBAS DE RENDIMIENTO UTILIZANDO UN N ÚMERO VARIABLE DE NEURONAS . Fig. 1. Tiempo de ejecución promedio contra el número de neuronas y sinapsis por neurona en las implementaciones de SNN.(Menos es mejor) procesamiento CUDA a 1.15Ghz cada uno. En estos experimentos los parámetros del modelo son almacenados dentro de la estructura neuronal. A. Comparativa entre la implementación original de Izhikevich, una implementación simple en C y nuestra implementación propuesta. Desarrollamos la implementación del modelo de SNNs de Izhikevich utilizando el lenguaje C estándar sin la arquitectura CUDA para alcanzar los mismos resultados que [1]. Después mostramos una comparativa entre la implementación original de Izhikevich, la implementación del algoritmo de Izhikevich en el lenguaje C simple y nuestra propuesta en términos de tiempo de ejecución. Como se muestra en la tabla I y figura 1, en los primeros experimentos la diferencia entre cualquier implementación en términos de tiempos de ejecución es casi la misma, pero una vez que un incremento en neuronas o sinapsis por neurona es requerido nuestra implementación sobrepasa en desempeño. TABLE I T IEMPO DE EJECUCI ÓN DE LAS IMPLEMENTACIONES DE SNN S EN SEGUNDOS ( MENOS ES MEJOR ). # de Neuronas 1K 2K 3K 4K 5K 6K 7K # de Sinapsis 1K 2K 3K 4K 5K 6K 7K impl. Izhikevich 0.129 1.626 7.6902 54.845 129.4038 201.204 268.4484 impl. C 0.18 1.124 14.588 74.946 148.328 286.048 388.524 impl. Propuesta 0.698 1.998 5.584 15.752 18.126 28.078 32.76 Cada implementación usa mil pasos de 1mS cada uno, una entrada talámica aleatoria con distribución normal y parámetros neuronales aleatorios. Los resultados presentados aquı́ son el tiempo promedio de cinco ejecuciones. B. Pruebas de rendimiento: Conexiones neuronales enormes Realizamos pruebas de desempeño empleando una enorme cantidad de neuronas. Nuestro objetivo fue alcanzar la mayor # de neuronas 1K 2K 5K 10K 15K 20K 50K 75K 100K 150K 200K 225K # de conexiones 1 × 106 2 × 106 5 × 106 1 × 107 1.5 × 107 2 × 107 5 × 107 7.5 × 107 1 × 108 1.5 × 108 2 × 108 2.25 × 108 Tiempo de ejecución 0.7 1.094 1.26 2.47 3.644 4.832 12.27 19.212 25.712 39.734 54.802 64.286 Tasa de disparo 6.389 12.5166 31.217 63.1872 95.132 126.743 319.5132 478.4436 638.0754 956.4144 1277.0678 1435.3274 El número de sinapsis en este experimento es constante (1,000 por neurona). La cantidad total de conexiones es la multiplicación del número de neuronas y de sinapsis por neurona. El tiempo de ejecución y la tasa de disparos son calculadas como el valor promedio de cinco experimentos (El tiempo de ejecución está medido en segundos y la tasa de disparo = espigas generadas / numero de pasos). C. Topologı́as propuestas con simulaciones en tiempo real. Otro experimento propuesto fue la simulación de topologı́as de redes neuronales de espigas en tiempo real: la máxima cantidad de neuronas y sinapsis por neurona con la restricción de un segundo de ejecución. Se propusieron 620 configuraciones diferentes: desde 200,000 hasta 16,000,000 de conexiones en cada paso. Con una restricción de tiempo de ejecución de un segundo logramos procesar 3,800,000 conexiones simuladas por paso (equivalente a 3,800 neuronas, 1,000 sinapsis y 1,000 pasos) como se muestra en la figura 2. D. Implementación propuesta bajo diferentes condiciones y ambientes operativos. Para probar la versatilidad de nuestra implementación, aplicamos nuestra propuesta en hardware diferente. Nuestro objetivo era probar que aún en hardware notoriamente inferior nuestra implementación puede sobrepasar la velocidad de ejecución de las implementaciones originales y serializadas de Izhikevich, inclusive cuando estas últimas hayan sido ejecutadas en una supercomputadora. Los ambientes utilizados son: 1) Ambiente 1 (Supercomputadora): Intel Xeon CPU. NVIDIA Tesla c2050 GPU con una RAM de GPU interna de 2687 Mbytes y 448 núcleos CUDA a 1.15 GHz cada uno. 2) Ambiente 2 (Supercomputadora con un GPU diferente): Intel Xeon CPU. NVIDIA Quadro 4000 GPU con una 38 MEMORIAS DEL PRIMER CONCURSO DE INVESTIGACIÓN, DESARROLLO E INNOVACIÓN TECNOLÓGICA IDIT 2012 redes neuronales de espigas y aplicaciones sin el requerimiento de hardware poderoso. Obteniendo mejores resultados que una implementación en C o MATLAB en una supercomputadora. V. C ONCLUSIONES Fig. 2. Experimentación de simulaciones en tiempo real: Tiempo empleado en segundos para cada combinación de la cantidad de neuronas y sinapsis por neurona. Los resultados presentados en esta gráfica son los promedios de tres ejecuciones. En los resultados experimentales de ésta investigación hemos confirmado que nuestra implementación de SNNs supera la implementación original de Izhikevich e incluso un modelo serializado escrito en lenguaje C en términos de tiempos de ejecución y rendimiento. En otros resultados experimentales hemos probado la computabilidad de conexiones neuronales enormes en un tiempo considerablemente bajo (200,000,000 de conexiones neuronales cada paso en menos de un minuto), y conexiones con restricciones de tiempo de ejecución de un segundo para simulaciones en tiempo real (3,800,000 conexiones computadas cada mS). Finalmente, probamos nuestra implementación en diferentes ambientes de hardware y obtuvimos un incremento dramático de rendimiento. Dicho desempeño sobrepasa las demás implementaciónes aún con las desventajas de un hardware claramente inferior. Esta propuesta nos permite investigar y desarrollar a futuro en mejoras en el modelo propuesto en términos del uso de GPUs trabajando simultánea y cooperativamente, y la creación de un conjunto de aplicaciones enfocadas en la visión computacional, el reconocimiento de patrones y simulaciones biológicamente realistas de circuitos corticales. R EFERENCES Fig. 3. Comparativa entre la implementación de Izhikevich, la implementación serializada en C y todos los ambientes utilizados. RAM de GPU interna de 2048 Mbytes y 256 núcleos CUDA a 950 MHz cada uno. 3) Ambiente 3: Dell XPS 710 con Intel Core 2 Duo. NVIDIA GeForce GTX 460 SE GPU con una RAM interna de 1024 Mbytes y 288 núcleos CUDA a 1320 MHz cada uno. 4) Ambiente 4:Laptop Dell Alienware M11x R2 con Intel Core i7. NVIDIA GT 335M GPU con una RAM interna de 1024 Mbytes y 72 núcleos CUDA a 450 MHz cada uno. La figura 3 demuestra que aún en ambientes inferiores nuestra implementación sobrepasa la implementación original de Izhikevich y la implementación de C simple. Esta caracterı́stica peculiar nos permite generar implementaciones de [1] E. M. Izhikevich, “Simple model of spiking neurons,” IEEE Transactions on neural networks, vol. 14, pp. 1569–1572, 2003. [2] ——, Dynamical systems in neuroscience, ser. Neural Networks, E. M. Izhikevich, Ed. Massachusetts, United states of america: Massachusetts Institute of Technology, 2007. [3] R. A. Vazquez, “Izhikevich neuron model and its application in pattern recognition,” Australian Journal of Intelligent Information Processing Systems, vol. 11, no. 1, pp. 53–60, 2010. [4] R. A. Vazquez and A. Cachon, “Integrate and fire neurons and their application in pattern recognition,” in Electrical Engineering Computing Science and Automatic Control (CCE), 2010 7th International Conference on, sept. 2010, pp. 424 –428. [5] J.-P. Tiesel and A. S. Maida, “Using parallel gpu architecture for simulation of planar i/f networks.” Proceedings of international joint conference on neural networks, pp. 3118–3123, 2009. [6] E. Izhikevich and G. Edelman, “Large-scale model of mammalian thalamocortical systems.” Neural Networks, vol. 23, pp. 16–19, 2009. [7] F. Bernhard and R. Keriven, “Spiking neurons on gpus,” Research report 05-15, 2005. [8] J.-P. Tiesel and A. S. Maida, “Using parallel gpu architecture for simulation of planar i/f networks,” Proceedings of international joint conference on neural networks, pp. 3118–3123, 2009. [9] J. M. N. N. D. J. L. K. Nicolau and A. Veidenbaum, “Efficient simulation of large-scale spiking neural networks using cuda graphics processors,” International Joint Conference on Neural Networks, pp. 2145–2152, 2009. [10] A. K. F. E. B. R. M. P. Shanahan. and W. Luk, “Nemo: A platform for neural modelling of spiking neurons using gpus.” Application-specific Systems, Architectures and Processors., pp. 137–144, 2009. [11] S. Haykin, Neural networks and learning machines, P. Hall, Ed. Pearson education, 2009.