Sistemas en Chip acelerados por hardware: comparación de

Anuncio

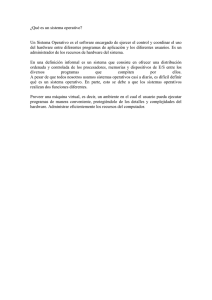

www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina Sistemas en Chip acelerados por hardware: comparación de performance en aplicaciones criptográficas Marcos J. Oviedo Pablo A. Ferreyra Carlos A. Marqués Facultad de Ingeniería Instituto Universitario Aeronáutico Córdoba, AR [email protected] Facultad de Matemática, Astronomía y Física Universidad Nacional de Córdoba Posgrado en Sistemas Embebidos Instituto Universitario Aeronáutico Córdoba, AR [email protected] Facultad de Matemática, Astronomía y Física Universidad Nacional de Córdoba Córdoba, AR [email protected] tradicionales, como el desarrollo de sistemas embebidos en un SoC de alta performance (HPSoC). Abstract— El procesamiento de datos de alta performance se ha convertido en un desafío para la tecnología de los sistemas embebidos actuales. Una alternativa para suplir los requerimientos de performance es la utilización de aceleradores de hardware implementados en lógica programable. En el presente trabajo se muestran los resultados obtenidos de dos implementaciones del algoritmo criptográfico TripleDES a través del uso de aceleradores de hardware. En un HPSoC la arquitectura de hardware esta optimizada para que la plataforma de cómputo que lo compone trabaje cooperativamente con aceleradores de hardware. En el curso de desarrollo de un HPSoC, las funcionalidades que componen al mismo son definidas primero en software, para que luego parte de las mismas sea trasladada a hardware. La implementación en hardware a través de lógica programable es una alternativa válida que se puede utilizar para lograr sustanciales incrementos en performance, teniendo en cuenta el alto nivel de paralelismo que se puede conseguir con la utilización de una plataforma de lógica programable. Keywords; Computación de Alta Performance, Sistema en Chip, Encriptación de datos Standard, Optimizaciones de Hardware, Aceleradores de Hardware. I. INTRODUCCION Avances en la industria de los semiconductores han permitido que utilizando componentes de lógica programable sea posible implementar sistemas digitales complejos. Un sistema en chip programable (SoC) es un sistema digital que en una sola pastilla de silicio, implementa un sistema embebido, dispositivos de aplicación específica y software de aplicación y control. En el presente trabajo se mostrará en forma teórica una metodología de desarrollo de un HPSoC para luego finalizar con una comparación de performance entre los resultados obtenidos de dos alternativas de implementación del algoritmo de encriptación simétrico TripleDES en un HPSoC. La implementación se realizo sobre una plataforma de lógica programable que contiene una FPGA Xilinx Virtex 4. Uno de los conceptos más poderosos atrás del diseño SoC es que la funcionalidad del sistema puede ser especificada y asignada no sólo al software que corre sobre el procesador, sino también a los componentes de hardware que lo constituyen. Permitiendo así, que para efectos de aceleración de procesamiento, sea posible implementar unidades de procesamiento de alta performance encargadas de realizar ciertos tipos de operaciones computacionales de forma óptima y por lo tanto a mayor velocidad que el procesador del sistema embebido, ayudando así a incrementar la performance del sistema. Este paper está organizado de la siguiente forma: La sección II presenta información teórica sobre las limitaciones de los sistemas basados en procesador que motivan el presente trabajo. La sección III presenta la metodología de trabajo propuesta para desarrollar este tipo de sistemas digitales. La sección IV presenta un enfoque en distintos niveles sobre las técnicas y mecanismos disponibles para incrementar la performance de un HPSoC. La sección V presenta dos implementaciones de HPSoC que proveen aceleradores criptográficos desarrollados siguiendo la metodología propuesta. La sección VI muestra y compara los resultados obtenidos. Por último, en la sección VII se muestran los resultados obtenidos y se presentan las conclusiones del presente trabajo. Debido a la creciente demanda de tecnológica de la sociedad moderna, los sistemas embebidos que componen los equipos electrónicos actuales debe ser capaces de evolucionar constantemente a modo de soportar la creciente demanda de capacidad de procesamiento a los que están sometidos. A modo de resolver esto existen alternativas a los sistemas embebidos 64 www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina II. III. LIMITACIONES DE LOS SISTEMAS BASADOS EN PROCESADOR En la metodología propuesta, el diseño de un HPSoC consistirá en dos áreas separadas pero que requieren interacción entre ellas. Una de esas áreas es la creación del soporte necesario para implementar un sistema embebido en la FPGA basado en microprocesador y la otra es la optimización de la aplicación en vistas de una posterior implementación basada en un codiseño hardware-software. En este codiseño el componente de hardware se implementara como un componente acelerador que se comunicara con el componente de software a través del diseño embebido. Los procesadores fueron concebidos para realizar computación de propósito general. Esta decisión de diseño produjo que los procesadores no sean eficientes a la hora de realizar tareas de cómputo específicas y por lo tanto, que no puedan satisfacer la performance de procesamiento que demandan algunos sistemas embebidos actuales. Persiguiendo la ley de Moore, a lo largo de los años se ha buscado alternativas para mejorar la performance de las plataformas de cómputo basadas en procesador. Sin embargo estas alternativas no han sido eficientes ni aplicables en muchos escenarios en donde la performance era un requerimiento. Como se enuncia en [1], esto se debe principalmente a que existen limitaciones físicas inherentes a los procesadores que en muchos casos y dada la tecnología actual, impiden que estas alternativas se apliquen arbitrariamente: • El hecho de aumentar la cantidad de transistores y la frecuencia a la que estos trabajan, introduce serios problemas de disipación de calor (barrera de potencia). • La frecuencia no puede ser incrementada arbitrariamente, no solo por la barrera de potencia, si no también debido a una inherente limitación física en los tiempos de conmutación de los transistores utilizados en el diseño del microprocesador (barrera de frecuencia). • En un sistema de cómputo actual, el ancho de banda del microprocesador es generalmente 70 veces superior al de la memoria externa, convirtiendo el acceso a la misma en un cuello de botella. El uso de complejas jerarquías de memorias locales al microprocesador (caches) disminuye considerablemente el tiempo de acceso a los datos, pero debido a la imposibilidad tecnológica de incrementar el tamaño del cache arbitrariamente, el acceso a memoria sigue siendo un problema real (barrera de memoria). • Finalmente los procesadores en si tienen una limitación fundamental: Un diseño basado en ejecución serial, que hace extremadamente difícil extraer niveles de paralelismo de un flujo de ejecución de instrucciones. Como se menciona en [2] existen complejos diseños y técnicas en las arquitecturas de los procesadores actuales que intentan extraer el paralelismo en las instrucciones y mitigar esta limitación. METODOLOGIA DE DESARROLLO DE UN HPSOC En primera instancia, el desarrollo de sistemas embebidos se realiza utilizando herramientas EDA que permiten interconectar, a través de una jerarquía de buses de interconexión, un microprocesador (que puede ser un softcore, o un hardcore como se menciona en [3]), con un conjunto de dispositivos que vuelven al sistema embebido una plataforma de computo funcional. El desarrollo de sistemas embebidos no es estandarizado y varía dependiendo del fabricante de FPGAs que se utilice. En el presente trabajo se utilizó FPGAs de la firma Xilinx, por lo cual se trabajo con el ecosistema de desarrollo de Xilinx para implementar el sistema embebido. Esto consistió en utilizar las herramientas EDK, ISE y las librerías de componentes de hardware XilinxProcessorIPLib. En segunda instancia, se deberá trabajar sobre la aplicación que se busca optimizar. Para esto se debe realizar un prototipo por software de la aplicación o algoritmo a implementar en el HPSoC. Este prototipo será luego caracterizado y evaluado mediante herramientas como profilers y analizadores de código, a modo de poder detectar cuales son los segmentos o áreas de la misma en donde más procesamiento se realiza (secciones críticas en términos de performance). Con esta información y a través de un enfoque top-down, se procederá a estudiar el algoritmo que define la aplicación, a modo de refactorizar la misma y que las secciones críticas puedan ser optimizadas y aisladas para ser implementadas en hardware. La implementación en hardware de las secciones críticas de la aplicación permiten que las operaciones computacionales puedan ser representadas en lenguajes de descripción de hardware y que a través de una estrategia de optimización por niveles, se puedan implementar componentes aceleradores de hardware, es decir hardware de procesamiento especifico que permita realizar computo altamente performante y eficiente. Para el desarrollo del componente acelerador se puede utilizar un lenguaje de descripción de hardware como VHDL o utilizar una herramienta ESL como ImpulseC [4]. El componente acelerador además, deberá integrarse dentro del diseño embebido del HPSoC, por lo que un canal de comunicación de alta velocidad entre hardware y software deberá también ser desarrollado. La utilización de lógica programable y la realización de un HPSoC es una valida alternativa para lograr sustanciales incrementos en performance en sistemas donde la performance es el principal requerimiento. En el presente trabajo se demostrara la implementación de un HPSoC que permitirá crear una plataforma de computo especifica y orientada a la aplicación, a modo de optimizar el camino de ejecución de datos (a través de extraer e implementar paralelismo), optimizar el uso de la memoria (aumento la localidad y el acceso), disminuir la disipación de potencia (hardware especifico requiere menor número de transistores) y disminuir la frecuencia de trabajo (posible debido a que en cada ciclo de reloj se realizan múltiples operaciones). Por otro lado, cabe mencionar que el componente de software del codiseño HW/SW puede correr directamente sobre el procesador o bajo el control y soporte de un sistema operativo (como una aplicación más de espacio de usuario). Dado los beneficios que provee un sistema operativo, en nuestra metodología se brinda soporte de un sistema operativo para el componente de software. 65 www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina detalles de bajo nivel que definen la implementación del mismo. Entonces, si posibles paralelizaciones son detectadas, y siempre cumpliendo con los requerimientos funcionales iniciales, se buscara implementar las modificaciones necesarias en el código del algoritmo, de modo de que este deje de lado su flujo de ejecución serial y adopte un modelo de funcionamiento en paralelo. Una vez que estas dos instancias del HPSoC estén completas, el diseño de hardware tiene que ser trasladado y mapeado en el fabric de una FPGA, y las imágenes binarias del software correspondiente tienen que ser almacenadas en las memorias correspondientes para su posterior evaluación. IV. OPTIMIZACION DE PERFORMANCE EN UN DISEÑO HPSOC Además de detectar niveles de paralelización y optimizaciones en el flujo de ejecución del algoritmo, otra interesante técnica que se puede utilizar para optimizar la performance a nivel de aplicación es el uso de precomputo de datos. Esto consiste básicamente en acotar el rango de acción del algoritmo, tomando asumpciones sobre el espacio de trabajo del algoritmo, a modo de precomputar y simplificar sus operaciones y de ese modo acelerar la ejecución del mismo. Existen diversos factores que pueden ser modificados y técnicas que pueden ser aplicadas en la arquitectura de un HPSoC a modo de incrementar la performance general del mismo. Estos factores pueden ser agrupados en tres áreas a las que llamaremos niveles de optimización. A. Optimizaciones a nivel de Sistema Describimos como sistema a la plataforma física en donde se implementa la aplicación. Las optimizaciones a nivel de sistema están ligadas a la forma en que se pueden implementar las aplicaciones en esta plataforma, y las modificaciones que pueden ser realizadas en la misma para que estas se ejecuten más rápido y para que el throughput sea más elevado. C. Optimizaciones a nivel de micro arquitectura Describimos como micro arquitectura a los componentes de lógica programable que implementan los detalles de bajo nivel del algoritmo que define la aplicación que se ejecutara sobre el HPSoC. Algunas técnicas para mejorar la performance de la micro arquitectura del componente acelerador son las siguientes. La optimización trivial es modificar el diseño de hardware que compone la plataforma de cómputo para que los diversos componentes de esta funcionen a la máxima velocidad admisible. Además, es óptimo establecer canales de comunicaciones de alta velocidad entre los componentes de uso frecuente por el procesador, por ejemplo los bancos de memorias o la comunicación con el fabric de la FPGA. El uso de caches de memorias (preferentemente memoria RAM en bloque) puede aumentar la localidad de datos y así mejorar la performance. 1) Replicar los arrays o bancos de memoria que contienen los datos: Una de las ventajas más importantes que nos ofrece la programación en hardware es la posibilidad de acceder a múltiples bancos de memoria en un solo ciclo de reloj. A diferencia de una implementación de software, en la que un CPU esta conectado a uno o mas dispositivos de memoria física siempre a través de un solo bus, una implementación en hardware permite la flexibilidad de generar una topología de conexionado arbitraria, en la que un conjunto de operaciones al ser ejecutadas puedan acceder a datos distribuidos en varios bancos de memoria en una sola operación de reloj. Es por esto que un factor importante a tener en cuenta, es que para lograr resultados óptimos debemos replicar nuestro set de datos en diferentes bancos de memoria. Con esto lograremos tener bancos de memoria separados, cada uno con su puerto de lectura/escritura, lo que permitirá acceder a los mismos en forma paralela para su posterior operación/procesamiento. Así mismo, las herramientas de síntesis que sintetizan el diseño de hardware permiten configurar restricciones de tiempo y aumentar el nivel esfuerzo, a modo de mejorar el rendimiento disminuyendo el tiempo de propagación de datos a través del hardware. Por otra parte, a nivel de sistema se puede paralelizar el procesamiento de datos a nivel de componente acelerador. Siempre que el algoritmo a procesar lo permita, es decir que el algoritmo de procesamiento trabaje con un conjunto de datos independiente unos de otros, y que además exista disponibilidad de recursos en la FPGA utilizada, se puede implementar más de un componente acelerador y procesar así varios conjuntos de datos en paralelo. 2) Operaciones sobre bucles: En un algoritmo, los bucles son una de las construcciones que contienen un alto grado de paralelismo inherente, y por lo tanto, son una de las construcciones que se apunta a optimizar. Los bucles generalmente realizan operaciones repetitivas sobre un set de datos. Si cada de las operaciones del bucle no depende de datos calculados en interacciones anteriores, es decir si en cada iteración se puede operar sobre set de datos independientes, el grado de paralelismo que se puede obtener es elevado. Existen dos técnicas para optimizar las operaciones sobre bucles, estas son el desenrollado del bucle y la generación de “líneas de ensamblado”, o mas conocido por su término en ingles, pipelines. El desenrrollado de bucles consiste en expandir el conjunto de iteraciones consideradas por el bucle y reacomodar el algoritmo para que estas puedan B. Optimizaciones a nivel de aplicación Describimos como aplicación al algoritmo computacional que cumple un cierto número de requerimientos con el fin de implementar por software o hardware la funcionalidad principal del HPSoC. El objetivo de las optimizaciones a nivel de aplicación es estudiar el algoritmo que define las operaciones críticas en performance de la aplicación, a modo detectar el paralelismo inherente en el mismo y optimizar el procesamiento. Cabe aclarar que las optimizaciones sobre el algoritmo se harán sobre los detalles de alto nivel del mismo, y no sobre los 66 www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina componentes necesarios para volver al sistema embebido y su procesador una plataforma de computo funcional. Además la herramienta permitió, desarrollar un canal de comunicación de alta velocidad entre el componente acelerador implementado en la lógica programable y el microprocesador del sistema embebido. ser realizadas en paralelo y en una sola iteración del bucle. El desarrollo de pipelines consiste en dividir el trabajo a procesar en subtareas, a modo de que a medida que van entrando los datos a procesar, cada subtarea pueda ir procesando en forma concurrente un diferente set de datos. Entonces, si cada iteración del bucle requiere ejecutar N subtareas, en una implementación sin pipeline, el bucle realizara una cantidad (N * cantidad_elementos_de_datos) de iteraciones para completar su trabajo. En cambio en una implementación con pipeline, la totalidad de datos serán procesados en una cantidad (N + 1) de iteraciones. La teoría de pipelines y desenrollado de bucles ha sido extensamente desarrollada en [5] y [6]. V. Se genero el soporte necesario para que el PPC pueda comunicarse a través de los buses PLB, OPB, FCB, OCM y DCR a los distintos dispositivo. Estos buses pertenecen a la familia de buses CrossConnect y están descriptos en [10]. Cabe aclarar que este procesador solo soporta conexión directa a los buses PLB, OCM, DCR y FCB, por lo que los dispositivos atrás del bus OPB se alcanzaran a través de un bridge PLB2OPB. Una vez definida la arquitectura de buses, sus tamaños y frecuencias de trabajo, así como también los elementos adicionales necesarios para su correcto funcionamiento, se escogió a los dispositivos del kit de desarrollo a los cuales se les dará soporte y como estarán conectados estos a la jerarquía de buses, a modo de que estos sean visibles al procesador PPC. La configuración de los mismos, es particular de cada caso y dependiente del diseño adoptado, aunque por lo general esta configuración especifica incluye aspectos como el tipo de DMA que utilizara, velocidad de funcionamiento, tipo de clock al que estará conectado, pines y redes al que estará conectado, cantidad, tipo de interrupciones que generara y áreas de memoria que estarán reservadas en el mapa de memoria del sistema para los registros del mismo. Cada IPCore de la librería de hardware XilinxProcessorIPLib posee un datasheet que detalla sus parámetros de configuración posibles. DESARROLLO DE UN HPSOC CRIPTOGRAFICO A modo de evaluar las mejoras obtenidas a través de la implementación de un HPSoC acelerado por hardware, se desarrollo un SoC prototipo sin aceleración (implementación solo por software), y dos versiones de un HPSoC con aceleración por hardware. En estos dos últimos casos, el componente acelerador fue desarrollado en VHDL y con la herramienta de síntesis de alto nivel ImpulseC respectivamente. La aplicación criptográfica consistió en obtener un set de datos de memoria y cifrarlos a través del algoritmo de cifrado simétrico TripleDES. El algoritmo de cifrado simétrico TripleDES se utilizó en modo ECB, siguiendo los lineamientos mencionados en [7] y [8]. Siguiendo la metodología propuesta en el presente trabajo, después de diseñar e implementar el sistema embebido en el SoC, se desarrollo en software un prototipo no optimizado del algoritmo a utilizar. Este prototipo sirvió para estudiar el algoritmo y caracterizarlo. Con los datos obtenidos y evaluando las técnicas de optimización enumeradas en [9], se procedió a desarrollar los componentes aceleradores y aplicar los niveles de optimización anteriormente descritos. El canal de comunicaciones de alta velocidad utilizado se implemento por medio del controlador APU, una funcionalidad del procesador PPC descripta en [11]. El controlador APU provee una interfase de comunicación flexible y de alta velocidad entre el fabric de la FPGA y el procesador PPC. Esta interfase de comunicación conecta directamente el pipeline de instrucciones del PPC a uno o más componentes aceleradores de hardware. Cabe aquí citar que para la implementación de los prototipos se utilizó el kit de desarrollo FX12 Minimodule, provisto por la firma Avnet y que cuenta con una FPGA Virtex4 FX12 y diversos componentes externos descritos en la página del fabricante. El diagrama en bloque del HPSoC desarrollado puede verse en la figura 1. B. Desarrollo del soporte del software de control del HPSoC El componente de software de la aplicación del HPSoC se ejecutara con soporte de un sistema operativo. Se eligió Linux como sistema operativo de soporte. Para esto se preparo el sistema operativo Linux a modo que controle los distintos componentes de hardware del sistema embebido. Se genero además un root filesystem con las aplicaciones necesarias para volver funcional al sistema. Se desarrollo además un mecanismo para que el kernel pueda ser cargado en memoria de ejecución mediante el uso de XMD, un debugger provisto por EDK y que a través de JTAG puede bajar y ejecutar binarios ELF compilados para el procesador PPC. Esto permitió que el kernel se pueda ejecutar sobre el sistema embebido, inicializarse, detectar el hardware sobre el que se ejecuta, configurar las interfaces de red, autoconfigurar su dirección de red a través de DHCP y bootear un root filesystem remoto a través de NFS. En la figura 2 se puede observar la iteración de protocolos durante el booteo del kernel. A. Desarrollo del sistema embebido del SoC Durante el desarrollo del diseño embebido se dio soporte a todos los dispositivos físicos de hardware del kit de desarrollo, utilizando los IP Cores de Hardware necesarios para el funcionamiento del sistema embebido. Para implementar el diseño embebido se utilizó la herramienta EDK de Xilinx descrita en [10]. El procesador elegido para el diseño embebido fue un recurso de hardware que posee la FPGA elegida, es decir el hardcore de un PowerPC 405 (PPC). Mediante esta herramienta se desarrollo un sistema embebido que permitió comunicar el procesador PPC con los dispositivos externos del kit de desarrollo, tales como la Memoria RAM, la memoria FLASH, el puerto UART, la PHY de Gigabit Ethernet así como también implementar 67 www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina Ethernet RAM de bloque Bus FCB Power PC 405 I cache HPSoC OPB Bus Bridge Controlador DDR Controlador UART Controlador GPIO Arbitro Arbitro Servidor de pruebas con: - Servicio DHCP server - Servicio NFS server - Entorno de Desarrollo - Buildroot - Crosscompiladores D cache PLB Controlador PHY Componente Acelerador de HW Figura 2. Flujo de consultas para booteo del sistema operativo Controlador HWICAP e) Se incremento la transferencia de datos para utilizar el máximo ancho de banda provisto por el canal APU. Esto es 64 bits de datos. Figura 1. Diagrama en bloques de la arquitectura HPSoC desarrollada La versión de Linux utilizada es la 2.6.20. Se realizaron modificaciones masivas sobre el código del kernel, utilizando código provisto por el fabricante y modificaciones ad-hoc. 2) Optimizaciones a nivel de aplicación: A nivel de aplicación se realizaron optimizaciones sobre el algoritmo TripleDES en si mismo. Como se describe en [9], se pueden realizar cambios en distintos puntos del algoritmo que mejoraran drásticamente la performance del mismo a través del precomputo de datos y de la optimización de las operaciones lógicas de permutación y tablas de búsqueda (operaciones sobre las cajas S). a) Precomputo de datos de las subllaves: Se realizo el precomputo de las subllaves necesarias para operar el algoritmo TripleDES. Esto permitio que las subllaves puedan ser accesibles de forma inmediata. Ademas, el hecho de precomputarlas de antemano permitio que los valores de las mismas puedan ser replicados espacialmente de modo que puedan ser utilizados de forma eficiente en las operaciones del algoritmo TripleDES. El precomputo se puede realizar debido a que se asume que el valor de la llave no será cambiado por el usuario en el futuro. La generación y precomputo de las subllaves se realiza en forma externa y el código se embebe en la descripción del hardware. Además, para poder soportar el canal de comunicaciones APU, hubo que habilitar el bit 6 del registro MSR, MachineState Register del procesador PPC. Este registro define el estado de funcionamiento del procesador, y debe ser configurado en tiempo de inicialización del sistema operativo. En este modo de funcionamiento, el procesador puede utilizar instrucciones vectoriales para transmitir datos a través del canal de comunicación de alta performance entre el hardware y el software. C. Desarrollo de la aplicación del HPSoC Como se mencionó, se desarrollaron tres versiones de la aplicación. Una desarrollada enteramente en software que sirvió como punto de estudio del algoritmo de encriptación. A partir de este prototipo, se desarrollaron dos versiones de componentes aceleradores. Una versión utilizando la herramienta ImpulseC y otra versión desarrollada en VHDL. A ambas versiones se les aplicaron las mismas optimizaciones descritas a continuación. b) Precomputo y combinación de la tabla de permutación P con las cajas S: El algoritmo DES provee un mecanismo de expansión de información a través de un conjunto predefinido de bits conocido como cajas S. El algoritmo incluye además tablas de permutación bits, conocidas como tabla P, que a fines de performance y teniendo en cuenta ciertas modificaciones en la implementación del mismo, pueden ser combinadas con tablas S para precomputar futuro procesamiento. Estas cajas combinadas se llaman cajas SP. 1) Optimizaciones a nivel de sistema: Las optimizaciones a nivel de sistema realizadas sobre la plataforma serán listadas a continuación. a) Se incremento la frecuencia del clock del procesador embebido a 200 Mhz. b) Se incrementaron la frecuencia de los buses PLB y OPB. c) Se incremento componente acelerador. la frecuencia de trabajo Flujo de consultas <- Consulta DHCP -> Respuesta DHCP con información de red y información de servidor NFS <- Petición de montaje a traves de NFS -> Informacion de punto de Montaje del c) Tabla de expansión E embebida: La tabla de expansión E se utiliza en DES para llevar un bloque de datos de 32 bits a un formato de 48 bits, necesario para poder XORear las subllaves con este valor expandido. Con fines de performance, se embebió el proceso de expansión de la tabla E en las operaciones de translación de las cajas SP. d) Se utilizó el máximo nivel de esfuerzo en la síntesis. Esto se logro editando el archivo etc/fast_runtime.opt. Este archivo contiene las opciones de ejecución de las utilidades de mapeo y ruteo de componentes. Ambas utilidades (map y place) fueron seteadas con la opción –ol a high (lo que indica máximo esfuerzo en la síntesis necesario para obtener un diseño optimizado). 3) Optimizaciones a nivel de microarquitectura: A nivel de microarquitectura no se realizaron optimizaciones sobre el algoritmo TripleDES en si mismo, si no que se busco 68 www.sase.com.ar 2 al 4 de marzo de 2011 UTN­FRBA, Buenos Aires, Argentina TABLA I. optimizar las formas en que las operaciones se realizan, así como también la implementación de pipelines, desenrollado de bucles y replicación de datos para favorecer la paralelización de operaciones. a) Implementación de la técnica de secuencias de permutación: A modo de implementar las permutaciones inicial y final de bits de forma optimizada, se utilizó la técnica "secuencias de permutación" descrita también en [9]. Esta técnica es ampliamente utilizada en diversos algoritmos de cifrado de datos, así como también en algoritmos de corrección de errores en la industria. HPSoC TripleDES Implementación Frecuencia de operación Throughput (aplicación userspace) Ganancia 300 Mhz 42.096 Kbps 1X 50 Mhz 17.929 Mbps 415X 50 Mhz 19.280 Mbps 458X Software Hardware ImpulseC Hardware VHDL b) Replicación de datos: Se genero código replicado de entidades de memoria que almacenan los datos de las 8 cajasSP. Esto permitió realizar operaciones de búsqueda en las tablas de forma paralela. El código de estas entidades de memoria fue desarrollado para que durante la sintesis las construcciones infieran en recursos de RAM en bloque. TABLA II. RESULTADOS DE SINTESIS HPSOC CRIPTOGRAFICO HPSoC con componente desarrollado en ImpulseC c) Pipelines: A modo de aumentar el throughput de procesamiento de datos, se subdividió el procesamiento del algoritmo en diferentes etapas que pueden funcionar en forma aislada. Estas etapas se encargan en la gran mayoría de realizar el proceso de combinar las cajas SP con los datos de entrada. El pipeline permitió que se procesen varios datos al mismo tiempo. VI. RESULTADOS DE IMPLEMENTACION HPSOC CRIPTOGRAFICO RESULTADOS OBTENIDOS Las métricas obtenidas de la ejecución del los componentes aceleradores de hardware desarrollados, así como también de la versión en software de la aplicación pueden verse en la tabla I. Recurso Utilización Porcentaje de uso BUFGs 11 out of 32 34% DCM_ADVs 2 out of 4 50% ILOGICs 29 out of 320 9% External IOBs 73 out of 240 30% LOCed IOBs 73 out of 73 100% OLOGICs 54 out of 320 16% RAMB16s 26 out of 36 72% SLICES 5470 out of 5472 99% SLICEMs 355 out of 2736 12% Este trabajo concluye que la utilización de un HPSoC es una alternativa técnicamente viable para mejorar la performance de los sistemas digitales embebidos del mundo actual. En esta tabla se muestra que la aceleración obtenida al implementar parte del algoritmo de la aplicación en un HPSoC con un componente acelerador es de alrededor de 400X en ambos casos. El throughput expuesto corresponde a la medición del tiempo de ejecución de la función de SW que envía los datos al componente acelerador. REFERENCIAS [1] [1] Wohlmuth, Otto, “High performance computing based on FPGAS” IEEE Field Programmable Logic and Applications, FPL, 2008. [2] Ramakrishna, Rau and Fisher, Joseph, "Instruction-level parallel processing: History, overview, and perspective", The Journal of Supercomputing, Volume 7, Numbers 1-2. [3] Meyer-Baese, Uwe, "Digital signal processing with field programmable gate arrays", Third Edition, Springer, pagina 589. [4] D. Pellerin and S. Thibault, “Practical FPGA Programming in C”. Prentice Hall Professional Technical Reference, 2005. [5] Pai, Vijay and Adve, Sarita, "Code transformations to improve memory parallelism", Proceedings of the 32nd annual ACM/IEEE international symposium on Microarchitecture, Pages: 147 - 155, 1999. [6] Wolf, M.E, Chen, Ding-Kai, "Combining loop transformations considering caches and scheduling", 29th Annual IEEE/ACM International Symposium on Microarchitecture, 1996. [7] Bruce Schneier, “Applied Cryptography Second Edition”. John Wiley, 2004. [8] Federal Information Processing Standars Publication, “DATA ENCRYPTION STANDARD (DES)”. FIPS PUB 46-3. [9] PK Yuen, “Practical Cryptology and Web Security”. Pearson Education Limited, Chap 4, 2006. [10] Xilinx Documentation files, “EDK Concepts, Tools, and Techniques”. [11] Shenoy, "Accelerating Software Applications Using the APU Controller and C-to-HDL Tools", Xilinx Application note XAPP 901. Se muestra además en la tabla II un extracto del reporte de la síntesis del componente acelerador más significativo (desarrollado en ImpulseC) que muestra el porcentaje de recursos usados en la FPGA. VII. CONCLUSIONES En el presente trabajo se presentaron los beneficios, en términos de performance, obtenidos a través de la implementación de aceleradores criptográficos utilizando HPSoCs. Las implementaciones realizadas muestran cómo es posible incrementar la performance de una aplicación de software corriendo en un sistema embebido en varios órdenes de magnitud. Los resultados comparativos mostraron que luego de aplicar la metodología propuesta se obtuvo una ganancia de alrededor de 400X en ambos casos. En el presente trabajo se utilizaron además herramientas del estado del arte en el desarrollo de lógica programable para implementar el sistema embebido y los componentes aceleradores. 69