Hoja de Ejercicios - Universidad de Alcalá

Anuncio

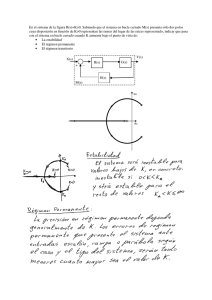

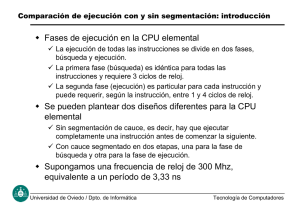

DEPARTAMENTO DE AUTOMÁTICA Universidad de Alcalá Arquitectura II Ejercicios 1.- En un procesador de frecuencia 40 MHz. se ejecuta un benchmark con la siguiente mezcla de instrucciones y ciclos: Tipo Aritmética entera Transferencia de datos Coma flotante Transferencia de control Nº Instrucciones 45.000 32.000 15.000 8.000 Ciclos 1 2 2 2 Calcular Ic, CPI, rendimiento y tiempo de ejecución. 2.- Considerar la ejecución de un programa con 200.000 instrucciones en un procesador a 40 Mhz. La relación de instrucciones y número de ciclos se muestra en la siguiente tabla: Tipo Aritméticas y lógicas Carga / Almacenamiento Bifurcación Referencias a memoria CPI 1 2 4 8 % 60 18 12 10 Calcular CPI y rendimiento. 3.- Una estación de trabajo usa un procesador de 15 MHz. con un rendimiento de 10 MIPS para ejecutar un programa dado. Asumir un ciclo de retardo para cada acceso a memoria. a) b) ¿Cuál es el número de ciclos por instrucción de este computador? Suponer que se actualiza el procesador a una frecuencia de 30 MHz. sin modificar la velocidad de memoria y consecuentemente necesitamos dos ciclos para accesos a memoria. Si el 30% de instrucciones requiere un acceso a memoria y el 5% requiere dos accesos a memoria, ¿cuál es el rendimiento del nuevo procesador? 4.- El tiempo de ejecución en segundos de 4 programas en tres computadores es el siguiente: Programa 1 2 3 4 Comp. 1 1 1000 500 100 C omp. 2 10 100 1000 800 Comp. 3 20 20 50 100 Asumir que en cada programa se ejecutan 100.000.000 instrucciones. Calcular los MIPS de cada programa en cada máquina. Analizar los resultados obtenidos. ¿Se obtiene alguna conclusión clara relativa a los computadores? 5.- Considerar la ejecución de un programa de 15.000 instrucciones en un procesador segmentado con una velocidad de reloj de 25 MHz. El cauce es de 5 etapas y se emite una instrucción por ciclo. a) b) Calcular la ganancia frente a un computador no segmentado. Calcular el rendimiento den MIPS del procesador. 6.- Un procesador no encauzado X tiene un reloj de 25 MHz. y una media de 4 ciclos por instrucción. Una mejora de este procesador Y consiste en un procesador encauzado de 5 etapas, pero su reloj debe reducirse por los ‘latches’ a 20 MHz. a) b) Si ejecutamos un programa de 100 instrucciones, ¿cuál es la ganancia del procesador Y frente al procesador X? Calcular el rendimiento en MIPS de los dos procesadores. DEPARTAMENTO DE AUTOMÁTICA Universidad de Alcalá Arquitectura II 7.- Obtener el diagrama de estados del cauce con la tabla de reserva siguiente, y calcular los ciclos que tienen latencia media mínima. F1 F2 F3 F4 T0 T1 T2 T3 T4 T5 T6 x x x x x x x Obtener el estado de ocupación del cauce cuando se lanzan operaciones según el ciclo de menor latencia media. 8.- Repetir el ejercicio para las siguientes tablas de reserva: F1 F2 F3 F4 F5 T0 T1 T2 T3 T4 T5 T6 T7 x x x x x x x x x F1 F2 F3 T0 T1 T2 T3 A A B AB A B B F1 F2 F3 F4 T0 T1 T2 T3 T4 T5 A B B A B A AB A B A B 9.- El siguiente código calcula el producto escalar de dos vectores: xor r1,r1,r1 xor r3,r3,r3 xor r4,r4,r4 Bucle: lw r5,vector1(r1) lw r6,vector2(r1) multw r6,r6,r5 add r3,r3,r6 add r1,r1,#4 add r4,r4,#1 slt r7,r4,#NumElementos bnez r7,Bucle sw ProdEscalar(r0),r3 a) ;pone un 0 en r1 ;otro en r3 ;otro en r4 ;se carga una componente del vector 1 ;se carga la equivalente del vector 2 ;se multiplican (suponiendo que se pudiera) ;se acumula el producto ;actualización del índice ;incremento del contador ;se comprueba si se ha terminado ;repetir mientras queden componentes ;almacenar resultado Para un cauce como el visto en clase (tema 3, transparencia 8), suponiendo que el código empieza a ejecutarse en el ciclo 0, ¿en qué ciclo se empieza a ejecutar la instrucción ‘add r1,r1,#4’ por primera vez? Explica la respuesta. b) ¿Y la instrucción ‘lw r5,vector1(r1)’ por segunda vez? c) ¿Y si utilizamos adelantamiento de resultados (tema 3, transparencia 19)? d) Clasifica las dependencias de datos que se dan en el código. e) Analiza las dependencias de control. f) Explica cómo se ejecuta el código si se utiliza cada una de las 4 formas de tratar las dependencias de control vistas en el tema 3. (Puede ser necesario modificar ligeramente el código al aplicar alguna de las técnicas). g) Suponiendo latencias de 2 ciclos para las instrucciones de carga y de 1 ciclo para las de proceso, reordena el código de forma que se minimice el número de parones que se dan en la ejecución del dódigo. DEPARTAMENTO DE AUTOMÁTICA Universidad de Alcalá Arquitectura II 10.- En el siguiente código: xor r1,r1,r1 xor r3,r3,r3 xor r4,r4,r4 Bucle: Lw r5,vector1(r1) Lw r6,vector2(r1) multw r6,r6,r5 add r3,r3,r6 add r1,r1,#4 add r4,r4,#1 slt r7,r4,#NumElementos bnez r7,Bucle sw ProdEscalar(r0),r3 ;pone un 0 en r1 ;otro en r3 ;otro en r4 ;se carga una componente del vector 1 ;se carga la equivalente del vector 2 ;se multiplican (suponiendo que se pudiera) ;se acumula el producto ;actualización del índice ;incremento del contador ;se comprueba si se ha terminado ;repetir mientras queden componentes ;almacenar resultado a) Aplicar un desenrollado de orden 4. b) Explicar cómo se aplica el renombrado de registros para las 3 primeras iteraciones. c) Suponiendo que se aplica el renombrado de registros y el adelantamiento de resultados, y el cauce es el del tema 3, transparencia 19, pero adaptado a un superescalar de grado 4, ¿en qué ciclo se ejecuta la instrucción ‘add r1,r1,#4’ por primera vez? d) ¿Y la instrucción ‘lw r5, vector1(r1)’ por segunda vez? e) Suponiendo que el superescalar tiene ejecución fuera de orden, en qué ciclo se retiran estas dos instrucciones? 11- El siguiente código en ensamblador calcula el producto escalar de dos vectores: or r1,r0,r0 Bucle: ld r2,VectorA(r1) ld r3,VectorB(r1) mul r4,r2,r3 add r5,r5,r4 add r1,r1,#4 cmpe r4,r1,#FinVector bne r4,bucle Trazar la ejecución de este código en un procesador superescalar de ancho 4, con ejecución fuera de orden. El procesador dispone de 6 registros lógicos (r0 a r5) y 12 físicos (f1 a f12). El cauce consta de las etapas de búsqueda, decodificación, entrada en el ROB y renombramiento, ejecución, terminación y retirada / almacenamiento. El ROB dispone de 10 entradas. 12.-Repetir el ejercicio anterior para el siguiente código que suma dos vectores: or r1,r0,r0 Bucle: lw r2,VectorA(r1) lw r3,VectorB(r1) add r4,r2,r3 stw VectorC(r1),r4 add r1,r1,#4 sgt r4,r1,#FinVector bne r4,Bucle DEPARTAMENTO DE AUTOMÁTICA Universidad de Alcalá Arquitectura II 13.-El siguiente fragmento de código: xor r1,r1,r1 ;inicializar índice xor r4,r4,r4 ;inicializar cuenta Bucle: lb r2,Texto(r1) ;carga letra seqi r3,r2,’a‘ ;compara con la ‘a’ beqz r3,Seguir addi r4,r4,#1 ;si es ‘a’, incrementa contador Seguir: addi r1,r1,#1 ;siguiente letra slt r7,r1,#NumeroLetras ;comprobar fin del texto bnez r7,Bucle nop cuenta el número de veces que aparece la letra ‘a’ en un texto. a) Aplicar predicación para eliminar el salto interno al bucle. b) Si el texto sobre el que trabaja es el siguiente: ‘¡Qué aburrido es estudiar arquitecturas avanzadas!’, suponiendo que se dispone de un predictor basado en contadores de 2 bits con valores iniciales 01, con 1024 contadores, y un BTB de 32 entradas, y que el código está almacenado a partir de la dirección 1000h, cada instrucción ocupando 4 bytes, ¿cuántos aciertos y cuántos fallos tiene el predictor en cada uno de los saltos del código? 14.-Repetir el ejercicio anterior para el siguiente código, que cuenta el número de ceros y de unos que hay en una lista de dígitos binarios: or r5,r0,r0 or r4,r0,r0 or r1,r0,r0 Bucle: lw r2,Lista(r1) beqz r2,Cero addi r4,r4,#1 j Seguir Cero: addi r5,r5,#1 Seguir: addi r1,r1,#4 seqi r6,r1,#NumeroElementos*4 beqz Bucle nop en las mismas condiciones del ejercicio anterior, para la lista: 00100101001 15.-Se quieren sumar dos vectores en un procesador vectorial. Los elementos del primer vector están almacenados en memoria con espaciado 17 (hay 16 palabras entre cada dos elementos del vector). Los elementos del segundo vector tienen espaciado 3, y los elementos del vector resultado tienen espaciado 5. En cada ciclo, el cauce puede leer dos valores de registros vectoriales y escribir un tercero a un registro. Cuando se carga un registro vectorial desde la memoria, se necesita un ciclo para computar la dirección antes de comenzar el acceso a memoria. Cada módulo de memoria tiene un tiempo de acceso de 16 ciclos. Suponiendo que la memoria tiene un entrelazado de inferior de orden 16, ¿cuánto se tarda en sumar los dos vectores? 16.-Disponiendo de una máquina tipo SIMD, diseñar el algoritmo (incluyendo la disposición de datos) para multiplicar dos matrices cuadradas. 17.-Repetir el ejercicio anterior para una máquina vectorial.