Problemas de rendimiento - Asignaturas DIICC, UdeC

Anuncio

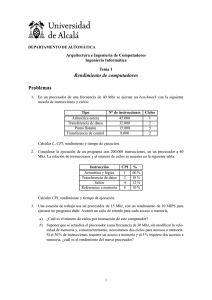

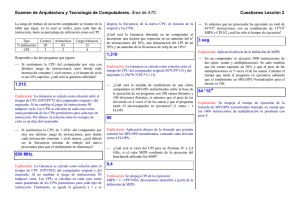

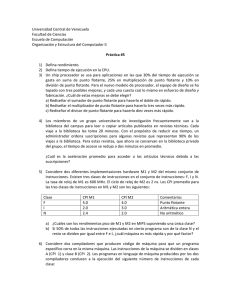

Problemas Perfomance Arquitectura y Organización de Computadores Javier Vidal Valenzuela August 15, 2007 1 Problema 1 Se tienen dos implementaciones distintas para una misma máquina MIPS R2001. La versión A, que tiene un clock de 1000 MHz y dos tipos de instrucciones, las α y las β con un CPI de 2 y 1 respectivamente. La versión B, tiene un reloj un 5% más rápido que A y el CPI de las instrucciones tipo α y β es de 2. En la máquina A se ejecuta un código que tiene 300 millones de instrucciones α y 700 millones de instrucciones β, mientras que en la máquina B, el mismo código, ahora optimizado, ejecuta dos tercios de las instrucciones tipo α y la misma cantidad de instrucciones tipo β. Calcular: • El CPI del código en cada implementación. • Los MIPS del código en cada implementación. • ¿Cuál de las dos implementaciones ejecuta más rápidamente el código? Justifique adecuadamente su respuesta. 2 Problema 2 Para las máquinas M1 (que tiene un reloj de 1 GHz) y M2 (que tiene un reloj de 1.2 GHz), los tres tipos y la cantidad de instrucciones enteras ejecutadas por ellas indicadas en las tablas que se presentan a continuación, se pide: 1. Determinar cuál es más rápida según CPI. 2. Determinar cuál es más rápida según MIPS. 3. Determinar cuál es más rápida según CPUtime. 4. Determinar cuál de las dos es realmente la más rápida. CPI Tipo A 1 Tipo B 2 Máq M1 M2 Tipo C 3 1 instr A 5 mill 10 mill instr B 1 mill 1 mill instr C 1 mill 1 mill Arquitectura y Organización de Computadores 3 Problema 3 Considere el siguiente código assembly MIPS loop: addi muli addi addi lw lw add sw bnq $5,$0,n $5,$5,4 $10,$0,$0 $10,$10,4 $15,0x1000($10) $20,0x2000($10) $30,$15,$20 $30,0x3000($10) $10,$5,loop 1. ¿Qué hace el programa?. Explique brevemente. 2. Si n = 5 y el CPI de las instrucciones store es 4, el de las load es 5, el de las branch es 3 y el de las ALU 4; calcule el CPI, los MIPS y el tiempo de ejecución del código si el reloj de la CPU es de 1000 MHz. 3. Se introduce una mejora de hardware que reduce en un 15% el CPI de las instrucciones ALU. ¿Cuál es la mejora obtenida con esta nueva implementación?. 4. Considere la versión del procesador MIPS segmentado visto en clase. Reescribir el código anterior insertando la cantidad de instrucciones nops necesarias para que la máquina no se detenga si la CPU segmentada NO usa forwarding y si la CPU usa forwarding. Nota: Recordar que la multiplicación es una operación aritmética. 4 Problema 4 Considere una implementación de MIPS (MIPS1), con los siguientes tiempos de ejecución para cada tipo de instrucción: Tipo de instrucción ALU Load Store Saltos incondicionales Saltos condicionales Ciclos por instrucción 6 10 10 4 5 La máquina funciona con un reloj de 2.8GHz. Para evaluar el desempeño de esta máquina (y potenciales mejoras a ella) se utiliza un benchmark con las siguientes frecuencias de ejecución de instrucciones: 2 Arquitectura y Organización de Computadores Tipo de instrucción ALU Load Store Saltos incondicionales Saltos condicionales Frecuencia (%) 35 25 15 10 15 Muestre claramente su trabajo para cada parte del problema • Calcule el CPI y el MIPS del benchmark proporcionado arriba. • Una mejora en la tecnologı́a VLSI utilizada para implementar una nueva versión del procesador (MIPS-II) permite aumentar la frecuencia de reloj a 3.4GHz. Todas las instrucciones que no hacen acceso a memoria reducen proporcionalmente su tiempo de ejecución, por lo que se ejecutan en el mismo número de ciclos que MIPS-I. Lamentablemente la tecnologı́a utilizada para implementar la memoria de datos no permite reducir su tiempo de acceso, por lo que el tiempo de ejecución de las instrucciones Load y Store en MIPS-II es igual al de MIPS-I. Determine los CPI y MIPS de MIPS-II ejecutando el benchmark, y calcule la aceleración de MIPSII sobre MIPS-I. Recuerde que una instrucción siempre se ejecuta en un número entero de ciclos de reloj. (10 puntos) • Considere que al procesador MIPS-I se le agrega una memoria cache para mejorar el desempeño de las instrucciones Load y Store, con lo cual los ciclos para load y store se reducen a 8. Utilizando la ley de Amdahl, determine qué porcentaje de las instrucciones Load y Store deberı́a acelerar la memoria cache para que la aceleración sobre MIPS-I conseguida con esta mejora sea la misma que la alcanzada en el punto (b). (15 puntos) 5 Problema 5 Considere los siguientes parámetros para una máquina: • Frecuencia de las operaciones en punto flotante: 25% • CPI promedio para las operaciones de punto flotante: 4.0 • CPI promedio para otras instrucciones: 1.33 • Frecuencia de operación raı́z cuadrada: 2% • CPI para operación raı́z cuadrada: 20 Suponga que existen dos alternativas de diseño: la primera considera la reducción a 2 CPIs para la instrucción raı́z cuadrada y la segunda considera la reducción a 2 CPIs para todas las operaciones en punto flotante. Comparar estas dos alternativas de diseño usando la ecuación de rendimiento de la CPU. 3