- Ninguna Categoria

C2 - Departamento de Electrónica

Anuncio

1

Capítulo 2

Síntesis en dos niveles

2.1. Formas de Funciones.

Pueden escribirse diversas expresiones para una función.

Existen dos formas básicas de expresiones booleanas que pueden ser implementadas en dos

niveles de compuertas.

a) Suma de Productos (OR de ANDs).

Se denomina forma normal disyuntiva. Si uno de los sumandos (producto lógico de

variables) toma valor lógico 1, la expresión tomará valor lógico 1.

Ejemplo 1: AB ' C B ' D A ' CD ' con 8 literales y 11 entradas.

b) Producto de Sumas (AND de ORs).

Se denomina forma normal conjuntiva. Si uno de los productos (suma lógica de variables)

toma valor lógico 0, la expresión tomará valor lógico 0.

Ejemplo 2: ( A ' B C )( B ' C D)( A C ' D) con 9 literales y 12 entradas.

Existen formas híbridas que son mezclas de las dos anteriores, y que en general tienen

representación en redes con más de dos niveles de compuertas.

Las formas híbridas se pueden reducir a una de las anteriores, aplicando postulados y

teoremas.

Ejemplo 3: AB(C+D)+E es una forma híbrida, de 5 literales, 8 entradas y 3 niveles que

puede ser representada como suma de productos según: ABC+ABD+E, con 7 literales, 9

entradas y 2 niveles. La forma híbrida tiene menor costo espacial, pero mayor costo temporal.

Toda expresión booleana puede ser representada en estas dos formas básicas.

Por ejemplo para el Ejemplo 1, se tiene la forma producto de sumas: ( A B )(C D)( A C )

con 6 literales y 9 entradas, que es de menor costo. La equivalencia entre ambas formas puede

ser demostrada aplicando los postulados y teoremas.

También se tiene para el Ejemplo 2, la forma equivalente según suma de productos:

A ' B ' C ' AC BD CD , con 9 literales y 13 entradas, que es de mayor costo. En este caso también

se tiene la forma equivalente: A ' B ' C ' AC BD A ' D .

Profesor Leopoldo Silva Bijit

13-04-2010

2

Sistemas Digitales

Existen dos formas especiales de suma de productos y producto de sumas que se denominan:

Suma de mintérminos y Producto de maxtérminos; las cuales permiten expresar funciones

booleanas en forma normalizada.

Las formas canónicas son representaciones estandarizadas de expresiones booleanas y

permiten asociar a una función una expresión algebraica única. Escritas de esta manera pueden

efectuarse comparaciones entre expresiones booleanas.

Una forma canónica destaca las componentes más primitivas de una expresión.

Existe sólo una forma de escribir la tabla de verdad de una función y sólo una forma

canónica, pero existen diversas representaciones de la función, mediante esquemáticos o

expresiones booleanas.

Los términos elementales con los que se construyen las formas canónicas se denominan

mintérminos y maxtérminos. Una forma canónica no es una expresión mínima.

2.2. Mintérminos

En una función de n variables, un mintérmino es un producto que contiene las n variables,

pudiendo éstas estar o no complementadas.

Para el caso de dos variables, los mintérminos son:

AB, A’B, AB’, A’B’

Puede comprobarse que para tres variables, el número de mintérminos es 8, y para n

variables se tendrán 2 n mintérminos.

Debe notarse que cada renglón de una tabla de verdad está asociado a un y sólo un

mintérmino.

Cada mintérmino puede ser asociado a un número decimal.

Para simplificar la notación, una vez ordenadas las variables de acuerdo a cierto criterio, se

asigna un "1" a una variable no complementada y un "0" a las complementadas, formando así un

número binario, el cual expresado en sistema decimal se emplea para referenciar unívocamente

a cada mintérmino.

Ejemplo 2.1. Definición de mintérmino

Sea: A B C un mintérmino en caso de tener una función de tres variables. Entonces el

código binario es 010, este número expresado en decimal es 2. El criterio de ordenación de las

variables es alfabético. Se anota: m2 A BC

Una función booleana puede describirse por la suma de los mintérminos que la constituyen.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

3

En general:

f

mi

La anterior es una forma particular de suma de productos.

Una simplificación adicional es escribir una lista de mintérminos según:

f

m(1,3,8)

Esto indica que f está formada por la suma de m1 , m3 y m8 .

Debe destacarse que es importante el orden de las variables antes de asignar códigos

binarios.

Ejemplo 2.2. Suma de mintérminos

Obtener la tabla de verdad para:

f ( A, B, C )

m(2, 6)

ABC

ABC

Se tiene:

# ABC f m2 m6

0 000 0 0

0

1 001 0 0

0

2 010 1 1

0

3 011 0 0

0

4 100 0 0

0

5 101 0 0

0

6 110 1 0

1

7 111 0 0

0

Figura 2.1 Tablas de verdad de algunos Mintérminos.

La tabla de verdad de un mintérmino contiene uno y sólo un valor lógico "1"; el resto son

"0"s. La posición del "1", define unívocamente un renglón. Cada columna de un mintérmino, a

través de la operación OR, deja un uno, en un renglón determinado de la columna de f.

La suma lógica de los mintérminos no incluidos en la sumatoria que describe a f, son los

mintérminos de la función complementada, en el caso del ejemplo anterior:

f

m(0,1, 3, 4, 5, 7)

2.3. Maxtérmino.

Es una suma lógica que contiene todas las variables, pudiendo éstas estar o no

complementadas.

Profesor Leopoldo Silva Bijit

13-04-2010

4

Sistemas Digitales

La tabla de verdad de un maxtérmino contiene uno y sólo un valor lógico "0"; el resto son

"1"s. La posición del "0" define unívocamente a un renglón de la tabla de verdad.

Para dos variables, los maxtérminos son: ( A B), ( A B ), ( A B) y ( A B )

Para n variables se tendrán 2 n maxtérminos.

El código decimal para identificar a los maxtérminos se obtiene, una vez ordenadas las

variables dentro de una suma de acuerdo a cierto criterio, asignando un "0" a cada variable no

complementada y un "1" a las variables complementadas. Debe notarse que esta asignación es

diferente (dual) de la elegida para mintérminos.

Ejemplo 2.3. Definición de maxtérmino.

Sea: ( A B C ) un maxtérmino. Entonces el código binario es: 101. El número expresado

en decimal es 5 y se anota: M 5

A B C

Una función puede describirse como el producto de los maxtérminos que la constituyen.

Cada maxtérmino asegura un cero de la función en un determinado renglón.

f

En general:

Mi

Es una forma particular de producto de sumas. También puede abreviarse mediante una lista

de los números decimales de los maxtérminos.

Ejemplo 2.4. Producto de maxtérminos

Obtener la tabla de verdad para:

f ( A, B, C )

M (2, 6)

(A B

C )( A

B

C)

Se tiene:

# ABC f M2 M6

0 000 1 1

1

1 001 1 1

1

2 010 0 0

1

3 011 1 1

1

4 100 1 1

1

5 101 1 1

1

6 110 0 1

0

7 111 1 1

1

Figura 2.2. Tablas de verdad de algunos Maxtérminos.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

5

La tabla de verdad de un maxtérmino contiene uno y sólo un valor lógico “0”, el resto son

“1”s. La posición del cero define unívocamente al renglón. Cada columna de un maxtérmino,

deja un cero a través de la operación AND, en un renglón determinado de la columna de f.

El producto lógico de los maxtérminos no incluidos en f, corresponde a la función

complemento:

f

M (0,1,3,4,5,7)

Relaciones

Con los códigos elegidos para denotar mintérminos y maxtérminos, se cumplen:

mi

Mi

Mi

mi

mi

Mi

Mi

mi

Para n variables se tendrá que:

i (2n ) 1

mi 1

i 0

i (2n ) 1

Mi

0

i 0

Es decir, la suma lógica de todos los mintérminos de n variables es igual a 1; y el producto

lógico de todos los maxtérminos tiene valor lógico cero.

Ejemplo 2.5. De suma de mintérminos a productoria de maxtérminos.

Expresar como producto de maxtérminos, la función f y su complemento:

f(A,B,C)

f

Se tiene, para la función f:

m( 2,3,6,7 )

m2 m3 m6 m7

f m2 m3 m6 m7

Complementando:

Reemplazando los mintérminos complementados por maxtérminos:

f

M2 M3 M6 M7

Finalmente, para la función complementada:

f

M (2,3, 6, 7)

Se puede escribir la función complementada, como la suma de los mintérminos que no están

f m0 m1 m4 m5

presentes en la función, es decir:

Aplicando De Morgan:

Profesor Leopoldo Silva Bijit

f

f

m0

m1 m4

m5

13-04-2010

6

Sistemas Digitales

Resulta:

f m0 m1 m4 m5

Reemplazando los mintérminos complementados por maxtérminos:

f

M 0 M1 M 4 M 5

f

Finalmente:

M (0,1, 4,5)

2.4. Expansión a formas canónicas

Cualquier función booleana puede ser representada en forma canónica. El proceso de obtener

la forma canónica se denomina expansión.

Un método directo consiste en obtener la tabla de verdad, y luego identificar los mintérminos

o los maxtérminos. Otra posibilidad, que se estudia a continuación, es mediante un desarrollo

algebraico basado en los postulados y teoremas del álgebra de Boole.

2.4.1. Expansión de suma de productos

Está basado en el uso repetitivo del teorema: a

ab

ab

Ejemplo 2.7. Expansión a mintérminos.

f (a, b, c)

a

bc

abc

El término "a" puede expandirse según:

a

ab ab

abc ab c abc ab c

m7 m5 m6 m 4

;se completan las variables que faltan.

Para bc’ se tiene:

bc

abc

m6

a bc

m2

Se tiene que: abc = m7 , es un mintérmino.

Usando el teorema de idempotencia (m6 + m6 = m6), se obtiene:

f (a, b, c)

m(2,4,5,6,7)

2.4.2. Expansión de productos de sumas

Está basado en completar los factores, mediante el uso de: a

(a

b)( a

b)

Ejemplo 2.8. Expansión a maxtérminos

f (a, b, c)

(a

b)(b

c)

Se tiene que:

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

a b

7

(a b c) (a b c )

M 0 M1

(a b c ) (a b c )

Considerando, por idempotencia, que: M 1

M 1M 1

M1 M 5

b c

Finalmente:

f (a, b, c)

M 0 M 1M 5

2.5. Síntesis de las formas.

2.5.1. Suma de productos

Dada una función mediante una suma de productos, ésta puede implementarse usando un

OR de AND's.

Ejemplo 2.9. OR de ANDs

Para: f (a, b, c, d )

ab cd , se logra directamente:

a

b'

f

c

d

Primer Nivel

| Segundo Nivel

Figura 2.3. Suma de productos en dos niveles.

Se dice que es una implementación en dos niveles.

Una red es de n niveles, cuando una señal de entrada debe pasar a través de n compuertas

para llegar a la salida; la señal de entrada que recorra más compuertas hasta llegar a la salida, es

la que define la cantidad de niveles; el recorrido se denomina ruta crítica y define el retardo de

propagación de la red. Debe notarse que se considera que se dispone de b' (si sólo se dispone de

b, se requiere un nivel adicional).

También puede implementarse usando solamente compuertas NAND.

Ejemplo 2.10. Dos niveles de NANDs

En el ejemplo 2.9. aplicando involución, se logra:

f

ab

cd

ab cd

; por involución .

; por De Morgan.

Gráficamente:

Profesor Leopoldo Silva Bijit

13-04-2010

8

Sistemas Digitales

a

b'

f

c

d

Figura 2.4. Suma de productos mediante NANDs.

La técnica anterior se denomina "Método de doble complementación", la cual se puede

visualizar en forma gráfica agregando dos pequeños círculos a la salida de la Figura 2.3.

a

a

f

f

b'

b'

c

c

d

d

Figura 2.5. Doble complementación.

Luego se emplea, el equivalente gráfico del Teorema de De Morgan, que se muestra en la

Figura 2.6.

Figura 2.6. Equivalencia gráfica del teorema de De Morgan.

Finalmente se desplazan los pequeños círculos, en las entradas de la compuerta de salida,

hacia las salidas de las compuertas de primer nivel; resultando la Figura 2.4.

2.5.2. Producto de sumas

Dada una función mediante un producto de sumas, puede lograrse una implementación en

dos niveles; usando un AND de OR's.

Ejemplo:

f

(A

B ) (C

D)

Se obtiene:

A

B'

f

C

D

Figura 2.7. Producto de sumas en dos niveles.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

9

Esto en el caso de emplear compuertas AND y OR. También puede aplicarse el método de

la doble complementación para un diseño basado en compuertas NOR.

Algebraicamente:

f

( A B ) (C

D)

; involución

( A B ) (C

D)

; De Morgan

Resulta:

A

f

B'

C

D

| Primer Nivel

| Segundo Nivel

|

Figura 2.8. Suma de productos mediante NORs.

El circuito anterior, puede obtenerse directamente a partir del basado en AND y OR, de la

Figura 2.7, usando el equivalente gráfico del teorema de De Morgan, que se muestra en la

Figura 2.9.

Figura 2.9. Visualización esquemática del teorema de De Morgan.

2.5.3. Conversión de producto de sumas a suma de productos. Cambio de lógica.

Si se tiene una expresión tipo producto de sumas, mediante la doble complementación, el

circuito a la izquierda de la Figura 2.10, puede modificarse como se muestra en el esquemático

de la derecha:

A

A

B'

f

C

D

B'

f

C

D

Figura 2.10. De producto de sumas a Suma de productos.

Aplicando De Morgan, a las compuertas de primer y segundo nivel se obtiene la red de la

Figura 2.11 izquierda. Luego complementando las variables de entrada y salida, se obtiene el

esquema de suma de productos.

Profesor Leopoldo Silva Bijit

13-04-2010

10

Sistemas Digitales

A

f

B'

A'

B

f'

C'

D'

C

D

Figura 2.11. Complementos de las entradas y salidas.

Debe notarse que la implementación como suma de productos tiene todas las variables de

entrada y salida complementadas, respecto a la forma producto de sumas. Es decir, plantea la

expresión en términos de los complementos de las variables originales.

También puede convertirse una expresión tipo suma de productos a la forma producto de

sumas. En un esquemático, se cambian los ANDs del primer nivel por ORs; y el OR del

segundo nivel por un AND; además se complementan las variables de entrada y la de salida.

Si se cambia la asignación de valores físicos a lógicos por su forma complementaria, el

diseño en dos niveles basado en suma de productos puede efectuarse como producto de sumas y

viceversa.

2.6. Diseño lógico

2.6.1. Fan-in. Fan out.

En la práctica, las compuertas lógicas tienen ciertas características. Una de ellas es el fan-in,

que es el número de entradas de una compuerta.

En componentes electrónicas integradas en pequeña escala, el caso de las compuertas lógicas

OR, AND, NOT, NOR y NAND, las pastillas suelen ser de 14 pines o patas. Dos de ellas se

emplean para proveer la alimentación continua (Vcc) y la Tierra (Gnd). Debido a esto, a medida

que aumenta el número de entradas a una compuerta, disminuye el número de circuitos, o

compuertas de igual tipo, que soporta la pastilla. Por ejemplo, se tienen 4 circuitos de 2

entradas, 3 de 3 entradas, 2 de 4 entradas.

Fan-out se denomina el número de compuertas que pueden ser alimentadas o comandadas

por una salida.

Si en un diseño lógico se efectúan restricciones de fan-in y fan-out, se tendrá una

representación en más de dos niveles.

A mayor número de niveles, habrá un comportamiento más lento del circuito; ya que una

conmutación debe propagarse a través de más compuertas.

A menor número de niveles se tendrá que ocupar compuertas de mayor fan-in, lo que

generalmente implica ocupar más pastillas en una implementación.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

11

2.6.2. Observaciones sobre la forma Producto de Sumas.

Algunas observaciones sobre la forma AND de ORs:

Si se observa la siguiente tabla de verdad:

f

0

1

0

1

1

1

0

0

f1

0

1

1

1

1

1

1

0

f2

1

1

0

1

1

1

0

1

Figura 2.12. AND de columnas.

Se advierte que, dada la elección de las funciones, se cumple: f = f1 f2

Donde f1 y f2 son grupos de maxtérminos de f, y son agrupaciones disjuntas. Los

maxtérminos de f1 no están presentes en f2 y viceversa.

Ambas funciones pueden representarse como producto de maxtérminos; es decir, como

producto de sumas.

La minimización consiste en encontrar los mayores grupos de maxtérminos que puedan

escribirse como un solo sumando con el menor número de literales. En ese caso al grupo se lo

denomina implicante. Esto minimiza el fan-in de las compuertas ORs que implementan el

sumando. A la vez, la minimización también consiste en determinar el menor número de grupos

disjuntos, ya que esto minimiza el fan-in del AND que forma el producto lógico.

2.6.3. Observaciones sobre la forma Suma de Productos.

Algunas observaciones sobre la forma OR de ANDs:

Si se observan las siguientes tablas de verdad:

f

0

1

0

1

1

1

0

0

f1

0

1

0

0

0

1

0

0

f2

0

0

0

1

1

0

0

0

Figura 2.13. OR de columnas.

Profesor Leopoldo Silva Bijit

13-04-2010

12

Sistemas Digitales

Se advierte que, dada la elección de las funciones, se cumple: f = f1 + f2

Donde f1 y f2 son grupos de mintérminos de f, y son agrupaciones disjuntas. Los mintérminos

de f1 no están presentes en f2 y viceversa.

Ambas funciones pueden representarse como suma de mintérminos; es decir, como suma de

productos.

La minimización consiste en encontrar los mayores grupos de mintérminos que puedan

escribirse como un solo producto con el menor número de literales. En ese caso al grupo se lo

denomina implicante. Esto minimiza el fan-in de las compuertas AND que implementan el

producto. A la vez, la minimización también consiste en determinar el menor número de grupos

disjuntos, ya que esto minimiza el fan-in del OR que forma la suma lógica.

2.6.4. Observaciones sobre las diferentes formas de diseño.

Existen básicamente dos metodologías de diseño. Una es agrupar los mintérminos de la

función, lo que lleva a la forma suma de productos; la otra es agrupar los maxtérminos de la

función, lo que lleva a la forma producto de sumas.

El primer método es equivalente a agrupar los ceros (maxtérminos) de la función

complementada.

El segundo método es equivalente a la agrupación de unos (mintérminos) de la función

complementada.

A muchas personas les resulta más sencillo formar agrupaciones de unos. Entonces:

agrupando los unos de la función se logra la forma suma de productos; y agrupando los unos de

la función complementada, se genera mediante De Morgan la forma producto de sumas, ya que

esto equivale a agrupar los ceros de la función. Luego debe compararse el costo de ambos

diseños para obtener el mínimo.

2.6.5. Perturbaciones. Diseños con riesgos.

En diseños de redes combinacionales pueden presentarse perturbaciones. En el caso de la red

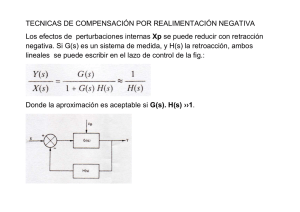

de la Figura 2.14, la salida puede expresarse según:

P = (((A’+B)’ + (D’+ C)’)’ + A)’ = A’(AB’+C’D)

Entonces con {B=0, C=1} o {B=0 y D=0}, se presenta perturbación, en canto de subida de A

atrasado, ver Figura 1.9.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

13

A

A

B

C

D

P = A'(AB' + C'D)

Figura 2.14. Perturbación en red combinacional

Las carreras entre los cantos, pueden evitarse en este caso cambiando el diseño.

Minimizando se logra un diseño libre de perturbaciones: P = A' C' D

Una perturbación puede eliminarse, suprimiendo la posibilidad de formar: (A + A') o (A A')

en la función; esto congelando en "1" ó "0" el resto de las variables.

Para esto se usa el teorema del consenso, que para tres variables puede escribirse:

AB AC

Si B=1 y C=1, queda: A

A

AB AC BC

A A 1

El término de consenso elimina la perturbación, colocando un uno lógico cuando se produce

la condición de perturbación. Lo cual se ilustra a continuación:

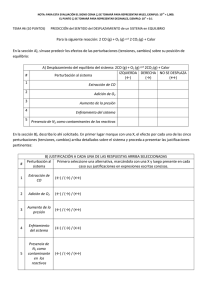

2.6.5.1. Perturbación estática en uno.

La tabla de verdad de f, se ilustra mediante una representación denominada mapa de

Karnaugh, que se estudiará en detalle en el Capítulo 5.

AB

00

C

0

1

1

1

0

1

01

11

2

1

3

1

1

6

10

7

f(A, B, C)=AB+A’C+BC

4

5

A'

C

A

B

f

B

C

Figura 2.15. Eliminación de perturbación en uno.

Profesor Leopoldo Silva Bijit

13-04-2010

14

Sistemas Digitales

Con B=1 y C=1, si se producen transiciones de A, éstas implican perturbaciones. Esto

permite identificar su ocurrencia en un mapa; se producen cuando el diseño tiene implicantes

adyacentes. Se corrige con el término de consenso, que de un punto de vista formal es

redundante; y en la práctica elimina la perturbación, cubriendo la zona en que los implicantes

tienen la adyacencia.

En el caso del ejemplo: ésta se produce en el canto de bajada de A, si A’ está atrasada

respecto a A; y en el de subida de A, si A’ está adelantada respecto a A.

Lo diseños basados en suma de productos pueden generar perturbaciones en 1; y los basados

en producto de sumas pueden generar perturbaciones en 0.

2.6.5.2. Perturbación estática en cero.

Si se tiene: f

( A B)( A ' C ) .

A

B'

f1

f

A’

C

f2

Figura 2.15a. Perturbación en cero.

La condición para la perturbación, se produce con B=0 y C=0, cuando ocurre un canto de

subida de A (con A’ atrasada respecto de A); la salida del and equivale al producto: AA’.

Las perturbaciones en cero, se eliminan introduciendo una suma de términos adicional,

empleando el teorema del consenso: ( A B)( A' C ) ( A B)( A' C )(B C ) .

A

B

f1

B

C

A’

C

f

f2

Figura 2.15b. Eliminación de perturbación en cero.

En este caso, cuando B=0 y C=0, la salida será: f

produce perturbación.

( A 0)( A ' 0)(0 0) 0 , y no se

Resumiendo: se producen perturbaciones estáticas, cuando hay agrupaciones adyacentes

(éstas difieren en una variable). Se denominan estáticas, pues es un cambio momentáneo de un

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

15

nivel constante (Spikes o glitches), produciendo un falso cero o un falso uno. El falso cero se

denomina perturbación estática en uno; el falso uno se denomina perturbación estática en cero.

Figura 2.16. Falsos ceros y unos.

El circuito combinacional, que en determinadas condiciones de las entradas, puede presentar

perturbaciones en la salida se denomina riesgoso (hazard). Mediante diseños en dos niveles, y

cuando se cubren las adyacencias entre implicantes, empleando compuertas adicionales, se

logran diseños de redes combinacionales libres de riesgos.

Ejemplo 2.11. Análisis de perturbaciones.

En el esquemático de la Figura 2.17, se tiene: f

AB

BC

A

f

B

C

Figura 2.17. Análisis de perturbaciones.

Puede determinarse si se produce o no perturbación, analizando si llegan señales y sus

complementos a una misma compuerta.

En el caso de la Figura 2.17, si A=0 y C=1 se tiene f = B'+B lo que implica la posibilidad o

riesgo de perturbación en f.

Para determinar cuándo se produce, es preciso conocer cual de las señales llega primero. En el

caso de la Figura 2.17, B llega al OR de la salida, con un retardo de propagación, a través del

AND; y B’ pasando a través del NOT llega al OR de salida, con dos retardos de propagación.

Como B' está atrasada respecto de B, la perturbación se produce en el canto de bajada de B.

Ver Figura 1.9.

En un mapa (ver Capítulo 5) se puede visualizar el riesgo de perturbación, debido a

agrupaciones adyacentes. En la Figura 2.18 se visualiza la perturbación al pasar B de 1 a 0, es

un caso de falso cero, ya que la implementación es del tipo suma de productos.

Profesor Leopoldo Silva Bijit

13-04-2010

16

Sistemas Digitales

AB

00

C

0

1

1

1

0

1

01

11

2

1

3

1

6

7

10

4

5

f(A, B, C)=A'B'+BC

Figura 2.18. Visualización de perturbaciones en mapas.

Puede corregirse el diseño:

a) atrasando B, colocando condensadores, dependiendo su ubicación y la forma de conectarlo de

la familia lógica. Esta solución no es general.

b) colocando compuerta de consenso A’C. La solución con compuertas que cubran las

transiciones entre implicantes es de tipo general y no depende de la frecuencia de las señales

presentes. Un circuito, con las compuertas adicionales, se denomina libre de riesgos.

Ejemplo 2.12.

En circuitos diseñados con más de dos niveles, pueden generarse perturbaciones con más de

un cambio momentáneo. Por ejemplo si debiendo estar en uno, tiene dos o más caídas a cero en

un leve período de tiempo.

El siguiente circuito, de la Figura 2.19, tiene una perturbación, de más de un pulso, en 1; el

resto de las variables se asumen unos para habilitar las entradas a los ands.

La señal en f1 tiene una perturbación en 1, ocurre lo mismo en f2. Libre de perturbaciones la

señal en f debería ser un uno. Sin embargo se presenta una perturbación de más de un pulso,

como se ilustra en las formas de ondas de la Figura 2.20, si el tiempo de propagación de la vía

que genera f2 es mayor que el retardo con que se produce f1.

a’

b

f1

a

c

a’

d

a

e

f

f2

Figura 2.19. Más de una perturbación estática.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

17

a

a’

f1

f2

f

Figura 2.20. Más de una perturbación estática.

Se producen en implementaciones con más de dos niveles, y si concurren a una compuerta

las señales y sus complementos por más de dos vías con retardos diferentes.

Si denominamos f a la señal de salida, y A a la señal de entrada, se tiene que:

f = (A+A’)(A+A’)

La perturbación de más de un pulso también se podría definir como estática, en el sentido

que un valor lógico que debe permanecer sin cambios (estacionario o estático), cambia el valor

una o más veces, y en forma momentánea, para finalmente retomar el valor inicial. En algunos

textos, estas perturbaciones son clasificadas como dinámicas.

2.6.5.3. Perturbaciones dinámicas.

Si la señal de salida cambia de valor lógico, es decir, de 0 a 1 o viceversa, y durante el

cambio ocurren perturbaciones se dice que ésta es dinámica.

Figura 2.21. Perturbaciones dinámicas.

La red de la Figura 2.22 muestra una perturbación dinámica, al cambiar la variable A de

entrada de 1 a 0, y la salida de 0 a 1. Con B=1, C=1 y D=0, se tiene que: f = (A’ +A)(A’) y las

señales concurren al AND de salida a través de tres vías con diferentes retardos. La señal f1,

tiene una perturbación estática en cero, en el canto de bajada de A; si el cambio f 1 se produce

después del cambio de f2, por ser su vía de propagación más lenta, la señal f, presentará una

oscilación: primero pasa a 1, luego a 0 y finalmente a 1.

Se aprecia que f, cambia momentáneamente a 0, luego vuelve a tomar valor 1; para

finalmente tomar valor estable 1.

Resumiendo se puede decir que una perturbación es dinámica si ocurre en una conmutación

de la salida. Se espera una sola transición de la salida y se producen oscilaciones de ésta.

Profesor Leopoldo Silva Bijit

13-04-2010

18

Sistemas Digitales

En un diseño en dos niveles, no se producen perturbaciones dinámicas. En una red

multinivel, tampoco se producen perturbaciones dinámicas si el diseño se realiza eliminando las

perturbaciones estáticas.

A

B

f1

A’

C

f

A’

f2

D

Figura 2.22. Red con perturbación dinámica.

A

A’

f1

f

Figura 2.23. Perturbación dinámica.

El caso dual del anterior, se produce para una red combinacional en la que se produzca en la

salida: f=AA’ + A’.

2.6.5.4. Carreras aleatorias de las entradas. Perturbación de la función.

En redes combinacionales también pueden producirse perturbaciones si varias de las entradas

tienen cambios casi simultáneos.

En el mapa de la función f, de la Figura 2.24, si la función cambia de:

f(0, 0, 0, 0) a f(0, 1, 0, 1)

debería permanecer en cero. Sin embargo si no se produce el cambio simultáneo de B y D, se

tendrán dos situaciones posibles:

Si B cambia primero, se tendrá, que la salida toma los valores:

f(0, 0, 0, 0) , f(0, 1, 0, 0) , f(0, 1, 0, 1)

Si D cambia primero, la salida toma los valores:

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

19

f(0, 0, 0, 0) , f(0, 0, 0, 1) , f(0, 1, 0, 1)

En ambos casos la función pasa momentáneamente por 1.

AB

00

CD

01

0

1

11

12

4

00

0

01

1

11

0

3

1

7

0

10

1

2

0

6

1

1

0

0

13

5

1

15

14

10

0

0

1

0

8

9

11

10

f(A, B, C, D)

Figura 2.24. Función con perturbación por carreras.

Una forma de controlar las carreras de las entradas es la habilitación del conjunto durante un

breve lapso de tiempo, luego de un tiempo de ocurrido el cambio de las entradas.

A, B, C, D

p

Figura 2.25. Pulso de habilitación.

El pulso de habilitación se denomina strobe, en inglés.

A

B

C

D

p

Figura 2.26. Función con perturbación por carreras.

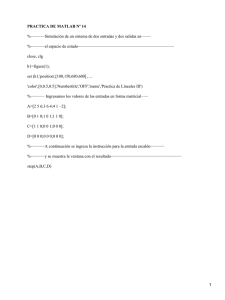

Ejemplo 2.13.

La red combinacional, de la Figura 2.27, es alimentada por un contador que genera las

señales A, B, C y D. Éstas cambian casi al mismo tiempo; es decir, varias tienen cantos que

Profesor Leopoldo Silva Bijit

13-04-2010

20

Sistemas Digitales

ocurren con pequeñas diferencias temporales. Podría decirse que ocurre una carrera entre las

diferentes conmutaciones.

A

B

TP1

C

D

Clock

CP1 Q1

CP2 Q2

74LS93

f

1

MR1

Q3

MR2 1 Q2

CP0

Q1

CP1

Q0

TP2

1

1

Figura 2.27. Carreras en las entradas.

Si se analizan las formas de ondas, cuando A es 1; y B pasa de 0 a 1; y C y D pasan de 1 a 0;

es decir cuando el contador entra en la cuenta 12 en decimal, o 1100 en binario, se produce una

perturbación de 1 en la salida.

A

B

C

D

TP1

TP2

f

Perturbación por carreras de las entradas

Figura 2.28. Perturbación por carreras en las entradas.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

21

Problemas resueltos

Problema 2.1. Diseño multinivel

Un caso más general de implementación en base a compuertas NOR y NAND se ilustra en el

siguiente ejemplo.

Se parte de una implementación multinivel tipo suma de productos, y se emplea la técnica de

doble complementación. El diseño se representa mediante un esquemático.

f

(A

B) C

(D

E) F

La función no está descrita como suma de mintérminos.

En forma inmediata se logra la red en tres niveles, empleando compuertas con fan-in igual a

dos:

A'

B'

D

E

C

F'

f

Figura P2.1. Función en tres niveles.

La implementación basada en compuertas NAND se logra con el método de doble

complementación. En forma gráfica:

A'

B'

D

E

C

F'

f

Figura P2.2. Doble complementación en diseños multinivel.

Aplicando el teorema de De Morgan, se logra una implementación, en base a NAND:

Profesor Leopoldo Silva Bijit

13-04-2010

22

Sistemas Digitales

A

B

C

F'

D'

E'

f

Figura P2.3. Diseño multinivel mediante NANDs.

Nótese que las variables de entrada, que recorren un número impar de compuertas para llegar

a la salida, deben complementarse. Es el caso de A, B, D y E en el ejemplo anterior.

Problema 2.2. Conversión a NANDs en multinivel

El siguiente ejemplo ilustra una conversión a compuertas nand de un esquemático multinivel,

del tipo suma de productos. Debe notarse el tratamiento de la señal interna X, y la necesidad de

agregar un inversor.

Desde un punto de vista analítico: F = A X + X + D; X = B C

Complementando, ambos miembros, se logra: F' = ( A X)' ( X' ) ( D' ) ; X' = (B C)'

A

A

X

B

F

C

X

B

D

C

X'

D'

F’

Figura P2.4 Implementación con NANDs en diseños multinivel.

Problema 2.3. Diseño multinivel. Factorización.

Sea una función de 7 variables.

X=ADF + AEF + BDF + BEF + CDF + CEF + G

Asumiendo que ya está simplificada lógicamente como suma de productos, se observa que

requiere una compuerta OR de 7 entradas (fan-in = 7), también se requieren 6 compuertas AND

de 3 entradas. La expresión está formada por 19 literales. Un diseño directo requiere 25 entradas

(7 al OR de salida y 18 a los ANDs). Esta implementación tiene alto costo y es en dos niveles.

Efectuando una factorización, puede expresarse según:

X = (A + B + C) (D + E) F + G

Para encontrar los factores adecuados pueden ayudar programas de minimización multinivel.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

23

La expresión anterior requiere una compuerta OR de tres entradas, dos ORs de dos entradas,

un AND de 3 entradas. La factorización logra una expresión con 7 literales; y 10 entradas.

Se disminuye el tamaño, pero aumenta el número de niveles.

A

B

C

X

D

E

F

G

Figura P2.5. Diseño en tres niveles.

Problema 2.4. Diferentes formas de implementación.

Pueden escogerse diferentes formas de implementar funciones.

Por ejemplo, para la siguiente tabla de verdad:

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

C

0

1

0

1

0

1

0

1

f

0

1

0

1

0

1

1

0

Figura P2.6. Función de tres variables.

a) Como suma de mínterminos: f = A'B'C+A'BC+AB'C+ABC'

requiere un OR de 4 entradas, y 4 ANDs de 3 entradas. 16 entradas, con 12 literales, en dos

niveles, asumiendo que se dispone de las variables y sus complementos (los literales).

b) Si se escribe como suma de productos mínima:

f = (A'B'C + A'B'C ) +A'BC+AB'C +ABC' por idempotencia, y agrupando se obtiene:

f = A'C+B'C +ABC' forma mínima que requiere un OR de 3 entradas, 2 ANDs de 2

entradas y un AND de 3 entradas. Con 10 entradas y 7 literales. En dos niveles.

c) Factorizando con S = AB, se logra: f = SC'+S'C;

Profesor Leopoldo Silva Bijit

13-04-2010

24

Sistemas Digitales

S

A

B

C'

f

C

Figura P2.7. Empleando un factor común S.

Que requiere: 3 compuertas AND de 2 entradas, un OR de dos entradas y un inversor. Se

tienen 9 entradas y 4 niveles.

d) Empleando compuertas XOR: f = S

A

B

C; con S = AB

S

f

C

Figura P2.8. Empleando compuertas xor.

Implementación que emplea 2 compuertas, dos niveles, 4 entradas. Una de las compuertas es

un OR exclusivo que requiere mayor costo interno.

Problema 2.5. Costos de Implementación.

Dependiendo de la forma de la expresión, las formas mínimas pueden tener costos diferentes,

como se aprecia en el siguiente ejemplo.

La expresión: f = AB + C en su forma canónica de suma de productos requiere: 20 entradas,

5 ANDs de 3 entradas y un OR de 5 entradas. Si se minimiza la suma de productos se requieren:

4 entradas, un AND de 2 entradas y un OR de 2 entradas.

La misma expresión anterior como forma canónica de producto de sumas requiere: 12

entradas, 3 ORs de 3 entradas y un AND de 3 entradas. En su forma minimizada de producto de

sumas requiere: 6 entradas, 2 ORs de 2 entradas y un AND de 2 entradas.

En este caso la suma minimizada de productos lleva a la implementación de menor costo

espacial.

Un análisis de las formas de ondas permite establecer diferencias entre las

implementaciones, ya sea por la producción de perturbaciones o porque tengan retardos

diferentes. Algunas compuertas que tienen mayor número de entradas, tienen mayor retardo.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

25

Problema 2.6.

Expresar como suma de mintérminos usando teorema de expansión. Exprese los mintérminos

mediante números decimales, ordenados en forma ascendente.

Con f(a, b, c, d) = a + b’ c

Solución:

Para el primer término se tiene la siguiente expansión:

a = ab + ab’ = abc + abc’ + ab’c + ab’c’

a = abcd + abcd’ + abc’d + abc’d’ + ab’cd + ab’cd’ + ab’c’d + ab’c’d’

a = m(15, 14, 13, 12, 11, 10, 9, 8)

Para el segundo término, la expansión resulta:

b’c = ab’c + a’b’c = ab’cd + ab’cd’ + a’b’cd + a’b’cd’ = m( 11, 10, 3, 2)

Entonces: f(a, b, c, d) = m(15, 14, 13, 12, 11, 10, 9, 8) + m( 11, 10, 3, 2)

Como m10 + m10 = m10 por idempotencia, y también: m11 + m11 = m11

Resulta finalmente, ordenando los valores decimales en forma ascendente:

f(a, b, c, d) = a + b’c = m(2, 3, 8, 9, 10, 11, 12, 13, 14, 15)

Problema 2.7.

Se tiene una red combinacional con tres entradas (D2, D1, D0) y ocho salidas: (L7, L6, L5, L4,

L3, L2, L1, L0).

Los tres dígitos binarios pueden leerse en su equivalente decimal (n), considerando que D2

es la cifra más significativa y D0 la menos significativa.

Cuando en la entrada se tiene el número n: la salida Ln está baja (0 lógico) y el resto de las

salidas están altas (1 lógico).

D2

D1

D0

L7

L6

...

L1

L0

Figura P2.9 Entradas y salidas Problema 2.7.

Determinar:

a) Tabla de verdad.

b) Expresión lógica mínima para L5 como suma de productos, efectuando reducciones

algebraicas.

c) Expresión lógica mínima para L5 como producto de sumas, efectuando reducciones

algebraicas.

Solución.

Profesor Leopoldo Silva Bijit

13-04-2010

26

Sistemas Digitales

a) La tabla de verdad para las ocho salidas:

D2

0

0

0

0

1

1

1

1

D1

0

0

1

1

0

0

1

1

D0

0

1

0

1

0

1

0

1

L7

1

1

1

1

1

1

1

0

L6

1

1

1

1

1

1

0

1

L5

1

1

1

1

1

0

1

1

L4

1

1

1

1

0

1

1

1

L3

1

1

1

0

1

1

1

1

L2

1

1

0

1

1

1

1

1

L1

1

0

1

1

1

1

1

1

L0

0

1

1

1

1

1

1

1

Figura P2.10 Tabla de verdad Problema 2.7.

b) De la tabla, expresando como suma de mintérminos:

L5 = m(0, 1, 2, 3, 4, 6, 7)

L5 = m0+m1+m2+m3+m4+m6+m7

L5 = m0+m0+m1+m2+m2+m2+m3+m3+m4+m6+m6+m7 Por idempotencia. T8.

L5 = (m0+m2+m4+m6) + (m0+m1+m2+m3) + (m2+m3+m6+m7) Por conmutación. P4.

Aplicando repetidamente fusión: T14

m(0, 2, 4, 6) = (D2’D1’D0’ + D2’D1D0’) +(D2D1’D0’ + D2D1D0’)

= D2’D0’ + D2D0’ = D0’

m(0, 1, 2, 3) = (D2’D1’D0’ + D2’D1’D0) +(D2’D1D0’ + D2’D1D0)

= D2’D1’ + D2’D1 = D2’

m(2, 3, 6, 7) = (D2’D1D0’ + D2’D1D0) +(D2D1D0’ + D2D1D0)

= D2’D1 + D2D1 = D1

Resulta finalmente:

L5 = D2’ + D1 + D0’

c) De la tabla, expresando como producto de maxtérminos:

Debido a que la expresión está formada por un solo maxtérmino, no es necesario minimizar:

L5 = M5 = D2’ + D1 + D0’

En este caso, ambos diseños resultan de igual complejidad (y con la misma expresión).

Problema 2.8.

Se tiene la función:

f(a, b, c) =

M(1,2,3,6) +

m(5, 7)

a) Determinar la tabla de verdad.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

27

b) Expresión lógica mínima para f como suma de productos.

c) Expresión lógica mínima para f como producto de sumas.

Solución:

a) La tabla de verdad para f, resulta de la suma lógica de las columnas asociadas al producto

de maxtérminos y a la suma de mintérminos. Con n el código decimal para el mintérmino.

a

0

0

0

0

1

1

1

1

b

0

0

1

1

0

0

1

1

c

0

1

0

1

0

1

0

1

M(1,2,3,6)

1

0

0

0

1

1

0

1

m(5, 7)

0

0

0

0

0

1

0

1

f

1

0

0

0

1

1

0

1

n

0

1

2

3

4

5

6

7

Figura P2.11 Tabla de verdad Problema 2.8.

b) Expresando f como suma de mintérminos, se obtiene: f = m(0, 4, 5, 7)

f = (a’b’c’ + ab’c’ ) + (ab’c + abc ) = b’c’ + ac Aplicando T14.

c1) Expresando f como producto de maxtérminos:

Se tiene: f(a, b, c) = M(1,2,3,6) = M1 M3 M2 M6 Por conmutación. P4

f = (a +b +c’)(a +b’ +c’)(a +b’ +c)(a’ +b’ +c) Por definición y Aplicando fusión. T14.

f = (a + c’) (b’ + c)

c2) Alternativamente, Describiendo el complemento de la función f, como suma de

mintérminos: f ’ = m(1, 2, 3, 6) = m1 +m3 + m2 +m6 Por conmutación. P4

f ’ = a’b’c + a’bc + a’bc’ + abc’ Por fusión. T14

Se obtiene la ecuación de polaridad inversa:

f ’ = a’c + bc’ Complementando y aplicando Involución en el lado izquierdo y De Morgan

en la expresión de la derecha, se obtiene igual resultado que en c1):

f = (a + c’)(b’ +c)

Problema 2.9.

Se tiene la función:

f(a, b, c, d) = ( a

b)

c

a) Determinar la tabla de verdad.

b) Expresar como suma de mintérminos.

c) Expresar como producto de maxtérminos.

Solución:

Profesor Leopoldo Silva Bijit

13-04-2010

28

Sistemas Digitales

a) Planteando tablas de verdad para el OR exclusivo de a y b, y empleando esta columna con

la de la variable c, se obtiene la columna para la función f. Con n el equivalente decimal del

código del mintérmino:

a

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

b

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

c

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

d a

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

b (a

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

b)

0

0

1

1

1

1

0

0

1

1

0

0

0

0

1

1

c n

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Figura P2.12 Tabla de verdad Problema 2.9.

b) Leyendo los mintérminos directamente de la tabla, se logra:

f = m(2, 3, 4, 5, 8, 9, 14, 15)

c) Leyendo los maxtérminos directamente de la tabla, se logra:

f(a, b, c, d) =

M(0, 1, 6, 7, 10, 11, 12, 13)

Otro desarrollo:

Se tiene por definición:

a b = ab’ +a’ b

Luego: ( a b ) c = (ab’ +a’ b)c’ + (ab’ +a’ b)’c = ab’c’ +a’bc’ + ab’c +a’b’c Por P6.

f = ab’c’d +ab’c’d’ + a’bc’d + a’bc’d’ + ab’cd + ab’cd’ + a’b’cd + a’b’cd’ por T14.

f = m9 + m8 + m5 + m4 + m11 + m10 + m3 + m2

Conmutando se obtiene igual resultado que el anterior.

Los números de los maxtérminos son los números de los mintérminos que no están

presentes, en la expresión anterior. Con esta información puede escribirse la tabla de verdad.

Problema 2.10.

Para una función booleana de 3 variables A, B, C:

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

29

f(A,B,C) = m(2,3,5,7)

a) Determinar la tabla de verdad para f.

b) Expresar f ' como producto de maxtérminos. Justificar la respuesta.

c) Expresión booleana, para f, con menos literales. Justificar la respuesta.

Solución.

a) m2 = A'BC' ; m3 = A'BC ;m5 = AB'C ; m7 = ABC

Los unos de f están asociados a los mintérminos presentes. El mintérmino 2 en decimal

equivale a la combinación de valores 010 de las variables ABC, y por lo tanto tendrá asociado

un uno en la tabla de verdad de la función.

Resulta entonces:

ABC

000

001

010

011

100

101

110

111

f

0

0

1

1

0

1

0

1

f'

1

1

0

0

1

0

1

0

Código decimal

0

1

2

3

4

5

6

7

Figura P2.13 Tabla de verdad Problema 2.10.

b) Los maxtérminos de f ' quedan definidos por los ceros de su tabla de verdad. Para A=0,

B=1 y C=0 se tiene que (A + B' +C) genera el cero en el renglón respectivo de f '.

Entonces: f ' = (A+B' +C)(A+B'+C')(A'+B+C')(A'+B'+C')

Codificando los maxtérminos en binario, se logra: f ' = M010 + M011 + M101 +M111

En decimal: f ' = M2 M3 M5 M7

Otro desarrollo:

A partir de f = (m2+m3+m5+m7), negando ambos miembros se logra:

f ' = (m2+m3+m5+m7)' ; P2

= m2' m3' m5' m7' ; T12 De Morgan

=

M ( 2,3,5,7) ;Con mi' = Mi

c) f(A,B,C) = m(2,3,5,7)

= A'BC'+AB'C'+AB'C+ ABC

= A'C'B+AC'B'+ACB'+ ACB

= A'C'(B+B') + AC(B'+B)

= A'C'(1) +AC(1)

= A'C'+AC

; definición de mintérminos.

; P4 Conmutatividad.

; P6 Distributividad.

; P7 Complemento único.

; P3 Elementos únicos.

Problema 2.11.

Se tiene un número binario de cuatro bits:

Profesor Leopoldo Silva Bijit

13-04-2010

30

Sistemas Digitales

A3A2A1A0, donde A3 es la cifra más significativa, sea n el equivalente decimal de este

número.

Diseñar un sistema que acepte a n como entrada y que produzca en la salida el equivalente

binario del número decimal: ( n*4 +1).

Solución.

El mayor n que puede escribirse con cuatro bits es 15, por lo tanto la salida mayor será 61, lo

cual requiere 6 cifras binarias para representarla. Sean éstas: S5S4S3S2S1S0.

La siguiente tabla de verdad ilustra la situación:

n

A3A2A1A0 n*4 +1 S5S4S3S2S1S0

0

0000

1

000001

1

0001

5

000101

2

0010

9

001001

3

0011

13

001101

4

0100

17

010001

5

0101

21

010101

6

0110

25

011001

7

0111

29

011101

8

1000

33

100001

9

1001

37

100101

10

1010

41

101001

11

1011

45

101101

12

1100

49

110001

13

1101

53

110101

14

1110

57

111001

15

1111

61

111101

Figura P2.14 Tabla de verdad Problema 2.11.

Observando la tabla, se determina que S1= 0 y S0 = 1 son constantes, y que:

S5 = A3, S4 = A2, S3 = A1, y S2 = A0

El diseño mínimo no requiere compuertas, y se muestra a continuación:

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

31

A3

S5

A2

A1

A0

S4

S3

S2

VCC

S1

S0

S1

tierra

S0

VCC

Figura P2.15 Esquemático Problema 2.11.

A la derecha se muestra un diseño donde las señales S1 y S0 son salidas de compuertas.

Problema 2.12.

Se tiene un circuito digital de 4 entradas (A, B, C, D) y cuatro salidas (f1, f2, f3, f4).

a) Determinar como suma de mintérminos, la función f1 que es verdadera cuando exactamente

dos de las entradas sean verdaderas.

b) Determinar como producto de maxtérminos, la función f2 que es verdadera cuando

exactamente tres de las entradas sean verdaderas.

c) Determinar mediante un circuito lógico en base a AND, OR y NOT, la función f3, que es

verdadera cuando exactamente cuatro de las entradas sean verdaderas.

d) Determinar mediante una expresión booleana, la función f4, que es verdadera cuando

exactamente cuatro de las entradas sean falsas.

Solución.

Se tienen las siguientes tablas de verdad.

Profesor Leopoldo Silva Bijit

13-04-2010

32

Sistemas Digitales

A

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

B

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

C

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

D

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

f1

0

0

0

1

0

1

1

0

0

1

1

0

1

0

0

0

f2

0

0

0

0

0

0

0

1

0

0

0

1

0

1

1

0

f3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

f4 Código

1

0

0

1

0

2

0

3

0

4

0

5

0

6

0

7

0

8

0

9

0

10

0

11

0

12

0

13

0

14

0

15

Figura P2.16 Tabla de verdad Problema 2.12.

Entonces:

f1 = m(3, 5, 6, 9, 10, 12)

f2 = M(0, 1, 2, 3, 4, 5, 6, 8, 9, 10, 12, 15)

f3 = m(15) = ABCD

A

B

C

D

f3

f4 = m(0) = A'B'C'D'

Ejercicios propuestos.

Ejemplo 2.1.

Verificar las relaciones:

f

m(2, 6)

M (0,1, 3, 4, 5, 7)

f

m(0,1, 3, 4, 5, 7)

M (2, 6)

Ejemplo 2.2.

Con f(a, b, c, d) = ab’d + c’(b d)’ + m9 + M’13

a) Expresar como suma de mintérminos.

b) Expresar como producto de maxtérminos.

c) Minimizar como suma de productos empleando teoremas.

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

33

Ejemplo 2.3.

Para la función:

f(A, B, C, D) = ((A + B)C+B’)D + m13m2 +m5 + M2m13

Determinar:

a) Formas canónicas.

b) Minimizar, indicando número de entradas.

c) 2-cubos que contienen a m7

d) Agregue un mintérmino (a elección) tal que la expresión se simplifique.

Ejemplo 2.4.

Para la función:

f(A, B, C, D) = ((A + B)C+B’)D + m13m2 +m13 + M2m13

Determinar:

a) Formas canónicas.

b) Minimizar, indicando número de entradas.

c) 2-cubos que contienen a m7

d) Agregue un mintérmino (a elección) tal que la expresión se simplifique.

Ejemplo 2.5.

Para un diseño libre de perturbaciones, de la función:

f ( w, x, y, z )

xy ' w ' y

que elección realizaría:

a) f ( w, x, y, z ) xy ' w ' y w ' xz

b) f ( w, x, y, z ) xy ' w ' y w ' x

Ejemplo 2.6.

Eliminar las perturbaciones estáticas de la función:

f (v, w, x, y, z ) v ' wz ' w ' x ' z xz vwy '

Profesor Leopoldo Silva Bijit

13-04-2010

34

Sistemas Digitales

Índice general.

CAPÍTULO 2.........................................................................................................................................1

SÍNTESIS EN DOS NIVELES ............................................................................................................1

2.1. FORMAS DE FUNCIONES. ...............................................................................................................1

2.2. MINTÉRMINOS ..............................................................................................................................2

Ejemplo 2.1. Definición de mintérmino ..........................................................................................2

Ejemplo 2.2. Suma de mintérminos ................................................................................................3

2.3. MAXTÉRMINO. ..............................................................................................................................3

Ejemplo 2.3. Definición de maxtérmino. ........................................................................................4

Ejemplo 2.4. Producto de maxtérminos .........................................................................................4

Relaciones ......................................................................................................................................5

Ejemplo 2.5. De suma de mintérminos a productoria de maxtérminos. .........................................5

2.4. EXPANSIÓN A FORMAS CANÓNICAS...............................................................................................6

2.4.1. Expansión de suma de productos .........................................................................................6

Ejemplo 2.7. Expansión a mintérminos. .................................................................................................... 6

2.4.2. Expansión de productos de sumas ........................................................................................6

Ejemplo 2.8. Expansión a maxtérminos ..................................................................................................... 6

2.5. SÍNTESIS DE LAS FORMAS..............................................................................................................7

2.5.1. Suma de productos ...............................................................................................................7

Ejemplo 2.9. OR de ANDs ........................................................................................................................ 7

Ejemplo 2.10. Dos niveles de NANDs ....................................................................................................... 7

2.5.2. Producto de sumas ...............................................................................................................8

2.5.3. Conversión de producto de sumas a suma de productos. Cambio de lógica. .......................9

2.6. DISEÑO LÓGICO ..........................................................................................................................10

2.6.1. Fan-in. Fan out...................................................................................................................10

2.6.2. Observaciones sobre la forma Producto de Sumas. ...........................................................11

2.6.3. Observaciones sobre la forma Suma de Productos. ...........................................................11

2.6.4. Observaciones sobre las diferentes formas de diseño. .......................................................12

2.6.5. Perturbaciones. Diseños con riesgos. ................................................................................12

2.6.5.1. Perturbación estática en uno........................................................................................................ 13

2.6.5.2. Perturbación estática en cero. ...................................................................................................... 14

Ejemplo 2.11. Análisis de perturbaciones. ............................................................................................... 15

Ejemplo 2.12. ........................................................................................................................................... 16

2.6.5.3. Perturbaciones dinámicas. ........................................................................................................... 17

2.6.5.4. Carreras aleatorias de las entradas. Perturbación de la función. .................................................. 18

Ejemplo 2.13. ...................................................................................................................................... 19

PROBLEMAS RESUELTOS ....................................................................................................................21

Problema 2.1. Diseño multinivel ..................................................................................................21

Problema 2.2. Conversión a NANDs en multinivel ......................................................................22

Problema 2.3. Diseño multinivel. Factorización. .........................................................................22

Problema 2.4. Diferentes formas de implementación. .................................................................23

Problema 2.5. Costos de Implementación. ...................................................................................24

Problema 2.6. ...............................................................................................................................25

Problema 2.7. ...............................................................................................................................25

Problema 2.8. ...............................................................................................................................26

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

35

Problema 2.9. .............................................................................................................................. 27

Problema 2.10. ............................................................................................................................ 28

Problema 2.11. ............................................................................................................................ 29

Problema 2.12. ............................................................................................................................ 31

EJERCICIOS PROPUESTOS................................................................................................................... 32

Ejemplo 2.1. ................................................................................................................................. 32

Ejemplo 2.2. ................................................................................................................................. 32

Ejemplo 2.3. ................................................................................................................................. 33

Ejemplo 2.4. ................................................................................................................................. 33

Ejemplo 2.5. ................................................................................................................................. 33

Ejemplo 2.6. ................................................................................................................................. 33

ÍNDICE GENERAL. .............................................................................................................................. 34

ÍNDICE DE FIGURAS........................................................................................................................... 36

Profesor Leopoldo Silva Bijit

13-04-2010

36

Sistemas Digitales

Índice de Figuras

Figura 2.1 Tablas de verdad de algunos Mintérminos................................................................... 3

Figura 2.2. Tablas de verdad de algunos Maxtérminos. ............................................................... 4

Figura 2.3. Suma de productos en dos niveles. ............................................................................ 7

Figura 2.4. Suma de productos mediante NANDs. ...................................................................... 8

Figura 2.5. Doble complementación............................................................................................. 8

Figura 2.6. Equivalencia gráfica del teorema de De Morgan. ...................................................... 8

Figura 2.7. Producto de sumas en dos niveles. ............................................................................. 8

Figura 2.8. Suma de productos mediante NORs. ......................................................................... 9

Figura 2.9. Visualización esquemática del teorema de De Morgan. ............................................ 9

Figura 2.10. De producto de sumas a Suma de productos. ........................................................... 9

Figura 2.11. Complementos de las entradas y salidas. ............................................................... 10

Figura 2.12. AND de columnas. ................................................................................................. 11

Figura 2.13. OR de columnas. .................................................................................................... 11

Figura 2.14. Perturbación en red combinacional ......................................................................... 13

Figura 2.15. Eliminación de perturbación en uno........................................................................ 13

Figura 2.15a. Perturbación en cero. ............................................................................................. 14

Figura 2.15b. Eliminación de perturbación en cero. .................................................................... 14

Figura 2.16. Falsos ceros y unos.................................................................................................. 15

Figura 2.17. Análisis de perturbaciones. ..................................................................................... 15

Figura 2.18. Visualización de perturbaciones en mapas.............................................................. 16

Figura 2.19. Más de una perturbación estática. ........................................................................... 16

Figura 2.20. Más de una perturbación estática. ........................................................................... 17

Figura 2.21. Perturbaciones dinámicas. ....................................................................................... 17

Figura 2.22. Red con perturbación dinámica. .............................................................................. 18

Figura 2.23. Perturbación dinámica............................................................................................. 18

Figura 2.24. Función con perturbación por carreras. ................................................................... 19

Figura 2.25. Pulso de habilitación. .............................................................................................. 19

Figura 2.26. Función con perturbación por carreras. ................................................................... 19

Figura 2.27. Carreras en las entradas. .......................................................................................... 20

Figura 2.28. Perturbación por carreras en las entradas. ............................................................... 20

Figura P2.1. Función en tres niveles........................................................................................... 21

Figura P2.2. Doble complementación en diseños multinivel. .................................................... 21

Figura P2.3. Diseño multinivel mediante NANDs. .................................................................... 22

Figura P2.4 Implementación con NANDs en diseños multinivel............................................... 22

Figura P2.5. Diseño en tres niveles. ........................................................................................... 23

Figura P2.6. Función de tres variables. ...................................................................................... 23

Figura P2.7. Empleando un factor común S. .............................................................................. 24

Figura P2.8. Empleando compuertas xor.................................................................................... 24

Figura P2.9 Entradas y salidas Problema 2.7. ............................................................................ 25

Figura P2.10 Tabla de verdad Problema 2.7............................................................................... 26

Figura P2.11 Tabla de verdad Problema 2.8............................................................................... 27

Figura P2.12 Tabla de verdad Problema 2.9............................................................................... 28

Figura P2.13 Tabla de verdad Problema 2.10............................................................................. 29

Profesor Leopoldo Silva Bijit

13-04-2010

Capítulo 2. Síntesis en dos niveles

37

Figura P2.14 Tabla de verdad Problema 2.11. ........................................................................... 30

Figura P2.15 Esquemático Problema 2.11. ................................................................................ 31

Figura P2.16 Tabla de verdad Problema 2.12. ........................................................................... 32

Profesor Leopoldo Silva Bijit

13-04-2010

Anuncio

Documentos relacionados

Descargar

Anuncio

Añadir este documento a la recogida (s)

Puede agregar este documento a su colección de estudio (s)

Iniciar sesión Disponible sólo para usuarios autorizadosAñadir a este documento guardado

Puede agregar este documento a su lista guardada

Iniciar sesión Disponible sólo para usuarios autorizados