Introducción: Muestreo y Cuantización de Señales Contínuas

Anuncio

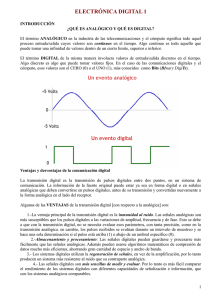

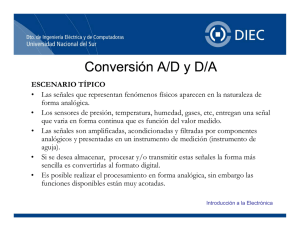

25/11/2003 Introducción: Los avances en el procesamiento digital de las últimas décadas motivan el hecho de poder reducir señales continuas a muestras discretas en el dominio de tiempo discreto. Muestreo y Cuantización de Señales Contínuas La operación que permite la transformación de una señal en tiempo continuo a una señal en tiempo discreto es comúnmente llamada muestreo (sampling). Ello consiste en tomar muestras del valor de la señal en tiempo continuo cada instantes de tiempo múltiplo de T, llamado intervalo de muestreo. Siendo, de este modo F=1/T la llamada frecuencia de muestreo. Si la señal en tiempo continuo es de banda limitada (diremos que su espectro se encuentra entre − ω M < X ( jω ) < +ω M ), ésta puede ser representada unívocamente por medio de sus muestras siempre que la frecuencia de muestreo exceda 2ω M . Valor comúnmente conocido como frecuencia de Nyquist. La arimétrica del procesamiento interno de los sistemas digitales impone la cuantización de los valores muestreados de la señal analógica en valores digitales discretos. De acuerdo a la cantidad de bits (n) del código digital que se esté utilizando, el rango completo de la señal analógica puede ser dividido en 2n niveles equi-espaciados llamados niveles de cuantización. La cuantización permite decidir cual código digital es el más adecuado para la representación del valor continuo de la señal muestreada. Siendo V fs la amplitud completa del rango de tensión de entrada, ∆ = V fs 2 n es llamado intervalo de cuantización, y el error que se comete durante el proceso de cuantización estará comprendido entre − ∆ 2 < ε Q < + ∆ 2 . El error de cuantización es inherente a cualquier proceso de conversión A/D, asi ε Q tiende a cero cuando n tiende a infinito. 1-1 25/11/2003 Razones que motivan la elección de Conversores A/D Pipeline El muestreo y la cuantización de señales a altas frecuencias de muestreo con bajo consumo es una meta muy importante para muchas aplicaciones, tales como dispositivos de video portátiles, dispositivos de comunicación, transductores de redes inalámbricas, canales de lectura de dispositivos de almacenamiento magnéticos de datos digitales, y muchas otras aplicaciones. Con energía limitada en baterías de tamaño razonable, necesitamos que en nuestros circuitos integrados la disipación de energía sea mínima. La gran mayoría de los sistemas de comunicación actuales utilizan procesamiento digital de señales (DSP) para resolver la información transmitida. De modo que entre el la señal analógica recibida y el sistema de procesamiento digital se necesita una interfaz analógico-digital. Esta interfaz permite la digitalización de la forma de onda recibida sujeta a la velocidad de muestreo del sistema. Como parte del sistema de comunicación, la restricción del bajo consumo, mencionado anteriormente, la interfaz A/D también deberá ser de bajo consumo. La tendencia a incrementar el nivel de integración de los circuitos integrados nos tiene obligados a que el conversor A/D resida en el mismo silicio con grandes circuitos DSP. El hecho de compartir la misma fuente de alimentación entre el conversor A/D y el circuito digital, reduce el costo de tener que agregar conversores DC-DC extras para generar múltiples fuentes de alimentación. De modo que, es deseable que cada conversor A/D opere con la misma fuente de alimentación que el circuito digital. Con el rápido avance de la Supervía de la Información de hoy en día, grandes cantidades de datos son almacenados en dispositivos de almacenamiento y son accedidos frecuentemente. Con el objeto de transmitir grandes cantidades de datos en cortos períodos de tiempo, se necesita que nuestros dispositivos de almacenamiento tengan grandes velocidades de transferencia. Esto se traduce directamente en altas velocidades de conversión en los canales de lectura de dispositivos magnéticos, como es en el caso de discos rígidos de última generación. En el mercado comercial actual es muy común encontrar aplicaciones que requieren tasas de transferencia de 100MS/s para resoluciones de 6-8bits. También con el objeto de lograr la mayor velocidad de transferencia en aplicaciones multimedia, se necesitan conversores A/D veloces que lo permitan. 2-2 25/11/2003 Los diseños tradicionales de conversores que brindan la máxima velocidad de conversión utilizan arquitecturas flash. Logrando la mayor velocidad de salida de datos (throughput) con el menor tiempo de retardo (latencia), se necesita una gran superficie para su implementación en tanto crece exponencialmente con la cantidad de bits. Los conversores A/D Pipeline utilizan interiormente pequeños conversores flash en cada una de sus etapas, alcanzando los mismos valores de throughput a expensas de un mayor tiempo de retardo, pero la superficie necesaria para su implementación es mucho menor para la misma cantidad de bits. En ciertas aplicaciones donde se requiere mediana – alta resolución y no hay, ó bién no es de importancia la realimentación (dado que el tiempo de retardo crece con el numero de etapas) es ventajoso utilizar el tipo de arquitectura de conversión A/D Pipeline. 3-3