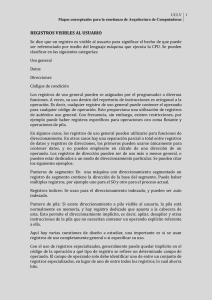

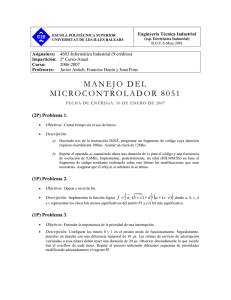

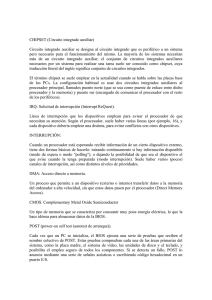

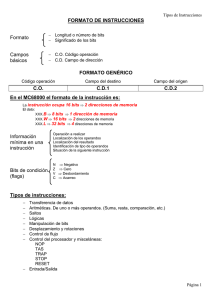

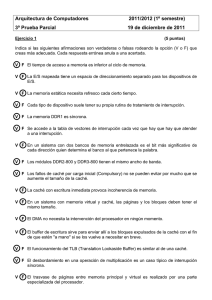

Fundamentos de computadores

Anuncio