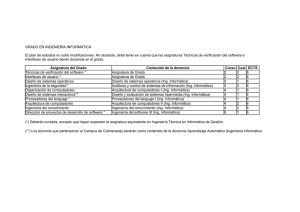

Perspectiva - Departamento de Arquitectura y Tecnología de los

Anuncio

Perspectiva Histórica de la

Ingeniería de Computadores

Tendencias en Ingeniería

g

de Computadores

p

Centro Mediterráneo. Almuñécar, 2013

Julio Ortega Lopera

TOP500, Junio 2013

Tianhe-2 (MilkyWay-2)

Procesador: Intel Xeon E5

E5-2692

2692 (2.2

(2 2 GHz

211.2 GFLOPS pico / procesador)

Nº de Procesadores (cores): 3120000

Memoria Principal: 1024 Tbytes

(17808 KW)

Rmax=33.86 PFLOPS (Rpico=54.9 PFLOPS)

ENIAC (1946)

Nº de Procesadores: 1 (100 KHz, 174 KW)

5000 sumas/s 357 mult/s 35 div/s

Mejora en un factor de 6x1012 en algo más de

65 años (crecimiento exponencial,

exponencial alrededor

del 55% anual)

Reloj “solo” 22000 (2.2x104) veces más rápido

y 525.9x10

525 9x10-12 J/flop vs

vs. 34

34.8

8 J/suma

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué objetivos y factores determinan la evolución de

los computadores?

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Objetivos de diseño: Aumento de Prestaciones

J. C. McCallum http://www.jcmit.com/index.htm

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Objetivos de diseño: Aumento de Prestaciones

TOP500

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Objetivos de diseño: Reducción de coste

J C.

J.

C McCallum http://www.jcmit.com/index.htm

http://www jcmit com/index htm

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Objetivos de Diseño de Computadores

Coste (“Cost driven”)

Más velocidad

Menos coste

Eficiencia

energética

Aumentar la aplicabilidad:

Tiempo

(“Performance driven”)

• Calidad de la solución

obtenida en un tiempo

dado

• Acceso a dispositivos de

cómputo asequibles

(Smith, R.E., Annals Hist. Comput., 1989)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Objetivos de diseño: Eficiencia Energética

http://www green500 org/

http://www.green500.org/

Nº1 TOP500

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Factores en la evolución de los

computadores

Posibilidades

Ley de Amdahl

(1967)

Ley de Moore

(1965)

Capacidades

p

Prestaciones

Promueve

Tecnología

Posibilidades

Ingeniería de

p

Computadores

Aplicaciones

Selección

Demanda

Posibilidades

Restricciones

Restricciones

“No hay ninguna razón por

la que alguien pueda

querer un computador en

casa” (1977, directivo de

DEC)

Generación

Factores

Económicos

Adaptada de Vajapeyam, S.;

Valero, M., IEEE Computer 2001

Inicialmente: Ley de Grosch (40’s, 1953)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de la Economía: Ley de Grosch

El coste de la computación por unidad de prestaciones, C/W,

decrece con la raíz cuadrada de las prestaciones, W :

Para reducir diez veces el coste relativo hay

yq

que aumentar la

velocidad cien veces (40’s, 1953, 1967, no se aplica desde la

introducción del transistor y los CI)

Unanimidad sobre la centralización de

la computación: los computadores

pequeños no son competitivos, lo

grande es mejor porque ahorra dinero

(economía de escala)

Este paradigma de la economía de

escala era el dominante en los 50 y 60

Predicción de T.J. Watson, de IBM,

sobre que no habría demanda para

más de cinco computadores

(grandes)

C

1

f

W

W

Si las prestaciones de un computador

se cuadruplican, su coste por unidad

de p

prestaciones se reduce a la mitad:

cuanto más potente es un

computador sería más costoso,

pero mejor

p

j es la relación

coste/prestaciones (economía de

escala)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de la tecnología: Ley de Moore

1965:

El término Ley de Moore

se debe a Carver Mead

(hacia 1970)

La complejidad del número de componentes semiconductores

de coste mínimo se dobla cada año

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de la tecnología: Ley de Moore

x2 cada 18 meses

1965:

x2 cada

24 de

meses

El término

Ley

Moore

se debe a Carver Mead

(hacia 1970)

La complejidad del número de componentes semiconductores

de coste mínimo se dobla cada año

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de la tecnología: Ley de Moore

x2 cada 18 meses

x2 cada 18 meses

1965:

x2 cada

24 de

meses

El término

Ley

Moore

se debe a Carver Mead

(hacia 1970)

La complejidad del número de componentes

x2 cada 24 meses semiconductores

de coste mínimo se dobla cada año

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de la tecnología: Ley de Moore

T e cn o lo g ia (m icr a s )

C a p a cid a d D R A M (M b its )

03

0,3

1

1,E+06

06

0,25

1,E+05

0,2

1,E+04

DRAM

0,15

M axima

1,E+03

uP

0,1

Prod.

1,E+02

0 05

0,05

0

1995

2000

2005

2010

2015

0 25 0 05

0.25-0.05

1 E+01

1,E+01

0.20-0.03

1,E+00

256M-256G

1995

T r a n s is to r e s / C h ip (M illo n e s )

2000

2005

2010

2015

64M-64G

64M

- 64G

x2 cada 18 meses

F r e c u e n cia M á x im a (M H z)

1,E+04

x2 cada 18 meses

4,E+03

3,E+03

1,E+03

3,E+03

2,E+03

1,E+02

Trans/CI

Frec(M ax)

2,E+03

1,E+03

,

1 E+01

1,E+01

11M-1,4B

1,E+00

5,E+02

750M-3G

0,E+00

1995

2000

2005

1965:

2010

2015

1995

2000

2005

2010

2015

x2 cada

24 de

meses

El término

Ley

Moore

se debe a Carver Mead

(hacia 1970)

La complejidad del número de componentes

x2 cada 24 meses semiconductores

de coste mínimo se dobla cada año

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Influencia de las

A li

Aplicaciones:

i

Ley

L de

d Amdahl

A d hl

T1

1/f

f×T1

(1-f)×T1

1-f

f×T1

p

T1

T

1

S

Tp 1 f (p 1)

Tp ≥

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

(1-f)×T1/p

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

Tecnología:

Componentes más rápidos y fiables, y de menor

consumo (más transistores y más rápidos)

Factores económicos:

Aumentar Prestaciones

Reducir Coste

Rentabilidad / Financiación

Aplicaciones

Características de las aplicaciones más

demandadas (“killer appiclations”)

Arquitectura del Computador:

Mejorar la eficiencia

energética

Aumentar la aplicabilidad

Paralelismo y Localidad (en distintos niveles)

¿Cómo han evolucionado los computadores?

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

“The big picture” (con poca resolución)

60

70

80

Mainframes /

Supercomputadores

90

00

Servidores

Grandes computadores para

aplicaciones de negocios y

científicas de gran volumen.

WWW

Minicomputadores

Aplicaciones científicas

en laboratorios y

pequeñas

p

q

organizaciones

g

Microprocesador

Intel 4004 ((1971))

1971

1

1964

4

REDUCIR

COSTE

Redes

PCs y

Estaciones de

Trabajo

Computadores Empotrados

Rápido

Rá

id crecimiento

i i t (t

(tecnología

l í y

herramientas de diseño): electrónica

digital de altas prestaciones,

videojuegos, teléfonos móviles, tarjetas

inteligentes conmutadores,….

inteligentes,

conmutadores

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Las Generaciones de Computadores (Tecnología)

Primera

1946-54

1946

54

Tubos de vacío

Memorias de líneas

de retardo

ms

Segunda

1955-63

1955

63

Transistores.

Memorias de núcleos de

ferrita

μs

Tercera

1964-70

1964

70

Circuito Integrado (SSI y

MSI)

Memorias de C.I.

ns

Cuarta

19711971

Circuito Integrado (LSI y

VLSI)

Memorias DRAM

ns

Arquitectura

Arq

itect ra

y

Estructura

Aritmética de punto

fijo

Aritmética expo-nen-cial

e po nen cial

Registros índices

Procesadores de E/S

Microprograma-ción

Microprograma

ción

Memorias cachés

Memoria Virtual

Microprocesadores

Microprocesadores.

Arquitecturas RISC y

paralelas

S. Operativos

sin S.O.

Monitores "batch"

Multiprogramación

Multiprocesamiento

S.O. en red

S O distribuidos

S.O.

Computadores

ENIAC (1946)

SSEM Baby (1948)0

EDSAC (1949)

Whirlwind I (1951)1

ERA 1101 (1951)

Ferranti Mark1(1951)2

UNIVAC I (1951)3

IBM 701 (1952)

UNIVAC 1103(1953)4

IBM 704 (1954)

TRADIC (1955)5

IBM 709 (1958)6

EDSAC 2 (1958)microprograma

IBM 7090 (1959)

UNIVAC LARC (1960)7

DEC PDP 1 minic. (1960)8

IBM 7030 Stretch (1961)9

Ferranti Atlas (1962)10

B5000 (1963)11

CDC 6600 (1964)12

IBM S/360 (1964) 13

DEC PDP 8 minic. (1965)

DEC PDP 11 (1970)

ILLIAC IV (1971)

TI-ASC (Vectorial) (1971)

Xerox Alto (1973)14

TI TMS (1974)

Altair 8800 (1975)15

AP-120B (VLIW) (1975)

Cray-1 (1976)16

DEC VAX-11 (1977)17

Apple II (1977)

IBM-PC (1981)

Años

Tecnología

(dispositivos

y período de reloj)

0 Programa

9

1

almacenado en memoria

Primer computador para tiempo real; microprog. (antes del término)

2 Primer computador comercial UK

3 Primer computador comercial USA

4 Interrupciones

5 Primero con transistores

6 Primero con interrupciones y DMA con canales

7 Multiprocesamiento con 2 procesadores y memoria entrelazada

8 Computadores económicos y E/S flexible (minicomputadores)

10

Primer pipeline

Memoria virtual con páginas, multiprogramación, extracod. e interr.

11 Programado en ALGOL

ALGOL, multiprocesamiento (2 proc

proc.),

) prec

prec. CISC

12 Arquitectura LOAD/STORE, Paralelismo ILP con varias UF, prec. RISC

13 Familia de computadores: código compatible, SO similar, distintas impl.

14 Escritorio, GUI (computación personal)

15 Primer computador personal significativo

16 Computador más rápido en modo escalar y vectorial

17 Primera máquina comercial de 32 bits. Paradigma CISC (patrón SPEC)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Las personas

http://awards.acm.org/eckert_mauchly/

g

y

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Sucesión temporal de innovaciones

Ley de Grosch (53)

1er Programa

Almacenado

Baby (48)

Ley de

Amdahl (67)

IBM 701

(52)

UNIVAC I TRADIC

Whirlwind I

(55)

(51)

ENIAC

(46)

Taxonomía de Flynn (72)

Ley de Moore (65)

IBM S360

(64)

PDP-1

(60)

SIMD ILLIAC IV

Vectorial TI-ASC

(71)

PDP-11

(70)

Interrupciones

UNIVAC 1103

(53)

Superescalar

CDC6600 (64)

DMA, Canales

C

E/S

/S

IBM 709 (58)

Memoria

Virtual

Segmentación

(B5000, 61)

S

S-100

Altair (75)

55

ISA

S IBM

PC (81)

S

Sbus

Sun

(89)

S370/85

1ªCache

(68)

Propuestas de

cache no

bloqueante (81)

Propuestas de

cache m

multinivel

ltini el

(88)

AGP

G

Intel

(96)

16b

Itanium

Intel

(01)

HyperTransport

AMD (01)

Gigabit

Ethernet

(98)

EDO

DRAM (94)

Intel

Pentium D

(05)

PCIe

C

Intel

(06)

Infiniband

2Gbps (99)

QPI

Q

Intel

(08)

10 Gigabit

Ethernet

(02)

1ermicro con cache

L2: Pentium Pro

(95)

Propuestas

prefetching

(90)

FP DRAM

(90)

8b

Intel P7

Pentium 4

(00)

Fast Ethernet 100Mbps

Myrinet

y

512Mbps

p

(95)

Infiniband

QDR 40Gbps

p

(08)

1ermicro con

cache L3:

Itanium 2 (03)

DDR SDRAM

(00)

SDRAM

(96)

32b

3ª G

65

PCI

C

Intel

(92)

1ermicro con

cache L1:80486

(89)

Primera DRAM

comercial 1KB

(Intel/IBM, 70)

60

Multibus

(83)

Hipercubos

Cosmic Cube

(81)

Ethernet

10Mbps

p

Xerox (72)

4b

50

SuperSPARC Intel P6

(91)

AMD K5

(95)

Concepto de

Cache (Wilkes)

(65)

Patente memoria

de núcleos

magnéticos (51)

2ª G

Intel

Earth Simulator

IBM Roadrunner

Paragon

SGI Challenge

(02)

(08)

(92)

(90)

NYU

Cray T3D/E

CM5 (91)

Ultracomp.

(95)

(83)

IBM Power 4

( )

(01)

RISC Cheetah

(80) (82)

Intel 4004

(71)

Unibus PDP11

(69)

Mem.Virt.

Páginas

(Atlas,UK)

(62)

Memoria

entrelazada

t l

d

(LARC, 60)

45

Apple II

(77)

Altair 8800

(75)

ARPANET

WAN ((69))

1ª G

WWW CERN (89)

IBM PC

(81)

VLIW AP120B (75)

Pipeline CISC

Stretch B5000

(61)

(63)

Tubo Williams

(CRT) (46-47)

Cray 1

(76)

TOP 500 (Junio, 93)

DDR3 (07)

DDR2 (03)

64b

4ª G

70

75

80

85

90

95

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

05

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

¿Cómo han evolucionado los computadores?

•

Los comienzos

•

Los procesadores

•

Las memorias y los buses

•

Las arquitecturas con varios procesadores

•

L computadores

Los

t d

embebidos

b bid

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los comienzos de la Ingeniería de

Computadores

Durante

u a e la

a 2ª Guerra

Gue a Mundial

u d a se demandan

de a da aplicaciones

ap cac o es cuya

resolución se vio favorecida por el esfuerzo de guerra:

- Cifrado y descifrado de códigos

códigos.

- Cálculo de trayectorias balísticas.

Inglaterra: Máquinas de propósito específico BOMB (electromecánica),

COLOSSUS (electrónica, 1943)

Estados Unidos:

• Atanasoff-Berry Computer ABC (sist. ecuaciones lineales, aritmética

binaria, diseño:1937, operativo: 1942, IEEE Milestone: 1937)

• Máquinas

q

de ERA ((Engineering

g

g Research Associates))

Alemania: Máquinas de Zuse, Z1 (1938, computador mecánico, lógica

Booleana, coma flotante, no fiable)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los comienzos del computador electrónico (I)

ENIAC (1946) Eckert – Mauchly (IEEE Milestone)

Primer computador electrónico fiable de

propósito general

100 KHz, 174 KW, 18000 tubos de vacío

5000 sumas/s 357 mult/s 35 div/s

Memoria de trabajo: 2000 biestables (triodos)

Proyecto EDVAC (Electronic Discrete Variable Automatic Computer):

“First draft of a report on the EDVAC” (von Neumann, 1945)

“Preliminary discussions on the logical design of an Electronic Computing

Instrument” (Burks, Goldstine, von Neumann, Institute for Advanced Studies, IAS,

Princeton,, 1946))

Computador de tipo von Neumann

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los comienzos del computador electrónico (II)

“Preliminary discussions on the

logical design of an Electronic

Computing Instrument”

Instrument (Burks,

Goldstine, von Neumann, IAS,

Princeton, 1946)

Blachman: “A survey of

Automatic Digital Computers”,

1953 ((Dep. Commerce, USA))

Computador

(inicio 50’s)

Programa almacenado (Baby 48, EDSAC 49)

Codificación binaria

Arquitectura aritmética paralela (compromiso

velocidad/complejidad de diseño)

Registros índice (Manchester Mark 1, 49)

Microprogramación (Whirlwind 47, EDSAC2 58)

Tiempo de

suma (μs)

Número de

Tubos

Organización

Tamaño de

Memoria (bits)

Tipo de

memoria

8500 (media)

2695

Serie

393216 (48 KB)

Tambor

EDSAC (1949)

(Cambridge)

1500

4500

Serie

4500

Líneas de

Retardo

Mark 1 (1951)

(Manchester)

1200

250

S i

Serie

10240

CRT

40

6800

Paralela

32768

CRT

ERA 1101 (1951)

Whirlwind (1951)

(MIT)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

El nacimiento de la Ingeniería de Computadores (I)

Los primeros computadores eran sistemas electrónicos

complejos

La complejidad hace necesario un nivel de abstracción por

encima del nivel de circuito eléctrico/electrónico constituido por

elementos idealizados con propiedades lógicas bien definidas:

De tensiones e intensidades se p

pasa a niveles lógicos

g

La Ingeniería de Computadores contempla el diseño del

computador desde sus capacidades funcionales sin tener que

prestar atención a los detalles electrónicos

Se basa en el funcionamiento de bloques de circuito que

implementan un conjunto fundamental de operaciones lógicas

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

El nacimiento de la Ingeniería de Computadores(II)

Los informes:

“First

First draft of a report on the EDVAC”

EDVAC (von Neumann,

Neumann 1945)

“Preliminary discussions on the logical design of an Electronic Computing

Instrument” (Burks, Goldstine, von Neumann, Institute for Advanced Studies,

IAS, Princeton, 1946)

describen el computador en términos de elementos de cómputo

abstractos (en lugar de elementos electrónicos)

Diagrama de bloques de un

computador en un artículo

de A. E. Smith, de 1948:

A partir de él se puede

seguir

i entendiendo

t di d como

funcionan los

computadores actuales

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

¿Cómo han evolucionado los computadores?

•

Los comienzos

•

Los procesadores

•

Las memorias y los buses

•

Las arquitecturas con varios procesadores

•

L computadores

Los

t d

embebidos

b bid

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

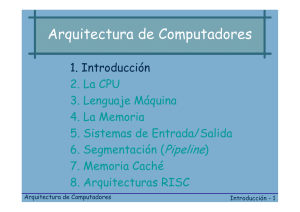

Evolución de los Procesadores

TCPU = NI x CPI x Tciclo

TCPU = NI x (CPE / IPE) x Tciclo

CPI

Procesadores Segmentados: IBM 7030 “Stretch” (1961)

Superescalares: CDC 6600 (1964); IBM 360/91 (1967) {Cocke-Agerwala,1987}

VLIW: AP-120B (1975); Multiflow (1987) {Fisher, Univ. Yale, 1983}

TCPU = (Noper/Op_instr) x CPI x Tciclo

NI

Procesadores Vectoriales: TI-ASC (1971); Cray-1 (1976)

Procesadores Matriciales: ILLIAC IV (1971; 1975 1º accesible en red) {Unger, 1958}

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Procesadores ILP

Inst. 1

IF

Inst. 2

t

Segmentado

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

WB

IF

ID

EX

MEM

Inst. 3

Inst 4

Inst.

IPC=1 F=1/t

x4

WB

Aumento de IPC y F

Aumento de IPC

IPC=2 F=2/t

Superescalar o VLIW IPC=2 F=1/t

t

t/2

Inst. 1

IF

ID

EX

MEM

WB

Inst. 1 IF ID EX M WB

Inst. 2

IF

ID

EX

MEM

WB

Inst. 3

IF

ID

EX

MEM

WB

Inst. 3

IF ID EX M WB

Inst. 4

IF

ID

EX

MEM

WB

Inst. 4

IF ID EX M WB

Inst. 2 IF ID EX M WB

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Límites del paralelismo entre instrucciones (ILP)

Dependencias de datos:

RAW WAR

RAW,

WAR, WAW

Dependencias

p

de control:

Saltos

No parece que se pueda

N

d

aprovechar mucho

paralelismo entre

instrucciones en este código

Década

Dé

d d

de llos 90 es un periodo

i d de

d innovación

i

ió fructífera

f

tíf

en ell diseño

di ñ

de microprocesadores: integración de buffers de renombramiento,

buffers de reorden, estaciones de reserva,......

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Renombrado, ejecución desordenada y

especulación en procesadores ILP

Los procesadores superescalares son capaces de renombrar los registros y

reordenar la ejecución,

j

, y especular

p

incluyendo

y

hardware ((estaciones de reserva,,

buffers de reorden, BTB,…), en los WLIW es el compilador quien extrae el

paralelismo que puede aprovechar el procesador

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Complejidad de los Cauces ILP

Cache

Instrucciones

Cache

Instrucciones

n bits x 1 inst/ciclo

IF

IF

MEM

WB

n bits x r inst/ciclo

BTB

Cola de

Instrucciones

ID

ALU

…..

Banco de

Registros

Cache

Datos

Procesador

Segmentado

ID/ISS

Banco de

Registros

Buffer de

Reorden

((ROB))

WB

Estación Reserva

Estación Reserva

Estación Reserva

UF

UF

MEM

Procesador Superescalar:

complejidad creciente en los cauces

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Cache

Datos

Límites de cauces ILP: consumo de energía

Los límites en la potencia que puede disipar un CI restringen la frecuencia a la

que puede funcionar

Pot ACV 2 f AVIshort VIleakage

( V Vthreshold ) 2

fmax B

V

eVthershold

I leakage H exp

KT

Sol

P6

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Límites de cauces ILP: retardos

Retardo~RwireCwire

Transistores

más lentos

Rwire=/(WxH)

/(

)

H

Valor previsto

por la SIA

W

Rwire ↑

Cwire ≈

tetapa

t

Cada vez se accede a menos superficie

((relativa)) del CI en un ciclo de relojj

Limites en el incremento de la

complejidad

p j

de la microarquitectura:

q

No se puede aumentar IPC y la

frecuencia de forma independiente

tretardo

t d

tciclo=1/F

tetapa

tretardo

tciclo(min)=1/Fmax

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Límites de cauces ILP: retardos

Retardo~RwireCwire

Transistores

más lentos

Rwire=/(WxH)

/(

)

H

Valor previsto

por la SIA

W

Rwire ↑

Cwire ≈

tetapa

t

Cada vez se accede a menos superficie

((relativa)) del CI en un ciclo de relojj

Limites en el incremento de la

complejidad

p j

de la microarquitectura:

q

No se puede aumentar IPC y la

frecuencia de forma independiente

tretardo

t d

tciclo=1/F

tetapa

tretardo

tciclo(min)=1/Fmax

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de los Microprocesadores ILP

I1

I3

I2

I5

I4

I7

I6

I10

I2

I3

I1

I4

I7

I8

I3

I2

I2

I5

I6

I4

I7

I1

I8

I9

I4

I5

I7

I8

I7

I8

I10

I6

I9

I10

I3

I2

I5

I2

I3

I1

I4

I7

I4

I6

I3

I5

I9

I8

I9

I8

I1

I1

I10

I6

Netburst Hyper-Threading:

Pentium 4HT (2002)

Power5

(2004)

Pentium D

(2005)

Sun T1

(2005)

I11

Multihebra

Sun T2

(2007)

Core (2006)

Multihebra

Simultánea

I5

Core i7

(2008)

Power4

(2001)

Superescalar

I1

I3

X

I2

X

X

I5

X

I7

I4

X

X

I9

I6

P5 ((1993):

) Pentium

P6 (1995): Pentium Pro,

II, III

Netburst (2000):Pentium 4

Pentium M ((2003))

X

X

X

X

I10

X

X

I2

I3

I1

I4

I5

I8

VLIW

Multicore

AMD

Opteron

(2003)

Itanium (2001)

Itani m 2 (2002)

Itanium

Montecito

(2006)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los ILP en el tiempo

Superescalares

SuperSPARC

p

(91)

( ) HiperSPARC (92)

Sun SPARC (87)

RISC I (80)

HP PA (92)

DEC 21264 (98)

DEC 21064 (92)

MIPS (82)

Power PC 601 (93)

IBM

POWER 1

(90)

Proyecto

Cheetah (82)

Intel

8008

(72)

Intel

8086

(78) CISC Intel x86

Intel 960 (89)

Intel 80386 (85)

Intel

4004

(71)

UltraSPARC

(00)

MIPS

R1x000

MIPS R10000 (94)

POWER4 (01)

P5 Pentium

(93)

Intel

80486

Pentium II P7 Pentium 4

(00)

(97)

P6 Pentium Pro Pentium III

(95)

(99)

AMD K5 (95)

CDC AFP (80)

VLIW

Cydrome CYDRA-5 (90)

TM-1 (96)

TRACE (87)

FPS AP-120 (75)

70

4 bits

8 bits

80

Core (06)

AMD K7 (99)

Transmeta Crusoe

(00)

Itanium IA-64

(00)

FPS AP-164 (80)

16 bits

Power

PC 970

(02)

Power PC 603 (94)

Multiflow (87)

32 bits

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

64 bits

Evolución de los procesadores:

Procesadores Matriciales y Vectoriales

TCPU = NI x CPI x Tciclo

TCPU = NI x (CPE / IPE) x Tciclo

CPI

Procesadores Segmentados: IBM 7030 “Stretch” (1961)

Superescalares: CDC 6600 (1964); IBM 360/91 (1967) {Cocke-Agerwala,1987}

VLIW: AP-120B (1975); Multiflow (1987) {Fisher, Univ. Yale, 1983}

TCPU = (Noper/Op_instr) x CPI x Tciclo

NI

Procesadores Vectoriales: TI-ASC (1971); Cray-1 (1976)

Procesadores Matriciales: ILLIAC IV (1971; 1975 1º accesible en red) {Unger, 1958}

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Procesadores Matriciales y Vectoriales

Procesador Matricial

SIMD

UC

EP1

EP2

EP3

EP4

C = A+B

C[1]=A[1]+B[1]

C[2]=A[2]+B[2]

C[3]=A[3]+B[3]

C[4]=A[4]+B[4]

F= D– E

F[1]=D[1]-E[1]

F[2]=D[2]-E[2]

F[3]=D[3]-E[3]

F[4]=D[4]-E[4]

G = K*H

G[1] K[1]*H[1]

G[1]=K[1]*H[1]

G[2] K[2]*H[2]

G[2]=K[2]*H[2]

G[3] K[3]*H[3]

G[3]=K[3]*H[3]

G[4] K[4]*H[4]

G[4]=K[4]*H[4]

Flujos de Datos

Flujo de Instrucciones

Procesador Vectorial

A[i]

[]

ADDV

B[i]

SUBV

D[i]

MULTV

E[i]

K[i]

Flujo de Instrucciones

H[i]

S

Sumador

d

C[i]

Restador

F[i]

Multiplicador

G[i]

Flujos de

Datos

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los Vectoriales en el tiempo

Hitachi SR8000 (98)

Hitachi S810-820 (84)

SX/4 (95)

NEC SX/2 (84)

SX/5 (98)

Vectoriales

Earth

Simulator

(02)

SX/6 (01)

IBM 3090/VF (86)

Fujitsu VPP700 (98)

Fujitsu VP100-200 (82)

VPP5000 (99)

Convex C4 (94)

Cray 3-4 (94)

Convex C1 C2 (85)

TI ASC (72)

Cray 2 (85)

C-90 (91)

T90 (96)

Cray 1 (76)

Cray X

X-MP

MP (83)

Cray Y

Y-MP

MP (88)

J90 (95)

( )

SV1 (98)

CDC7600 (70)

CDC Star 100 (72)

70

CDC Cyber 205 (81)

80

CDC ETA 10 (87)

90

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

Los Matriciales en el tiempo

GPUs Programables

NVIDIA GeForce 256 (99)

CM5 (91)

CM2 (90)

Repertorios SIMD

DAP 610 (87)

Goodyear

y

MPP ((80))

Intel MMX (97) SSE ((99))

AMD 3DNow! (98)

MasPar MP1 (85)

BSP (82)

IBM , Apple, Motorola

AltiVec (96-98)

IBM GF/11 (85)

HP MAX (93)

Illiac IV (71)

Sun VIS (95)

DEC MVI ((97))

70

80

90

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

AVX (11)

Evolución de los Procesadores: Arquitecturas

heterogéneas

g

T1

Arquitectura 1

Arquitectura 2

Procesador CELL (2005)

(IBM, Sony, Toshiba)

Procesadores de red:

IXP1200 (2000)

f de la ley

A d hl

Amdahl

disminuye

NVIDIA: Proyecto

y

Denver/Maxwell

AMD Trinity (2012)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Sucesión temporal de innovaciones

Ley de Grosch (53)

1er Programa

Almacenado

Baby (48)

Ley de

Amdahl (67)

IBM 701

(52)

UNIVAC I TRADIC

Whirlwind I

(55)

(51)

ENIAC

(46)

Taxonomía de Flynn (72)

Ley de Moore (65)

IBM S360

(64)

PDP-1

(60)

SIMD ILLIAC IV

Vectorial TI-ASC

(71)

PDP-11

(70)

Interrupciones

UNIVAC 1103

(53)

Superescalar

CDC6600 (64)

DMA, Canales

C

E/S

/S

IBM 709 (58)

Memoria

Virtual

Segmentación

(B5000, 61)

S

S-100

Altair (75)

55

ISA

S IBM

PC (81)

S

Sbus

Sun

(89)

S370/85

1ªCache

(68)

Propuestas de

cache no

bloqueante (81)

Propuestas de

cache m

multinivel

ltini el

(88)

AGP

G

Intel

(96)

16b

Itanium

Intel

(01)

HyperTransport

AMD (01)

Gigabit

Ethernet

(98)

EDO

DRAM (94)

Intel

Pentium D

(05)

PCIe

C

Intel

(06)

Infiniband

2Gbps (99)

QPI

Q

Intel

(08)

10 Gigabit

Ethernet

(02)

1ermicro con cache

L2: Pentium Pro

(95)

Propuestas

prefetching

(90)

FP DRAM

(90)

8b

Intel P7

Pentium 4

(00)

Fast Ethernet 100Mbps

Myrinet

y

512Mbps

p

(95)

Infiniband

QDR 40Gbps

p

(08)

1ermicro con

cache L3:

Itanium 2 (03)

DDR SDRAM

(00)

SDRAM

(96)

32b

3ª G

65

PCI

C

Intel

(92)

1ermicro con

cache L1:80486

(89)

Primera DRAM

comercial 1KB

(Intel/IBM, 70)

60

Multibus

(83)

Hipercubos

Cosmic Cube

(81)

Ethernet

10Mbps

p

Xerox (72)

4b

50

SuperSPARC Intel P6

(91)

AMD K5

(95)

Concepto de

Cache (Wilkes)

(65)

Patente memoria

de núcleos

magnéticos (51)

2ª G

Intel

Earth Simulator

IBM Roadrunner

Paragon

SGI Challenge

(02)

(08)

(92)

(90)

NYU

Cray T3D/E

CM5 (91)

Ultracomp.

(95)

(83)

IBM Power 4

( )

(01)

RISC Cheetah

(80) (82)

Intel 4004

(71)

Unibus PDP11

(69)

Mem.Virt.

Páginas

(Atlas,UK)

(62)

Memoria

entrelazada

t l

d

(LARC, 60)

45

Apple II

(77)

Altair 8800

(75)

ARPANET

WAN ((69))

1ª G

WWW CERN (89)

IBM PC

(81)

VLIW AP120B (75)

Pipeline CISC

Stretch B5000

(61)

(63)

Tubo Williams

(CRT) (46-47)

Cray 1

(76)

TOP 500 (Junio, 93)

DDR3 (07)

DDR2 (03)

64b

4ª G

70

75

80

85

90

95

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

05

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

¿Cómo han evolucionado los computadores?

•

Los comienzos

•

Los procesadores

•

Las memorias y los buses

•

Las arquitecturas con varios procesadores

•

L computadores

Los

t d

embebidos

b bid

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de la Memoria

Tubos - Ferrita

Semiconductor

….

Latencia

Tecnología

Tubos

- Ferrita

Capacidad

de

Semiconductor

Integración

Caches

Reducir el

tiempo de

acceso a los

datos

Aumentar el

espacio de

almacenamiento

Org.

DRAM

Ancho de Banda

Tubos

- Ferrita

Jerarquía

de

Semiconductor

Memoria

Paralelismo

Transf.

Transf

Bloques

L

Localidad

lid d

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de la Memoria: Memoria

Entrelazada

Módulo 0

Ta = M*t

Módulo 1

Acceso 1

Multiplexor

p

Módulo 2

Acceso 2

0

M-1

Ta

t

0 1 …… M-1 0 1 …… M-1

m bits menos

significativos

Módulo

M1

M-1

T = Ta + M*t

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de la Memoria: DRAM

1

2

Acceso

Convencional

FPM

EDO

1

SDRAM

2

Mejora de Anchos de

Banda de la Memoria

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de la Memoria: SDRAM DDR

Tiene varios bancos de memoria internos y

multiplexa los buffers de E/S (I/O buffers): los

datos pasan de buses más anchos en el interior

de la memoria a buses más estrechos (de igual

tamaño que en la memoria DDR)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Evolución de los Buses

Unibus

JJerarquías

í

de Buses

PCI Express II

10 GBps

PCI Express

5 GBps

Aumento en los anchos de banda

AGP 8

8x

2.1 GBps

ISA

8 MBps

1985

PCI

133 MBps

AGP 1x

266 MBps

1993

1997

AGP 2x

533 MBps

1998

AGP 4x

1.1 GBps

1999

2002

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

2004

2006

Interfaces de memoria y red más integradas

Las arquitecturas multinúcleo integran el controlador de memoria y la interfaz de red

(incluyendo el conmutador)

Core0 Core1 Core2 Core3 Core4 Core5 Core6 Core7

L1

L1

L1

L1

L1

L1

L1

L1

L2

L2

L2

L2

L2

L2

L2

L2

LLC - L3

Controlador

memoria

(MC)

Controlador

memoria

(MC)

NI+Switch

QPI

SMI

Intel Xeon 7500

H

HyperTransport

T

t (2001) 12

12.8

8 GB/s

GB/

QPI (2008) 25.6 GB/s

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Sucesión temporal de innovaciones

Ley de Grosch (53)

1er Programa

Almacenado

Baby (48)

Ley de

Amdahl (67) Taxonomía de Flynn (72)

SIMD ILLIAC IV

Vectorial TI-ASC

(71)

IBM 701

(52)

UNIVAC I TRADIC

Whirlwind I

(55)

(51)

ENIAC

(46)

Ley de Moore (65)

IBM S360

(64)

PDP-1

(60)

PDP-11

(70)

Cray 1

(76)

IBM PC

(81)

Apple II

(77)

Altair 8800

(75)

VLIW AP120B (75)

Pipeline CISC

Stretch B5000

(61)

(63)

Superescalar

CDC6600 (64)

Intel

Earth Simulator

IBM Roadrunner

Paragon

SGI Challenge

(02)

(08)

(92)

(90)

NYU

Cray T3D/E

CM5 (91)

Ultracomp.

(95)

(83)

IBM Power 4

( )

(01)

SuperSPARC Intel P6

(91)

AMD K5

(95)

RISC Cheetah

(80) (82)

Intel 4004

(71)

TOP 500 (Junio, 93)

WWW CERN (89)

Intel P7

Pentium 4

(00)

Itanium

Intel

(01)

Intel

Pentium D

(05)

Infiniband

2Gbps

p ((99))

Interrupciones

UNIVAC 1103

(53)

DMA, Canales E/S

IBM 709 ((58))

Memoria

Virtual

Segmentación

(B5000, 61)

Tubo Williams

(CRT) (46-47)

Unibus PDP11

((69))

S-100

Altair ((75))

Propuestas de

cache no

bloqueante (81)

Primera DRAM

comercial 1KB

(Intel/IBM, 70)

4b

45

50

2ª G

55

60

Multibus

((83))

Sbus

Sun

(89)

Propuestas de

cache m

multinivel

ltini el

(88)

8b

16b

AGP

Intel

(96)

10 Gigabit

Ethernet

(02)

HyperTransport

AMD ((01))

1ermicro con cache

L2: Pentium Pro

(95)

Propuestas

prefetching

(90)

FP DRAM

(90)

EDO

DRAM (94)

Infiniband

QDR 40Gbps

(08)

PCIe

Intel

(06)

QPI

Intel

(08)

1ermicro con

cache L3:

Itanium 2 (03)

DDR SDRAM

(00)

SDRAM

(96)

32b

3ª G

65

PCI

Intel

(92)

1ermicro con

cache L1:80486

(89)

S370/85

1ªCache

(68)

Patente memoria

de núcleos

magnéticos (51)

1ª G

ISA IBM

PC ((81))

Gigabit

Ethernet

(98)

Fast Ethernet 100Mbps

Myrinet 512Mbps

(95)

Concepto de

Cache (Wilkes)

(65)

Mem.Virt.

Páginas

(Atlas,UK)

(62)

Memoria

entrelazada

t l

d

(LARC, 60)

Hipercubos

Cosmic Cube

(81)

Ethernet

10Mbps

Xerox (72)

ARPANET

WAN (69)

DDR3 (07)

DDR2 (03)

64b

4ª G

70

75

80

85

90

95

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

05

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

¿Cómo han evolucionado los computadores?

•

Los comienzos

•

Los procesadores

•

Las memorias y los buses

•

Las arquitecturas con varios procesadores

•

L computadores

Los

t d

embebidos

b bid

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Comienzo de los 60.

Punto de Rendimientos decrecientes:

más prestaciones significaban circuitos

más complejos y de mayor tamaño.

Los tiempos de propagación de las

p

a los tiempos

p de

señales se aproximan

ciclo (se utiliza el argumento del límite

que impone la velocidad de la luz: 1 pie

por nanosegundo y máquinas de 30 pies

de lado con tiempos de ciclo del orden de

g

)

los nanosegundos)

Ley de

Grosch

Rendimientos

decrecientes

HEP (1978)

Multihebra

CDC 6600 (1964)

p

Proc. Superescalar

TI-ASC (1971)

Vectorial

Ley de Moore

(1965)

2ª Generación

AP-120B (1975)

Proc. VLIW

IBM 360/91 (1967)

Proc. Superescalar

Ley de Amdahl

(1967)

Ley de Grosch

(1953)

ILLIAC IV (1971)

Matriciales (SIMD)

Coste

19

964

IBM 7030 (1961)

Segmentación

C.mmp

C

mmp (1972)

(16 PDP-11)

Velocidad

3ª Generación

3

Cray 1 (1976)

Vectorial

Microprocesador

Intel 4004 (1971)

1971

1955

Hacia las arquitecturas con varios procesadores

Taxonomía de

Flynn (1972)

4ª Generación

4

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los Computadores Paralelos

UMA

Multiprocesadores

SMP

P

P

P

P

C ache

C ache

C ache

C ache

R ed de Interconexión

B ridge

P

C ontrolador

de M em oria

Cache

E /S

Bridge

Controlador

de Memoria

N IC

P

DRAM

P

P

P

P

Cache

Cache

Cache

E/S

DRAM

NIC

Controlador

B id

Bridge

Controlador

de Memoria

Bridge de Memoria

NORMA

Multicomputadores

Clusters

E/S

Cache

Cache

Cache

Bridge

E/S

P

Controlador

de Memoria

DRAM

Controlador

B id

Bridge

Controlador

de Memoria

Bridge de Memoria

DRAM

DRAM

NIC

E/S

NIC

Red de Interconexión

Bridge

E/S

DRAM

DRAM

DRAM

NIC

E/S

Controlador

de Memoria

NIC

NIC

E/S

NIC

NUMA

Red de Interconexión

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los computadores paralelos en el tiempo

70

80

00

90

Multicomputadores

nCube (90)

J-Machine MIT (92)

Mosaic-C (92)

Cosmic Cube (81)

Intel Paragon (92)

Intel iPSC’s (83)

CM5 (91)

SMP basado en bus

Sequent Symmetry (88)

UMA: SMP

16 PDP-11/40

conectados a 16

módulos

ód l de

d

memoria con

una red de

barras cruzadas

Coherencia

Directorios (1976)

IBM 3081

SGI Challenge (90)

SGI 4D/240 (88)

KSR 1 (91)

Cedar Illinois (87)

DASH Stanford (92)

BBN Butterfly (89)

Sun Enterprise (98)

Convex

Exemplar (97)

NUMA

Coherencia

Snoopy (1983)

C mmp (72)

C.mmp

Sun SPARC Center (98)

Encore Multimax (87)

Synapse N+1 (83)

SGI Origin (97)

Cray T3D/E (95)

CC-NUMA (1988)

UMA

4 bits

NYU Ultracomputer (83)

8 bits

16 bits

80

IBM RP3 (85)

COMA: KSR1 (1991)

32 bits

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

64 bits

Los Clusters (final de los 90)

Si cada año y medio (o dos años) se tiene un

microprocesador con el doble de

prestaciones, el tiempo de desarrollo de las

plataformas paralelas es importante: uso de

elementos hardware estándar para

configurarlas

70

60

50

40

32

30

20

10

0

0

1,5

3

4.5

6

7.5

9

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los Clusters (final de los 90)

Si cada año y medio (o dos años) se tiene un

microprocesador con el doble de

prestaciones, el tiempo de desarrollo de las

plataformas paralelas es importante: uso de

elementos hardware estándar para

configurarlas

70

60

50

40

32

30

20

10

0

0

1,5

3

4.5

6

7.5

9

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Los Clusters (final de los 90)

Si cada año y medio (o dos años) se tiene un

microprocesador con el doble de

prestaciones, el tiempo de desarrollo de las

plataformas paralelas es importante: uso de

elementos hardware estándar para

configurarlas

70

60

50

40

32

30

20

10

0

0

1,5

3

4.5

6

7.5

9

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

TOP500 (Evolución de arquitecturas)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

TOP500 (presencia de procesadores)

Nov. 2003

Nov. 1993

Jun 2013

Nov 1998

Nov.

Nov 2008

Nov.

Distribución de Prestaciones

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Las redes de interconexión y los nodos

Switch

Switch

P

Interfaz

de red

Nodo

Switch

Nodo

Switch

M

Switch

Nodo

Nodo

Nodo

Del diseño de redes específicas al uso de redes comerciales (específicas para altas

prestaciones o no):

•

•

•

•

QsNET (Quadrics)

Myrinet (Myricom)

Gigabit Ethernet

Infiniband

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

TOP500 (Evolución de las redes)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

TOP500 (Presencia de redes)

Nov. 1993

Nov. 2003

N

Nov.

1998

N

Nov.

2008

Jun. 2013

Distribución de Prestaciones

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Sucesión temporal de innovaciones

Ley de Grosch (53)

1er Programa

Almacenado

Baby (48)

Ley de

Amdahl (67) Taxonomía de Flynn (72)

SIMD ILLIAC IV

Vectorial TI-ASC

(71)

IBM 701

(52)

UNIVAC I TRADIC

Whirlwind I

(55)

(51)

ENIAC

(46)

Ley de Moore (65)

IBM S360

(64)

PDP-1

(60)

PDP-11

(70)

Cray 1

(76)

IBM PC

(81)

Apple II

(77)

Altair 8800

(75)

VLIW AP120B (75)

Pipeline CISC

Stretch B5000

(61)

(63)

Interrupciones

UNIVAC 1103

(53)

Superescalar

CDC6600 (64)

DMA, Canales

C

E/S

/S

IBM 709 (58)

Unibus PDP11

(69)

Intel

Earth Simulator

IBM Roadrunner

Paragon

SGI Challenge

(02)

(08)

(92)

(90)

NYU

Cray T3D/E

CM5 (91)

Ultracomp.

(95)

(83)

IBM Power 4

( )

(01)

SuperSPARC Intel P6

(91)

AMD K5

(95)

RISC Cheetah

(80) (82)

Intel 4004

(71)

S

S-100

Altair (75)

TOP 500 (Junio, 93)

WWW CERN (89)

ISA

S IBM

PC (81)

Multibus

(83)

S

Sbus

Sun

(89)

PCI

C

Intel

(92)

Intel P7

Pentium 4

(00)

AGP

G

Intel

(96)

Itanium

Intel

(01)

HyperTransport

AMD (01)

Intel

Pentium D

(05)

PCIe

C

Intel

(06)

QPI

Q

Intel

(08)

Infiniband 2Gbps (99)

ARPANET

WAN ((69))

Memoria

Virtual

Segmentación

(B5000, 61)

Tubo Williams

(CRT) (46-47)

1ermicro con

cache L1:80486

(89)

S370/85

1ªCache

(68)

Patente memoria

de núcleos

magnéticos (51)

Propuestas de

cache no

bloqueante (81)

Primera DRAM

comercial 1KB

(Intel/IBM, 70)

4b

1ª G

45

50

2ª G

55

60

Fast Ethernet 100Mbps

Myrinet

y

512Mbps

p

(95)

Concepto de

Cache (Wilkes)

(65)

Mem.Virt.

Páginas

(Atlas,UK)

(62)

Memoria

entrelazada

t l

d

(LARC, 60)

Hipercubos

Cosmic Cube

(81)

Ethernet

10Mbps

p

Xerox (72)

Propuestas de

cache m

multinivel

ltini el

(88)

8b

16b

65

EDO

DRAM (94)

Infiniband

QDR 40Gbps

p

(08)

1ermicro con

cache L3:

Itanium 2 (03)

DDR SDRAM

(00)

SDRAM

(96)

32b

3ª G

10 Gigabit

Ethernet

(02)

1ermicro con cache

L2: Pentium Pro

(95)

Propuestas

prefetching

(90)

FP DRAM

(90)

Gigabit

Ethernet

(98)

DDR3 (07)

DDR2 (03)

64b

4ª G

70

75

80

85

90

95

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

00

05

Perspectiva Histórica de la Ingeniería de

Computadores

¿Qué

Q

objetivos

j

y factores determinan la evolución de

los computadores?

¿Cómo han evolucionado los computadores?

•

Los comienzos

•

Los procesadores

•

Las memorias y los buses

•

Las arquitecturas con varios procesadores

•

L computadores

Los

t d

embebidos

b bid

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

“The big picture” (con poca resolución)

60

70

80

Mainframes /

Supercomputadores

90

00

Servidores

Grandes computadores para

aplicaciones de negocios y

científicas de gran volumen.

WWW

Minicomputadores

Aplicaciones científicas

en laboratorios y

pequeñas

p

q

organizaciones

g

Microprocesador

Intel 4004 ((1971))

1971

1

1964

4

REDUCIR

COSTE

Redes

PCs y

Estaciones de

Trabajo

Computadores Embebidos

Rápido

Rá

id crecimiento

i i t (t

(tecnología

l í y

herramientas de diseño): electrónica

digital de altas prestaciones,

videojuegos, teléfonos móviles, tarjetas

inteligentes conmutadores,….

inteligentes,

conmutadores

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Computadores embebidos

Uno de los primeros computadores embebidos es el

Autonatics D-17, un sistema de control de vuelo

del misil Minuteman, desarrollado en 1961. Otro de

los primeros es el sistema de control de vuelo del

A l utilizando

Apolo,

tili

d la

l tecnología

t

l í de

d Circuitos

Ci it

Integrados del momento (1966) para ahorrar peso y

reducir tamaño

700

600

500

400

Empotrados

Para PCs

300

200

100

0

1996

1998

2000

2002

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Algunas de las empresas

Altera: empresa fundada

Alt

f d d en1983

1983

Xilinx: empresa fundada en1984 (por el inventor de las FPGAs, Ross Freeman)

ARM Holdings: fundada por Acorn Computers (en la que se diseñó la arquitectura

ARM en 1983)

1983), Apple y VLSI Technology)

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Ampliación del universo de aplicaciones

Nuevos Paradigmas:

•

Internet de las Cosas

•

Computación ubicua

•

eSalud

•

Smart Metering

•

Smart Grid

•

Smart City

•

Smart TV

•

PAC Soft-PLC,

PAC,

Soft PLC …

•

…

•

Hardware Libre

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Hardware Libre

El denominado Hardware Libre o Harware de acceso abierto (Open Source Hardware) se

refiere al hardware cuyas especificaciones y diagramas esquemáticos son de acceso

público, ya sea bajo algún tipo de pago o de forma gratuita (diseño y difusión similar al del

software libre).

libre)

Está contribuyendo de manera decisiva a extender proyectos de diseño de dispositivos de

cómputo para aplicaciones muy diversas que ponen de manifiesto las posibilidades de la

ingeniería de computadores para los emprendedores:

http://www.neoteo.com/famosos-proyectos-de-hardware-libre

Arduino

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Smartphones: ¿supercomputadores móviles?

Dadas las prestaciones pico (>100

GOPS) y consumo de potencia

(~1W) requeridos por los protocolos

3G y 4G, un procesador

“convencional”, a 2-3 GHz, capaz de

terminar 2-3 instrucciones/ciclo

instrucciones/ciclo, no

satisface estos requisitos

La tendencia son los sistemas

embebidos con arquitecturas

multinúcleo heterogéneas

g

(núcleos especializados y

aceleradores hardware para

operaciones específicas)

Woh, M. et al.: “Mobile Supercomputers for

the Next-Generation Cell Phone”. IEEE

Computer. Enero, 2010.

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Conclusiones

La evolución de los computadores ha estado determinada por la forma en que la

tecnología, las aplicaciones, los factores intervienen en los objetivos de diseño

de las arquitecturas (mejora de prestaciones, reducción de coste, y eficiencia

energética).

energética)

En la evolución de las arquitecturas ha sido frecuente que técnicas

desarrolladas e implementadas utilizando una determinada tecnología

reaparezcan con mejoras tecnológicas que las hacen más eficientes o permiten

sistemas menos costosos (wheel of reincarnation)

Las principales estrategias de la arquitectura para aprovechar las mejoras

tecnológicas han venido de la mano del aprovechamiento del paralelismo y de la

localidad de acceso a los datos, q

que interactúan en todos los niveles del

computador.

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Algunas Referencias

http://www.computerhope.com/history/index.htm

http://www.zib.de/zuse/Inhalt/Programme/eniac/index.html

http://people.cs.clemson.edu/~mark/admired

http://people.cs.clemson.edu/

mark/admired_designs.html

designs.html

http://www.semichips.org/home.cfm: SIA (Semiconductor Industry Association). “The technology

roadmap for semiconductors”.

http://awards.acm.org/eckert_mauchly/: Premios Eckert-Mauchly ACM-IEEE CS

AGARWAL, V. et al.: Clock rate versus IPC: The End of the Road for Conventional Microarchitectures.

ACM ISCA,, pp.248-259,

pp

, 2000.

HENNESSY, J.L.; PATTERSON, D.A.:“Computer Architecture. A Quantitative Approach”. Morgan

Kaufmann, 2006 (4ª Edición).

IEEE Computer, Septiembre, 1997.

ORTEGA, J.:”Entre la profecía de Moore y la ley de Amdahl”. Lección inaugural ETSIIT. Noviembre,

2008.

SMITH, R.E.:”A Historical Overview of Computer Architecture”. Annals Hist. Comp., 1989

VAJAPEYAM,, S.;; VALERO,, M.:”Earlyy 21st Centuryy Processors”. IEEE Computer.

p

Abril,, 2001.

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013

Gracias por la Atención

Perspectiva Histórica en Ingeniería de Computadores. Centro Mediterráneo, 2013