開啟原PDF

Anuncio

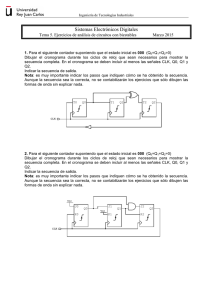

1. 2. 3. 4. 5. 6. 7. Retardos, “glitches” y registros de sincronización Temporización en sistemas síncronos El “skew” de reloj Distribución de reloj Circuitos no recomendados Frecuencia máxima de funcionamiento de un circuito síncrono Metaestabilidad: sincronizadores Diseño síncrono NOT 7404 La salida de los circuitos no se produce de forma instantánea cuando cambian sus entradas sino que transcurre un tiempo determinado entre ambos sucesos. A este tiempo se le conoce como retardo de propagación. 1. Retardos y glitches No es posible determinar de forma exacta el valor de estos retardos por lo que en los catálogos se especifican valores mínimos, típicos y máximos. El retardo de propagación depende de la carga, de la temperatura de operación y del envejecimiento de los componentes. • TPHL: Tiempo que transcurre entre la variación de la entrada y el paso de la salida de nivel alto a nivel bajo. Este tiempo se mide en los puntos donde la amplitud de las señales es del 50%. • TPLH: Retardos (Definiciones) S A B C (A⊕B) S A B C (A⊕B) Operación de un sumador de tres bits S = (A ⊕ B) ⊕ C Retardos de propagación de una puerta XOR 74S86 Glitches cuando pasa de 000 → 101 y de 010 → 111 Glitches La diferencia de retardos entre caminos puede producir glitches en la salida. Durante estos estados espúreos el valor de la salida no es válido, ni estable. En un diseño correcto no deben utilizarse señales con glitches como señales de reloj en circuitos sensibles a flancos. Glitches (Actividad espúria) El empleo de lógica registrada no evita los glitches, sino su efecto sobre el resto del sistema. Se trata de sincronizar la lógica de modo que se toman muestras de la señal en determinados puntos, fuera de ellos, los espúreos no tienen efecto. • Circuito síncrono: • Circuito que emplea una señal de reloj para sincronizar todos los cambios de estados internos • Contienen elementos de memoria, flip-flops, temporizados por la misma señal de reloj común Diseño síncrono • Síncronos: Incorporan señales de reloj. Los eventos se capturan en flancos de reloj que ocurren en intervalos bien definidos. Las salidas de un estado tienen un ciclo de reloj para propagarse al próximo estado. Se toleran retardos en la llegada del dato dentro del mismo periodo de reloj. El sistema es más fiable. • Asíncronos: No existen señales de reloj. Para garantizar un correcto funcionamiento el cambio en una entrada sólo puede producirse después de que el circuito esté estable como consecuencia del cambio anterior. El sistema es menos fiable. Sistemas secuenciales: Diseño síncrono Q Q D CLK tpFF thold DATO ESTABLE tsetup DATO ESTABLE Si no se respetan los tiempos de setup y de hold no se garantiza el correcto funcionamiento del FF CLK D Parámetros temporales en un FF 2. Temporización t t t FF 7474 CLK D Q Parámetros temporales en un FF Q2 D2 Q1 D1 CLK D1 Q DATO tpFF tsetup thold tpFF CLK D Q1 tpFF DATO tsetup thold CLK D Q DATO tsetup D2 Q2 tCLKmin : tiempo mínimo del periodo de reloj para captura con éxito tpLCR DATO tpLCR LÓGICA COMBINACIONAL + RUTADO Temporización t t t t t Clk Q_C Q_B Q_A 3 ciclos CLK 0.0 0 A D Q_A 4.5 0 Q_C Q_B Q_A B Clk Clk de FF_A y FF_C B D Q_B 0 2 ciclos 0.0 Puede provocar un fallo en la sincronización D C Q_C 3. Retardo en el reloj (Clock Skew) Las dos primeras causas dependen de la implementación del circuito (emplazamiento-rutado) Las dos últimas dependen de la fabricación Factores que lo originan: Diferencia de caminos en las líneas de reloj Diferencia entre los parámetros distribuidos (R,C) de cada línea Diferencia de retardo de los buffers de la línea de reloj Diferencias entre registros (características eléctricas): tFF, umbrales de disparo, etc. Retardo en el reloj (Clock Skew) • All major synthesis tools can infer global buffers onto clock signals that come from off-chip You can always use a BUFG symbol and the software will choose an appropriate buffer type • XC4000E/L and Spartan have 4 BUFGPs and 4 BUFGSs • XC4000EX/XL/XV and SpartanXL have 8 BUFGLSs • Virtex and Spartan-II have 4 BUFGs All Xilinx FPGAs have global buffers • This routing network is balanced to minimize skew Global buffers are connected to dedicated routing Usar buffers globales para reducir el skew 4. Distribución de reloj Pínes dedicados para utilizar las líneas dedicadas de reloj • GCLK1 – GCLK8 • Cada uno se conecta a un BUFGLS Buffers: • BUFGLS: Global Low-Skew Buffer • BUFGE: Global Early Buffer Líneas globales: distribuyen el reloj y otras señales de alto fan-out Líneas globales en XC400XL Líneas globales en XC4000XL Cualquier BUFGLS puede conectarse a las líneas globales de todo el dispositivo Los BUFGE sólo se pueden conectar a las líneas globales de su cuadrante Líneas globales en XC4000XL Entrada de reloj Distribución de las líneas de reloj Introduce skew entre CLK1 y CLK2 El uso de un BUFG extra lo reduce No hay skew de reloj Divisor de reloj recomendado Divisor de reloj tradicional CLK1 CLK1 BUFG BUFG D D Q Q CLK2_CE BUFG CLK2 Retardo en el reloj (Clock Skew) Q D Q CE D Contador D FF Q Si la línea conectada a Q3 es más lenta, la transición 0111→1000, puede convertirse en 0111→1111→1000 Produciendo un glitch en el reloj CLK Q3 Q2 Q1 Q0 Contador CE D FF Q Este circuito no produce glitches: hay que utilizar las entradas de “clock enable” para evitar los glitches en el reloj CLK Q3 Q2 Q1 Q0 Hay que evitar que se produzcan glitches en el reloj • Los FFs de los dispositivos actuales son muy rápidos: pueden responder a pulsos de reloj muy estrechos ⇒ NO conectar la salida de lógica combinacional a una entrada de reloj de un FF (“gated-clock”) 5. Circuitos NO recomendados Ejemplo: contadores Circuitos NO recomendados RST CLK X CLK_12MHz FPGA CLK RST INx P DETECTOR DE PATRON “01101” CLK_in CLK_out RST DIVISOR DE FRECUENCIA CLK_1KHz CLK RST CE Q CONTADOR 2 BITS Ejemplo: contador de secuencias 2 RST RST RST TC S(3..0) TC CLK INC RST TC S(3..0) CONTADOR BCD CLK INC TC S(3..0) CONTADOR BCD CLK INC CONTADOR BCD CLK 4 4 4 4 SEL M C MUX_4a1 D U O DECODIFICADOR S(3..0) CONTADOR BCD INC I BCD(3..0) 4 DIS(3..0) 4 Circuitos recomendados INCORRECTO Gated Clock CORRECTO Circuitos NO recomendados RESET asíncrono CLR FF Q Los glitches en SET/RESET asíncronos pueden dar lugar a comportamientos indeseados del circuito CLK Q[0] Q[x] Contador binario D Q[0] RESET síncrono R FF Q Siempre que sea posible hay que utilizar SET/RESET síncronos CLK Q[x] Contador binario D Hay que evitar que se produzcan glitches en los Set/Reset Circuitos NO recomendados El camino más lento determinará la frecuencia máxima de trabajo Caminos: •Retardo de FF a FF •Retardo de FF a Pad de salida •Retardo de Pad de entrada a FF •Retardo combinacional Pad a Pad •Reloj a través de lógica 6. Frecuencia máxima de funcionamiento de un circuito síncrono tpLC tpFF Violación del tiempo de hold Máxima frecuencia de reloj tsetup CLK D Q tH ≤ tpFF+tpLC TCLK ≥ tpFF+tpLC+tsetup LÓGICA COMBINACIONAL + RUTADO Q CLK D Máxima frecuencia de reloj Clock-to-clock Clock-to-clock Clock-to-pad Pad-to-clock Pad-to-pad Reloj a través de lógica Se desea implementar en el dispositivo CPLD 9536-5 los siguientes circuitos Indíquese: 1.Número de macroceldas 2.Número y tipo de pines utilizados 3.Frecuencia máxima de funcionamiento del circuito Ejercicios Clk A U3 C D U1 Q 8 ns U4 7 ns C D U2 Q Y 6 ns U6 DFFs : Tsu = 3 ns Thd = 4 ns Tc2q = 5 ns 9 ns U5 ¿Cuál es la máxima frecuencia de operación de este circuito? 2 ns U8 U7 1 ns Ejercicio BUFG D Q D D Q Q D D Q Q • Aplicando las ecuaciones anteriores a cada etapa registrada • Analizar los retardos en las entradas y salidas • El retardo más restrictivo fijará la velocidad máxima de funcionamiento del sistema completo BUS [7..0] CLK ADATA ¿Cómo garantizar que nuestro sistema funciona? Máxima frecuencia de reloj OUT1 Datos CLK interno Microprocesador FPGA, u otro sistema A nuestro sistema pueden llegar señales externas (de un teclado, del ratón, de un sensor, etc.) que no están sincronizadas con el reloj del sistema. Por ello, en su captura pueden producirse violaciones de setup o hold que van a conducir al sistema a un estado metaestable. Para minimizar (no se pueden evitar) la metaestabilidad (oscilación de la salida del FF) se utilizan los sincronizadores. Fuente externa de datos 7. Metaestabilidad, sincronizadores FF Clk del sistema Entrada así asíncrona FF Dato sincronizado Para sincronizar una señal asíncrona pueden colocarse dos o más FFs en cascada funcionando con el reloj del sistema. Sincronización de una entrada asíncrona Problemas de la sincronización con un único FF: 1. Que la duración del pulso sea mayor de dos periodos de la señal de reloj (podría interpretarse que llega más de un pulso). 2. Que la duración del pulso sea menor que un periodo de la señal de reloj (es posible que se pierda). Sincronización de señales asíncronas Sincronización de señales asíncronas Sincronización de un sistema multireloj Click below to find more Mipaper at www.lcis.com.tw Mipaper at www.lcis.com.tw