Descargar

Anuncio

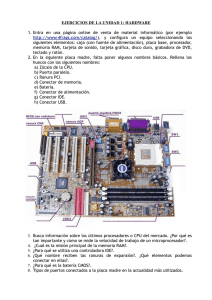

5. EL SISTEMA DE VISIÓN XILINX SPARTAN-6 IVK En el siguiente capítulo se presenta una descripción detallada del sistema de visión Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit, desarrollado y distribuido por el fabricante Avnet Electronics. En primer lugar, se dará una visión general de las características principales de la familia Spartan-6 de Xilinx, indicando sus ventajas en los sistemas de alto rendimiento como pueden ser los de visión artificial. Seguidamente se presentará la placa de desarrollo Xilinx® Spartan®-6 LX150T Development Kit, que junto al sensor OmniVision OV9715 y a las tarjetas auxiliares FMC-IMAGEOV / FMC-DVI componen el sistema de visión completo. Por último, se hará una lista de las herramientas software que vienen incluidas, así como el repositorio de IP-Cores incluidos y los diseños de referencia que sirven como base para cualquier diseño de un sistema de visión. 5.1 Introducción El sistema Spartan-6 FPGA Industrial Vídeo Processing Kit es una herramienta de diseño integral para la creación de prototipos, y el desarrollo de aplicaciones avanzadas de procesamiento de imágenes en el mundo de la industria. El Kit completo, tanto la parte hardware, como el software, y los diseños de referencia están especialmente concebidos para permitir a los ingenieros en hardware realizar sistemas más confiables, disminuyendo al mismo tiempo el tiempo de diseño y los recursos necesarios para su puesta a punto. El sistema de desarrollo está compuesto de los siguientes elementos: x Spartan-6 LX150T PCI Express Development Kit [65] [66] [67]. Es la placa de desarrollo en la que se basa todo el sistema de visión. Dispone de una FPGA modelo Xilinx Spartan-6 XC6SLX150T, así como memoria DDR3 SDRAM, memoria Flash, conectores USB, Jtag, ranura PCI-Express y otros elementos que se verán más adelante. x Sensor OmniVision OV9715 [68]. Es el sensor de imagen, fabricado por OmniVision para los sistemas de visión de alto rendimiento. Es capaz de capturar imágenes con resolución de 720p (líneas horizontales), y la lente de la cámara proporciona un ángulo de visión de casi 180º. x Tarjetas auxiliares FMC-IMAGEOV / FMC-DVI [69] [70] [71] [72]. Tarjetas controladas por la FPGA a través de la placa de desarrollo, y que proporcionan las interfaces de entrada y salida para vídeo DVI proveniente de una cámara digital, o desde el sensor de imagen OV9715. Además, el Kit incluye una licencia completa (aunque bloqueada para su uso únicamente con el dispositivo LX150T) de Xilinx ISE® Design Suite: System Edition DVD, así como algunos diseños completos de referencia que pueden descargarse desde la Web de Avnet Electronics, previo registro. En los siguientes apartados de este capítulo se describirán uno a uno los elementos que componen el sistema de visión. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 82 5.2 Recursos lógicos en la FPGA Spartan-6 Figura 5.1. Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit, usado en este Proyecto Fin de Carrera [163]. 5.2 Recursos lógicos en la FPGA SPARTAN-6 La familia Spartan-6 de Xilinx cuenta con unas características ideales para sistemas de alto rendimiento, proporcionando gran flexibilidad y eficiencia en sistemas de visión. Construida con tecnología de 45nm y preparada para trabajar con voltajes bajos, estas FPGA proporcionan un ahorro considerable de consumo con respecto a las familias anteriores, proporcionando además un balance adecuado entre calidad y precio. Esta familia de FPGAs incluye una nueva y más eficiente lógica en sus tablas LUT (que disponen de seis entradas y de un registro dual) además de 18Kb de memoria BlockRAM, Slices DSP48A1 de nueva generación, controladores de memoria SDRAM, controlador de niveles de consumo, tecnología SelectIO™, bloques transceptores optimizados de alta velocidad, transceptores compatibles con PCI Express, entre otros. En [63] se pueden ver en detalle todas las características de esta familia. Tabla 5.1. Bloques lógicos de la FPGA Xilinx® Spartan®-6 XC6SLX150T [63]. A continuación se describen brevemente los elementos que componen la familia de dispositivos Spartan-6. CLBs, Slices, y LUTs. Cada uno de los bloques lógicos configurables (CLB) está compuesto de dos slices, dispuestos uno al lado del otro en dos columnas. Existen tres tipos de slices en la arquitectura de la familia Spartan-6: SLICEM, SLICEL, y SLICEX. Cada uno de ellos contiene cuatro LUTs, ocho biestables y lógica variada. Las LUTs son de propósito general, tanto para lógica combinacional como para secuencial. Las herramientas de síntesis están preparadas PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 83 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK para sacar el mejor rendimiento de estas celdas, proporcionando una alta eficiencia en la implementación. Los tres tipos de slices mencionados anteriormente se distribuyen de la siguiente manera: x SLICEM. Corresponden al 25% del total en la FPGA, y sus LUTs pueden ser configuradas como tablas con seis entradas y una salida, o como tablas de cinco entradas y dos salidas independientes entre sí. Estos slices también pueden ser configurados como memoria RAM distribuida con 64 bits por cada LUT, como registro de desplazamiento de 32 bits (SRL32), o dos registros de desplazamiento de 16 bits (SRL16s) con todos elementos accesibles mediante direccionamiento. La salida de cada LUT es registrada por un biestable dentro de la CLB. Para operaciones aritméticas, contiene un registro de acarreo de alta velocidad, que propaga la señal de acarreo a través de las columnas de slices. x SLICEL. Corresponden a otro 25% del total en la FPGA, y agrupa todas las características anteriores, a excepción de las funciones de memoria y registro de desplazamiento. x SLICEX. Abarcan el 50% restante del total de la FPGA, y tienen la misma estructura que los SLICEL, a excepción de los registros de acarreo para operaciones aritméticas. Administración de Reloj. Cada FPGA Spartan-6 tiene hasta seis CMTs (Clock Management Tile), cada uno compuesto de dos DCMs (Digital Clock Manager) y un PLL (PhaseLocked Loops), que pueden ser utilizados individualmente o en cascada. El DCM proporciona cuatro fases diferentes para el reloj de entrada (CLKIN), a 0º, 90º, 180º y 270º (CLK0, CLK90, CLK180 y CLK270 respectivamente). Además, es capaz de proporcionar relojes al doble de frecuencia del reloj de entrada, así como un divisor de cualquier fracción entera entre 2 y 16, alineada con la señal CLK0. El PLL sirve como sintetizador y soporta un mayor rango de frecuencias. También es capaz de funcionar en conjunto con los DCM. El corazón del PLL es un oscilador controlado por tensión (VCO) con un rango que va desde los 400Mhz hasta los 1080Mhz. Tres divisores de frecuencia independientes adaptan el PLL a la aplicación que se desee. Bloques BlockRAM. Cada FPGA Spartan-6 contiene entre 12 y 268 BlockRAM de doble puerto, cada uno con capacidad de almacenar 18Kb. Cada uno de estos bloques contiene dos puertos completamente independientes, que solamente comparten la información almacenada. Los accesos a memoria están controlados por la señal de reloj, por lo cual son completamente síncronos. Los datos de salida se almacenan en un registro, que mantiene su valor hasta la siguiente operación. Existe también un registro opcional que proporciona mayores frecuencias de trabajo, a costa de incrementar las operaciones de lectura y escritura en un ciclo de reloj. Cada puerto puede configurarse como 16Kx1, 8Kx2, 4Kx4, 2Kx9 (u 8), 1Kx18 (o 16), o 512x36 (o 32). Algunos de estos modos incluyen salidas con bits de paridad. Cada Block RAM puede configurarse como dos bloques independientes de 9Kb, con un solo puerto de acceso y escritura. Bloques controladores de memoria. Cada FPGA de la familia Spartan-6 tiene bloques dedicados de control de memoria (MCB "Memory Control Block"), para los tipos DDR, DDR2, DDR3, LPDDR (DDR del inglés "Double Data Rate", LP del inglés "Low Power") capaces de soportar transferencias de hasta 800 Mb/s. Estos MCB se conectan a pines predefinidos de la FPGA, y si no se utilizan, dichos pines pueden seguir utilizándose como entradas y salidas de propósito general. Slices DSP48A1. Las aplicaciones de procesamiento de señal requieren el uso de multiplicadores y acumuladores, los cuales están implementados en los DSP48A1. Estos slices dedicados tienen la ventaja de ser de bajo consumo, y totalmente configurables, combinando la alta velocidad con un tamaño reducido. Cada uno de estos bloques se compone de un multiplicador de 18x18 bits, y un acumulador de 48 bits, cada uno de ellos preparado para trabajar a frecuencias de hasta 390Mhz. El acumulador puede usarse también como contador PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 84 5.2 Recursos lógicos en la FPGA Spartan-6 incremental o decremental síncrono, y el multiplicador puede usarse para operaciones de barrelshift. Entradas y salidas. El número de pines de entrada y salida varía desde 102 hasta 576. Cada uno de estos pines es configurable, y soporta una larga lista de estándares, con voltajes de hasta 3.3V. Todos los pines de entrada y salida están organizados en bancos (generalmente de 4 a 6 bancos). Cada banco posee recursos en común, como la fuente de alimentación de salida. Transceptores Gigabit de bajo consumo. La transmisión de datos de alta velocidad entre circuitos integrados se ha vuelto muy popular y de vital importancia hoy en día. Por ello, la familia Spartan-6 dispone de 2 a 8 transceptores de alta velocidad, capaces de transmitir y recibir a velocidades de hasta 3.2Gbps. Transmisor y receptor son circuitos independientes con distintos PLL. El transmisor es básicamente un conversor paralelo-serie con ratio de conversión de 8, 10, 16 o 20. El receptor es un conversor serie-paralelo de las mismas características. Bloques integrados para conexión PCI-Express. La familia Spartan-6 dispone de un bloque integrado capaz de hacer frente a las especificaciones PCI-Express, soportando velocidades de hasta 2.5Gbps por pista y por dirección (transmisión y recepción). La herramienta LogiCORE™ hace uso de esta capacidad y proporciona un asistente para la configuración de estos bloques en caso de que se decidan utilizar. Para más detalles acerca de la familia Spartan-6 de Xilinx, consúltese [63]. Las siguientes referencias proveen extensa documentación sobre conceptos de diseño en Spartan-6, herramientas, técnicas, consideraciones de implementación, y otros aspectos de interés en esta familia de FPGAs [80] [81] [82] [83] [84] [85] [86] [87] [88] [89] [90] [91] [92] [93]. 5.3 Xilinx® Spartan®-6 LX150T Development Kit El Kit de desarrollo LX150T proporciona un entorno completo para el diseño e implementación de prototipos de alto rendimiento. El Kit ofrece una plataforma estable para desarrollar y probar diseños orientados a la familia de FPGA Spartan-6, cuyos recursos son suficientes para desarrollos de sistemas complejos. El Kit incluye diseños de referencia, que permiten al ingeniero partir de una base a la hora de realizar sus diseños, pudiendo acceder de forma fácil a los periféricos de la placa de desarrollo [65]. Figura 5.2. Xilinx® Spartan®-6 LX150T Development Kit [65]. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 85 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK 5.3.1 Características del Kit de desarrollo LX150T Las características principales de esta placa de desarrollo se listan a continuación. x x x x x x x x x x x x x x x x x x x Incluye una FPGA Xilinx Spartan-6 XC6SLX150T-3FGG676C. Dos Conectores de expansión de propósito general de tipo FMC LPC. Conector de tarjetas SD. Conector Avnet LCD Interface (ALI), para pantalla LCD. Conector para transceptores GTP RocketIO™ GTP. Conector tipo SFP cage. Dos tranceptores suministrados a los conectores FMC, para su uso en los módulos de expansión. Conector de ranura para interfaz PCI Express (4 pistas a 2.5 Gbps). Conector SATA servidor. Componente de memoria 128 MB DDR3 SDRAM. Componente de memoria 32 MB FLASH. Puerto serie de comunicaciones RS-232. Puerto USB 2.0. Puerto UART USB-RS232. Puerto Ethernet 10/100/1000. Regulador de alimentación a 5.0, 3.3, 2.5, 1.8, 1.5 y 1.2 V que se deriva del slot PCI Express o desde una fuente externa de 12 V. Reguladores de terminación SSTL2. Memoria de configuración Platform Flash XCF32 y XCF08. Soporte para programación y configuración a través de JTAG. En los siguientes apartados se hará una breve descripción de los elementos principales, indicando aquellos que son indispensables en cualquier sistema de visión. 5.3.2 Diseño funcional Los elementos de la placa de desarrollo LX150T están conectados a los pines de la FPGA de forma predefinida. Aunque es posible realizar cualquier diseño partiendo de cero, el fabricante proporciona un diseño de referencia base con un sistema SCP incrustado (Soft-core Processor), donde se han añadido los bloques básicos de control de los elementos de la placa, así como el procesador Microblaze. En la Figura 5.3 se puede observar el diagrama de bloques de alto nivel que compone el sistema de referencia de la placa de desarrollo. Los bloques amarillos representan elementos hardware situados en la placa de desarrollo, mientras que los bloques azules son los bloques periféricos implementados en la FPGA que controlan estos elementos externos. Cada periférico se comunica con el procesador Microblaze a través del bus PLB (Processor Local Bus), y sus registros ocupan un espacio en el mapa de memoria del procesador, para la tarea de lectura y escritura de los mismos por parte de Microblaze. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 86 5.3 Xilinx Spartan-6 LX150T Development Kit Figura 5.3. Diagrama de bloques de alto nivel del diseño base del Xilinx® Spartan®-6 LX150T Development Kit [65]. Algunos de los periféricos del diseño de referencia han sido creados y configurados desde el asistente para sistemas embebidos (BSB, "Base System Builder"), mientras que otros son plantillas GPIO (General Purpose I/O) que posteriormente han sido modificadas para que desempeñen diferentes tareas, como el manejo de los botones, switches y leds de la placa de desarrollo. Los periféricos de control para el lector de tarjetas SD, el conector SATA o la expansión PCI-Express entre otros, no se incluyen en el diseño de referencia básico, y deberán ser añadidos en caso de necesitarse a través de la herramienta EDK. Este diseño de referencia permite al ingeniero comenzar el proyecto de desarrollo del sistema desde una base, sin necesidad de añadir y configurar todos los elementos básicos de control de la placa. 5.3.3 PCI Express x4 Add-In Card La placa de desarrollo LX150T proporciona una interfaz eléctrica compatible con el estándar PCI-Express. Esta interfaz consta de cuatro pistas, cada una de las cuales incluye un par diferencial de transmisión y recepción. Cada pista soporta velocidades de hasta 2.5Gbps, compatible con la primera generación de PCI-Express. Para proporcionar la señal de reloj de referencia, la placa utiliza un circuito integrado que puede programarse, cuya función es la de atenuador de jitter (ICS874003-05). En la Figura 5.4 se muestra la forma en la que la interfaz PCI-Express se conecta con la FPGA Spartan-6 [65]. El circuito integrado ICS874003-05 proporciona un reloj de referencia que puede configurarse a 100 MHz, 125 MHz, o 250 MHz. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 87 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK Figura 5.4. Diagrama de conexión de la interfaz PCI-Express con la FPGA [65]. 5.3.4 Conector SFP La interfaz SFP (Small Form-factor Pluggable) es un conector tipo "jaula" que se conecta a uno de los transceptores Gigabit (GTP) de la FPGA. Éste permite añadir al sistema conexiones ópticas de alta velocidad, a través de módulos transceptores ópticos al conector SFP. La tarjeta tiene un reloj de referencia específico, totalmente configurable, y la placa está preparada para soportar velocidades de transmisión y recepción de hasta 3.75 Gbps a través de este conector, operando en fibras monomodo o multimodo. Figura 5.5. Conector SFP [65]. 5.3.5 Conector SATA Otro de los transceptores GTP de la FPGA Spartan-6 está conectado a la interfaz SATA, permitiendo añadir al sistema dispositivos de almacenamiento, como por ejemplo un disco duro externo. El conector proporciona sólo la interfaz necesaria para los datos, y el dispositivo que se conecte tendrá que ser alimentado de forma externa. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 88 5.3 Xilinx Spartan-6 LX150T Development Kit 5.3.6 Memoria SDRAM DDR3 128MB Este dispositivo proporciona 128MB de memoria RAM de alta velocidad en un solo circuito integrado, operando a 1.5V. Las señales de la memoria DDR3 están conectadas al banco 4 de la FPGA, tal y como se muestra en la Figura 5.6. Figura 5.6. Interfaz SDRAM DDR3 [65]. 5.3.7 Memoria Paralela Flash 32MB Este elemento es un circuito integrado de expansión (S29GL-P) que proporciona memoria no volátil de 32MB. Esta memoria es de acceso asíncrono, aunque soporta un modo de lectura síncrono para aplicaciones de alto rendimiento. El dispositivo S29GL-P tiene un tiempo de acceso de 110ns, y está conectado a los bancos 1 y 2 de la FPGA. La Figura 5.7 muestra el diagrama de bloques de alto nivel de esta memoria. Figura 5.7. Diagrama de conexión de la memoria Flash 32MB [65]. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 89 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK 5.3.8 Xilinx Platform XCF Configuration Flash La placa de desarrollo tiene otros dos dispositivos de memoria de 32Mb y 8Mb de capacidad, que se utilizan para la configuración de la FPGA, y que se conectan a ésta de tal forma que la configuración se descarga de forma automática al accionar el switch de encendido. 5.3.9 Señales de reloj La placa de desarrollo LX150T posee numerosas fuentes de reloj, para abarcar una gran cantidad de diseños y aportar la flexibilidad necesaria para diferentes tipos de aplicaciones. También existen pines dispuestos para que el diseñador use fuentes externas de reloj para aplicaciones específicas. Los diferentes relojes están dispuestos para derivar las señales hacia los diferentes dispositivos de memoria y de comunicaciones, así como la lógica existente en la placa. La Figura 5.8 muestra un diagrama de conexión de las fuentes de reloj con la FPGA. Figura 5.8. Señales de reloj conectadas a las entradas globales de reloj de la FPGA [65]. Un gran número de estas señales de reloj son generadas gracias a un dispositivo sintetizador de frecuencias (TI CDCM61002 LVDS) que se encuentra en la placa de desarrollo. Las señales generadas por este circuito integrado tienen las siguientes características: x x x x Rango de frecuencias de salida: 43.75 MHz hasta 683.264 MHz. RMS jitter: 0.509 ps. a una frecuencia de 625 MHz. Tiempo de subida y bajada máximo: 255 ps. Duty cycle: Varía dependiendo de la frecuencia de salida. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 90 5.3 Xilinx Spartan-6 LX150T Development Kit 5.3.10 10/100/1000 Ethernet PHY Con el fin de proporcionar interfaces estándar para la comunicación, la placa de desarrollo dispone de un dispositivo transceptor Ethernet de capa física a 10/100/1000 Mb/s, conectado a la FPGA gracias a la interfaz estandarizada GMII. Este dispositivo posee un conector RJ45 para la conexión de un cable de red. El dispositivo que realiza las funciones de capa física Ethernet es un circuito integrado National DP83865DVH Gig PHYTER® V, que trabaja a 1.8V. También existe diversa lógica alrededor, tales como resistencias y leds que informan cuando los datos están transmitiéndose y recibiéndose. La Figura 5.9 muestra de qué forma están conectados estos dispositivos a la FPGA. Existen además algunos jumpers que se utilizan para configurar parámetros de la conexión, tales como activar o desactivar la autonegociación, seleccionar entre una comunicación Full-Duplex o Half-Duplex, o la velocidad del enlace, entre otros. Figura 5.9. Interfaz Ethernet 10/100/1000 Mb/s [65]. 5.3.11 USB 2.0 PHY Al igual que en el caso anterior, la placa de desarrollo cuenta con un dispositivo que implementa la capa física y la interfaz necesaria para una conexión de tipo USB 2.0. El circuito integrado en cuestión es el NXP ISP1504A1, que proporciona una conexión de alta velocidad que soporta tres modos, uno a 480Mbps, otro a 12Mbps y el último a 1.5Mbps. La Figura 5.10 muestra la conexión con la FPGA. Figura 5.10. Interfaz USB 2.0 PHY [65]. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 91 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK 5.3.12 Conector RS232 El transceptor RS232 es un circuito integrado MAX3221, que opera a 3.3V, e internamente genera los voltajes necesarios para cumplir con el estándar de transmisión serie. Los dos canales de datos (TXD y RXD) terminan en un conector tipo DB9. La Figura 5.11 ilustra la forma de conectarse con la FPGA. Figura 5.11. Interfaz RS232 [65]. 5.3.13 USB RS232 UART Bridge Al igual que en el caso anterior, la placa de desarrollo implementa otro transceptor RS232, aunque en este caso es a través de un conector USB. El puente entre USB y RS232 lo proporciona un circuito integrado Cypress CP2102. Este conector USB se utiliza para acceder a la placa de desarrollo a través de un PC que no disponga de conexión serie estándar, utilizando cualquier puerto USB, previa instalación de los drivers que vienen incluidos en el Kit. 5.3.14 Switches y LEDs La placa de desarrollo cuenta también con cuatro botones tipo "push", ocho switches de posición, y ocho leds discretos (sólo pueden estar encendidos o apagados). Estos dispositivos pueden ser usados como elementos de propósito general, como botones de reset, conmutadores de estado, y otras funciones similares. 5.3.15 Puerto de programación JTAG Existen varias formas de configurar la FPGA de la placa de desarrollo. Entre ellas se encuentran la programación JTAG, y la carga del fichero de configuración desde una memoria PROM. Existen cinco dispositivos conectados en la cadena de bloques del conector JTAG, Las memorias de configuración PROM XCF32P y XCF08, la FPGA Spartan-6 y los dos conectores FMC. Dos jumpers situados en la cadena incluyen o excluyen los conectores FMC de la misma (Figura 5.12). PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 92 5.3 Xilinx Spartan-6 LX150T Development Kit Figura 5.12. Conector JTAG [65]. 5.3.16 Buses I2C y otros dispositivos La placa de desarrollo implementa dos buses I2C (Inter Integrated Circuit), cuyo objetivo es establecer una conexión de baja velocidad y pocas líneas entre ciertos dispositivos de la placa. Estos dispositivos pueden conectarse o desconectarse de los buses a través de una serie de jumpers dispuestos como en la Figura 5.13. El primer bus I2C interactúa con los dos conectores FMC, mientras que el segundo accede a los dispositivos Real Time Clock, un sensor de temperatura y la interfaz para el LCD ALI (Avnet LCD Interface). Figura 5.13. Buses I2C [65]. 5.3.16.1 Real-Time Clock Es un dispositivo RTC (Real Time Clock) Maxim DS3232, compuesto por un oscilador de cristal con compensación de temperatura (TXCO), junto a una memoria SRAM de 236 bytes alimentada por una pequeña batería, donde se guardan los registros de configuración del dispositivo. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 93 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK 5.3.16.2 Sensor de temperatura La placa de desarrollo cuenta con un dispositivo Maxim MAX7500 conectado al bus I2C, que ejerce la función de sensor digital de temperatura, con un conversor analógico digital que convierte los datos de temperatura con gran precisión. 5.3.16.3 ALI Interface (Avnet LCD Interface) Existe en la placa una zona con 15 pines especialmente diseñada para conectar una pantalla LCD. ALI es una interfaz desarrollada por el fabricante Avnet Electronics para conectar la placa de desarrollo a una pantalla LCD del tipo "Avnet Display Kit". Figura 5.14. Interfaz ALI [65]. En [73] se encuentra una guía de las especificaciones físicas de esta interfaz, así como una lista de las pantallas LCD que soporta este tipo de conexiones. 5.3.17 Ubicación de componentes en la placa LX150T En la siguiente figura se muestra la ubicación de los diferentes componentes vistos con anterioridad, así como una lista de los jumpers de configuración, que se listarán a continuación. Figura 5.15. Jumpers, componentes y conectores [65]. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 94 5.3 Xilinx Spartan-6 LX150T Development Kit x JP2. Usado para seleccionar el modo de configuración de la FPGA. x JP3. "Flash Write Protect Enable". Usado para proteger la memoria flash contra escritura. x JP8. Usado para configurar el voltaje de salida del banco 0 de la FPGA, que termina en uno de los conectores FMC. Para señales diferenciales, se configura en 2.5V y para señales simples se configura en 3.3V. x JP1. Selecciona el número de pistas del conector PCI-Express que serán detectadas (máximo 4x). Ideal para aplicaciones que necesiten un número menor de pistas. x J4. Permite pull-ups en los pines de I/O de la Spartan-6 cuando se configura. Por defecto está desactivado. x J2. Cuando se conecta un módulo en el conector SFP, este jumper activa para que pueda ser detectado y usado. x JP4 y JP7. Estos dos jumpers actúan en conjunto, y permiten añadir o quitar los conectores JX1 y JX2 a la cadena JTAG, para ser configurados. x JP5 y JP6. Estos dos jumpers actúan en conjunto, y permiten añadir los conectores JX1 y JX2 a un bus I2C global, o separarlos en un bus I2C independiente. x SW1. Este Switch permite a la FPGA que se reconfigure nuevamente, según el método indicado por JP2. x SW12. Permite elegir el modo de alimentación de la placa, a través de un transformador, o directamente a través de los pines PCI-Express. x SW11. Switch de alimentación principal. x SW7 y SW8. Reset principal del dispositivo atenuador de jitter ICS874003-05, y configurador de la frecuencia de salida del dispositivo, respectivamente. x SW9 y SW10. Controlan la frecuencia de salida del sintetizador LVDS CDM6100. x SW2-SW5. Botones Push configurables a través de GPIO. x SW6. Dip-switch de ocho posiciones que pueden ser leídos a través de GPIO. Por defecto están a nivel bajo. 5.4 Tarjetas FMC-IMAGEOV y FMC-DVI Estas dos tarjetas de expansión han sido diseñadas como plug-in adicionales, que se conectan a los conectores FMC de la placa de desarrollo, aportando nuevas características a la misma. El módulo "Dual Image Sensor FMC", o FMC-IMAGEOV es una placa que proporciona dos interfaces de vídeo compatibles con los sensores de imagen Omnivision OV7915. Entre sus características se destacan [71]: x x x x Dos interfaces para sensores de imagen Omnivision que pueden funcionar a la vez. Conector HDMI, que proporciona una interfaz de salida DVI. Sintetizador de reloj de vídeo. Registros de configuración de periféricos (sintetizador de reloj, sensor de imagen, entre otros). x Pines de entrada/salida de propósito general. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 95 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK Figura 5.16. Módulo Dual Image Sensor FMC visto desde abajo y arriba [71]. El módulo DVI I/O FMC es otra tarjeta compatible con la interfaz FMC, que aporta las siguientes características [69]: x x x x x Conector HDMI como interfaz de entrada de vídeo DVI. Conector HDMI como interfaz de salida de vídeo DVI. Interfaz de salida "DisplayPort". Sintetizador de reloj de vídeo independiente. Registros de configuración de periféricos (sintetizador de reloj, entradas y salidas DVI, entre otros). x Pines de entrada/salida de propósito general. Figura 5.17. Módulo DVI I/O FMC [69] 5.5 Sensor de imagen OMNIVISION OV9715 720p El sensor de imagen Omnivision OV9715 está diseñado específicamente para aplicaciones avanzadas de imagen en automoción. Su gran campo de visión y su alta resolución lo hace un elemento ideal para trabajar en sistemas de visión de 360 grados, en sensores de ayuda al aparcamiento o sistemas de aviso en carretera, entre otros. Este sensor de imagen es capaz de trabajar con condiciones de luz mínimas, y sus 3300 mV/lux-seg permite imágenes reales en prácticamente cualquier condición de iluminación [68]. Además, el sensor es altamente configurable, pudiéndose trabajar en diferentes resoluciones y fotogramas por segundo, y teniendo total control sobre el formato de salida y la transferencia de datos. Este sensor es capaz de trabajar a una resolución de 1280x720 píxeles a 30 fotogramas por segundo, pudiendo llegar a 60 fotogramas por segundo para una resolución VGA. Por último, destacar que el sensor de imagen Omnivision OV8715 cumple con las estrictas especificaciones del AEC (Automotive Electronics Council). PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 96 5.6 Sistema completo Figura 5.18. Omnivision OV9715 [68]. 5.6 Sistema completo La placa de desarrollo Spartan-6 LX150T PCI Express Development Kit, junto todos los demás elementos descritos anteriormente, se muestran ensamblados y montados sobre una base de metacrilato, tal y como se aprecia en la Figura 5.19. El sensor de imagen Omnivision se monta sobre un poste flexible, que permite a la cámara mantenerse en cualquier posición. Junto a ella, se encuentran las dos placas de expansión, situadas en los conectores FMC de la placa de desarrollo. El Kit también incluye un programador JTAG, drivers para la conexión RS232-USB con el PC, y un cable de alimentación, formando en su conjunto el sistema de visión Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit. Figura 5.19. El sistema de visión completo montado. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 97 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK 5.7 Repositorio de IP-Cores incluidos El sistema de desarrollo Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit trae un repositorio de PCOREs incluidos (También llamados IP-Cores o simplemente periféricos), para los diseños de referencia y para su implementación en cualquier aplicación. Estos PCOREs se listan a continuación [75]. PCORE Nombre Versión Descripción PCOREs Específicos del sistema Xilinx® Spartan®-6 FPGA IVK 1.01a Controlador de la interfaz Avnet LCD Interface, para pantallas LCD compatibles. fmc_imageov_camera_in IMAGEOV Camara IN 1.02a Bloque que recibe la fuente de vídeo de un sensor de imagen conectado en la tarjeta FMC IMAGEOV y lo convierte en un bus de vídeo XSVI. fmc_imageov_dvi_out IMAGEOV DVI OUT 1.02.c Bloque que transforma una señal de vídeo desde el bus XSVI y la saca por la salida de vídeo DVI de la tarjeta FMC IMAGEOV. ali_controller Controlador Interfaz ALI fmc_dvidp_dvi_in FMC DVI IN 1.02a Recibe la fuente de vídeo de una cámara digital por el conector DVI de la tarjeta FMC DVI y genera un flujo de vídeo por el bus XSVI. fmc_dvidp_dvi_out FMC DVI OUT 1.02.c Bloque que transforma una señal de vídeo desde el bus XSVI y la saca por la salida de vídeo DVI de la tarjeta FMC DVI. ivk_video_det Video Detect 2.01.a Provee una serie de mecanismos para detectar la resolución de vídeo entrante. ivk_video_gen Video Generate 2.01.a Genera señales de sincronismo para varias resoluciones de vídeo. PCOREs creados con System Generator sg_spc_s6_plbw Stuck Pixel Correction 3.01a Implementa un algoritmo de corrección de píxeles atascados. sg_bc_s6_plbw Brightness / Contrast 3.01a Modifica el brillo y el contraste de una fuente de vídeo que llega por un bus XSVI. sg_cfa_s6_plbw Color filter array interpolation 3.01b Implementa un algoritmo de tipo CFA en una fuente de vídeo que llega por un bus XSVI. sg_cc_s6_plbw Color Correction 3.01b Modifica las componentes de color de una fuente de vídeo que llega por un bus XSVI. sg_stats_s6_plbw Statistics 3.01b Provee numerosas estadísticas relacionadas con la imagen. sg_gamma_s6_plbw Gamma Correction 3.01c Implementa un algoritmo de corrección gamma sobre una fuente de vídeo que llega por un bus XSVI. PCOREs adquiridos desde el repositorio Xilinx Video IP vdma Video DMA 1.00a Controlador de acceso directo a memoria (DMA) para un frame buffer situado en una RAM externa. Tabla 5.2. PCOREs incluidos en el repositorio del sistema Xilinx® Spartan®-6 FPGA IVK [75] PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 98 5.8 Diagrama de bloques general 5.8 Diagrama de bloques general El sistema de desarrollo Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit trae varios diseños de referencia que hacen uso de las características más destacadas del Kit. Todos los diseños de referencia comparten una estructura general, donde se establecen algunos periféricos principales controlados por Microblaze. Esta estructura general consta de elementos como: x x x x x x Procesador Microblaze. Buses de memoria y datos. Controlador de memoria. Controlador de conexión UART. Controladores de LEDs, Switches y pulsadores. Controladores de bus I2C. El objetivo de este bloque común es crear un entorno base para el desarrollo de los sistemas de visión, proporcionando un método de conexión de los bloques PCORE a los buses de Microblaze. De esta forma se podrá usar el procesador para rutinas tales como: x Tareas de diagnóstico. x Recepción de mensajes de información de los bloques hardware. x Adquisición de información sobre la transferencia de datos desde las tarjetas de expansión. x Configuración de parámetros y registros de los bloques. x Carga de coeficientes en los filtros. x Reset por software. x Recopilación de estadísticas del sistema. x Envío de mensajes a un PC a través del puerto UART. x Recepción de órdenes enviadas desde un PC y ejecución de las mismas. Figura 5.20. Partes comunes y específicas de los diseños de referencia (figura derivada de [75]). PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 99 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK La parte superior de la Figura 5.20 muestra un diagrama de bloques general de cualquier sistema de visión. Nótese que la estructura común descrita anteriormente no tiene como objetivo realizar ningún procesado de la señal de vídeo, ya que su funcionamiento es por software, y por lo tanto carece de sentido utilizarlo para esta tarea. El procesamiento real del sistema de visión se encuentra en la estructura específica, también ilustrada en la Figura 5.20. Esta estructura específica será la encargada de recibir los datos de vídeo en tiempo real y realizar el tratamiento necesario para la aplicación en cuestión, a través de los periféricos, algunos de los cuales están descritos en la Tabla 5.2. En los diseños de referencia que se verán en el siguiente apartado, se ha obviado la estructura común sin pérdida de generalidad, para hacer más legibles las figuras y entender más fácilmente las características de cada uno de ellos. Sin embargo, no hay que olvidar que lo que se muestra es sólo una parte del sistema, y la estructura común sigue presente en todos los diseños. 5.9 Diseños de referencia En este apartado se verán los diseños de referencia de visión incluidos en el sistema de desarrollo Xilinx® Spartan®-6 FPGA Industrial Video Processing Kit. Existen otros diseños de referencia que hacen uso de otras capacidades de la Placa de desarrollo, implementando sistemas Ethernet, capas TCP/IP, conversores DA/AC, o que hacen uso de la interfaz PCIExpress; sin embargo, el estudio de estos diseños de referencia queda fuera del alcance de este Proyecto Fin de Carrera, que se centra en los sistemas de visión. Los diseños de referencia completos pueden descargarse de [76] y [77], previo registro. A continuación se listan los diseños de referencia incluidos como ejemplos base para un sistema de visión [75]. x Procesamiento de vídeo con entrada DVI. x Procesamiento de vídeo con entrada DVI y frame buffer. x Procesamiento de vídeo con entrada sensor de imagen y frame buffer. En los sucesivos apartados se hará una breve descripción de la funcionalidad de cada uno de estos sistemas de referencia. Téngase en cuenta que, tal y como se mencionó anteriormente, los diagramas de bloques que se mostrarán a continuación sólo corresponden con la estructura específica de cada sistema. La estructura común no aparecerá en las figuras, pero no debe olvidarse que está presente en cada uno de los diseños. Una característica común a todos los diseños de referencia es que, gracias a las tarjetas de expansión FMC y su capacidad para generar múltiples señales de sincronismo y reloj, el sistema admite varios tipos de resolución de vídeo, tal y como se muestra en la siguiente tabla. Resolución Frecuencia de referencia (reloj de píxel) Dimensiones del fotograma VGA 25.125 MHz 640 x 480 SVGA 27.000 MHz 800 x 600 XGA 40.000 MHz 1024 x 768 720p 74.250 MHz 1280 x 720 Tabla 5.3. Resoluciones de vídeo admitidas por los diseños de referencia. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 100 5.9 Diseños de referencia Otra característica común a todos los diseños de referencia es la capacidad de configurar aspectos de la cadena de procesado a través de un PC. Para ello, Microblaze usa el puerto UART de comunicaciones de la placa, para conectarse a un PC que use la aplicación Hyperterminal, tal y como se aprecia en la Figura 5.21. Figura 5.21. Mensajes de información del sistema enviados a Hyperterminal. 5.9.1 Procesamiento de vídeo con entrada DVI Este diseño de referencia tiene como objetivo mostrar las siguientes características. x x x x Captura de vídeo desde una fuente DVI. Realizar tareas de procesamiento de vídeo en tiempo real. Mostrar el vídeo procesado por pantalla. Usar Microblaze para las siguientes tareas: Iniciar los periféricos del sistema. Comunicación con un PC a través de Hyperterminal. Configurar varios aspectos de la cadena de procesado. La Figura 5.22 muestra el diagrama de bloques de este diseño, que incluye dos PCOREs de transformación de gamma [78] y un filtro FIR 5x5 con coeficientes configurables. Figura 5.22. Diagrama de bloques del diseño de referencia base con entrada DVI [75]. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 101 Capítulo 5. El sistema de visión Xilinx Spartan-6 IVK Este sistema se conecta con un PC a través de Microblaze, usando para ello el puerto UART de la placa de desarrollo. Usando Hyperterminal en el PC, se pueden configurar los coeficientes del filtro FIR, así como otros parámetros de interés. 5.9.2 Procesamiento de vídeo con entrada DVI y frame buffer Este diseño ilustra las siguientes capacidades del sistema: x x x x Captura de vídeo desde una fuente DVI. Realizar un buffer del vídeo en la memoria DDR3 externa. Mostrar por pantalla el vídeo desde el buffer. Usar Microblaze para las siguientes tareas: Iniciar los periféricos del sistema. Comunicación con un PC a través de Hyperterminal. Configurar varios aspectos de la cadena de procesado. La Figura 5.23 muestra el diagrama de bloques de este diseño, en el que se han añadido dos PCOREs DMA [79] que controlan el frame buffer, junto al MPMC (Multy-Port Memory Controller) [80]. El PCORE "Video DMA" posee una licencia gratuita que permite su prueba en hardware, y tiene como restricción el cese de su funcionamiento tras un periodo de tiempo determinado. La licencia completa de este IP se puede adquirir desde [64]. Figura 5.22. Diagrama de bloques del diseño de referencia con entrada DVI y frame buffer [75]. 5.9.3 Procesamiento de vídeo con sensor de imagen Este diseño ilustra las siguientes capacidades del sistema: x Captura de un stream de vídeo desde el sensor de imagen. x Realización de una cadena de procesamiento consistente en: SPC. Stuck Pixel Correction. BC. Brillo y contraste CFA. Interpolación Color Filter Array. CC. Corrección de color. STATS. Estadísticas de la imagen. GAMMA. Corrección gamma. x Realizar un buffer del vídeo en la memoria DDR3 externa. x Mostrar el vídeo resultante en una pantalla, a diferente frame rate. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 102 5.9 Diseños de referencia x Usar Microblaze para las siguientes tareas: Iniciar los periféricos del sistema. Comunicación con un PC a través de Hyperterminal. Configurar varios aspectos de la cadena de procesado. La Figura 5.24 muestra el diagrama de bloques de este diseño, en el cual se ha conectado el sensor de imagen Omnivision OV9715 [68] a la tarjeta de expansión FMCIMAGEOV [71]. Figura 5.23. Diagrama de bloques del diseño de referencia con sensor de imagen y frame buffer [75]. El bloque "Camera Imput" provee los codecs necesarios para decodificar el formato BT656 del sensor y generar las señales de sincronismo de vídeo para adaptarlo a las especificaciones del bus XSVI. El bloque "Video Detect" no altera en ninguna forma el vídeo, sino que provee un mecanismo que detecta la resolución de la ventana activa de vídeo (píxeles de información sin contar los espacios de blanking, para posteriormente hacer uso del PCORE Video DMA que guardará el fotograma en una memoria externa. Este diseño de referencia acepta resoluciones de entrada de hasta 1280x720 a 30 f.p.s., mientras que reproduce con una resolución de 1280x720 a 60 f.p.s. Estos parámetros pueden ser configurados a través de Microblaze, y modificados para admitir otras resoluciones, siempre y cuando el sensor las soporte. PROYECTO FIN DE CARRERA. NICOLÁS AGUIRRE DOBERNACK 103