Estructura de Computadores ADVERTENCIA Objetivo

Anuncio

Estructura de Computadores

2.- Representación de la Información

UNIVERSIDAD CARLOS III DE MADRID

Área de Arquitectura y Tecnologí

Tecnolog ía de Computadores

ADVERTENCIA

Este material es un simple guión de la clase: no son

los apuntes de la asignatura.

El conocimiento exclusivo de este material no

garantiza que el alumno pueda alcanzar los objetivos

de la asignatura.

Se recomienda que el alumno utilice los materiales

complementarios propuestos.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 2 –

Objetivo

Conocer las diferencias entre instrucciones y datos.

Conocer las representaciones habituales para

cadenas de caracteres.

Comprender las distintas representaciones numéricas

que puede usar un computador.

Comprender el funcionamiento de las operaciones

aritmética de como fija y coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 3 –

1

Al final de este tema el alumno ...

Será capaz de identificar las propiedades de las

representaciones de caractéres y de cadenas.

Podrá interpretar valores en distintos formatos de

representación numéricos de coma fija y coma

flotante.

Podrá realizar operaciones aritméticas tanto en coma

fija como en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 4 –

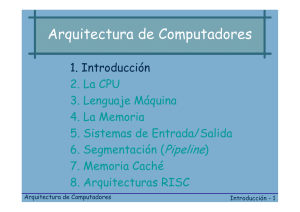

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 5 –

Tipos de información

RESULTADOS

DATOS

INSTRUCCIONES

Flujos de información en el computador:

Flujo de datos.

Flujo de control.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 6 –

2

Tamaños privilegiados

Octeto, carácter o byte.

Representación de un carácter.

Típicamente 8 bits.

Palabra.

Información manipulada en paralelo en el interior del

computador.

Típicamente 32 bits.

Media Palabra.

Doble Palabra.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 7 –

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 8 –

Representación de caracteres

Sistemas:

EBCDIC (8 bits).

ASCII (8 bits).

Unicode (16 bits).

Correspondencia de un código numérico a cada

carácter representado.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 9 –

3

Propiedades

Caracteres de ‘0’ a ‘9’ son consecutivos Simplifica comprobación de dígito.

Simplifica la operación de obtener el valor numérico.

Mayúsculas y minúsculas se diferencia en un bit Simplifica conversión de mayúsculas a minúsculas.

Caracteres de control situados en un rango Simplifica su interpretación.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 10 –

Cadenas

Cadenas de longitud fija.

Cadenas de longitud variable con separador.

Cadenas de longitud variable con longitud en

cabecera.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 11 –

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 12 –

4

Representaciones numéricas

Naturales.

1, 2, 3, ...

Enteros.

..., -3, -2, -1, 0, 1, 2, 3, ...

Racionales

2/5 = 0,4; 1/3 = 0,3333...

Irracionales

√2, π, e

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 13 –

Problema

Cualquier conjunto numérico es infinito.

Números irracionales no son representables por

requerir infinitos dígitos.

Espacio material de representación finito.

Secuencia de n bits 2n códigos distintos.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 14 –

Rango y precisión

Rango.

Intervalo comprendido entre el menor y el mayor número

representable.

Suele ser simétrico se puede indicar el menor y el mayor

número positivo.

En algunos casos (coma flotante) hay hueco entre positivos

y negativos.

Precisión.

No todos los números son representables exactamente.

Algunos números deben aproximarse al representable más

cercano.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 15 –

5

Resolución

Diferencia entre un número representable y el

inmediato siguiente.

Resolución = máximo error cometido en la

representación.

La resolución puede ser:

Constante a lo largo de todo el rango.

Variable a lo largo del rango.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 16 –

Sistema Posicional

Número cadena de dígitos afectados por un factor

de escala.

246,8 = 2 102 + 4 101 + 6 100 + 8 10-1

De forma general, un número X definido por:

Cadena de dígitos.

X = (..., x3, x2, x1, x0, x-1, x-2, x-3, ...)

Cada dígito pertenece a un conjunto de dígitos.

D = {dq-1, dq-2, ..., d1, d0}

Vector de pesos

P = <..., p3, p2, p1, p0, p-1, p-2, p-3, ...>

Valor del número

+∞

V ( x) = ∑ pi ⋅ xi

i =−∞

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 17 –

Sistema posicional con base

Vector de pesos generado a partir de la base b.

P = <..., b3, b2, b1, b0, b-1, b-2, ...>

Valor de X

+∞

V(x) = ∑bi ·xi

Representación

i=−∞

X = (..., x3, x2, x1, x0, x-1, x-2, x-3, ...)b

Bases

b=10 D={0, 1, 2, 3, 4, 5, 6, 7, 8, 9}

b=2 D={0,1}

b=8 D={0, 1, 2, 3, 4, 5, 6, 7}

b=16 D={0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F}

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 18 –

6

Coma fija sin signo / Binario puro

Sistema posicional.

Base 2.

Cadena de n bits.

V ( x) = 2 n −1 · xn −1 + ... + 2 2 · x2 + 2· x1 + 2 0 · x0

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 19 –

Binario Puro – Propiedades

Rango: [0, 2n-1]

Resolución: 1

Posibilidad de desbordamiento en sumas y productos.

No representa números negativos Problemas con

la resta.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 20 –

Coma fija signo-magnitud

Reserva un bit para el signo.

0 signo positivo.

1 signo negativo.

n −2

V ( x ) = ∑ 2i · xi

i =0

si

xn−1 = 0

n−2

V ( x ) = −∑ 2 i · xi

i =0

si

xn −1 = 1

n−2

V ( x) = (1 − 2· xn −1 )∑ 2i · xi

i =0

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 21 –

7

Coma fija signo-magnitud – Propiedades

Rango: [-(2n-1-1), 2n-1-1]

Resolución: 1

Doble representación de cero.

Se debe analizar los bits de signo para ver si la

operación es suma o resta.

Posibilidad de desbordamientos en sumas, restas y

productos.

Dificultad de detección de negativos por doble

representación del cero.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 22 –

Complemento a dos

Números positivos: se usa binario puro.

Números negativos: complemento a dos.

n

Se resta el número de 2 .

1

−

0 0 0 0 0 0 0

0 0 1 1 0 0 1

1 1 0 0 1 1 1

0

0

0

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 23 –

Complemento a dos – Valor

Números positivos

n −1

V ( x) = ∑ 2i · xi

i =0

Números negativos

n −1

V ( x) = −2 n + ∑ 2i · xi

i =0

=

=

xn −1 = 0

n−2

∑ 2 ·x

i

i

i =0

n−2

n−2

i =0

i=0

− 2 n + 2 n −1 + ∑ 2i ·xi = −2 n −1 + ∑ 2i ·xi

xn −1 = 1

Generalización

n−2

V ( x) = − xn −1 2 n−1 + ∑ 2i · xi

i =0

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 24 –

8

Complemento a dos – Propiedades

Rango: [-2n-1, 2n-1-1]

Resolución: 1

No hay doble representación para 0.

Permite suma de números negativos y positivos.

Cambio de signo = complemento a dos.

Resta = suma + complemento a dos.

Puede generar desbordamiento.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 25 –

Complemento a dos: Extensión de signo

Representación de -3 con 8 bits:

11111101 = FD

Representación de -3 con 16 bits:

11111111 11111101 = FFFD

Representación de -3 con 32 bits:

11111111 11111111 11111111 11111101 = FFFFFFFD

Al pasar a representar un valor con más bits:

Se extiende el bit más significativo Extensión de signo

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 26 –

Complemento a uno

Números positivos

Usa binario puro.

Números negativos:

Complemento lógico bit a bit.

0 0 1 1 0 0 1 0

1 1 0 0 1 1 0 1

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 27 –

9

Complemento a uno – Propiedades

Rango: [-2n-1+1, 2n-1-1]

Resolución: 1

Cambio de signo = complemento a uno.

Puede producirse desbordamiento.

Doble representación del cero.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 28 –

Exceso a M

Se incrementa el número en M unidades y se expresa

en binario puro.

Valores típicos de M

2n-1 (n=8 M=128)

2n-1 -1 (n=8 M = 127)

Usada para representar exponentes en

representaciones de coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 29 –

BCD – Sistema Decimal Codificado en

Binario

Convierte uno a uno los dígitos decimales a binario.

Nº bits por dígito = 4

Desperdicio = 37,5%

Evita problemas de redondeo.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

0

0000

1

0001

2

0010

3

0011

4

0100

5

0101

6

0110

7

0111

8

1000

9

1001

Página – 30 –

10

BCD – Signo y coma decimal

Se pueden usar los códigos sobrantes para el signo y

la coma decimal

+73 = 1010 0111 0011

-255 = 1011 0010 0101 0101

1,35 = 1010 0001 1100 0011 0101

Aplicaciones:

Entrada/salida.

Cálculo en ciertas aplicaciones de gestión.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 31 –

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 32 –

Coma flotante

Divide la representación en dos partes:

Mantisa (M): Dígitos significativos del dato.

Exponente (E): Factor de escala con respecto a una base (r).

V(X) = M rE

Representación de n bits

Mantisa: p bits.

Exponente: q bits

exponente

p bits

mantisa

q bits

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 33 –

11

Coma flotante

Mantisa y exponente usan sistemas de coma fija.

Mantisa:

Número entero.

Número fraccionario con coma en posición prefijada.

Exponente:

Base = 2.

Exceso a 2

q-1

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 34 –

Coma flotante con mantisa entera

Coma fraccionaria a la derecha de m0.

q-1

Rango positivo: [0, (2p-1-1)r(2 -1)]

q-1

q-1

Rango negativo: [-r-2 , -2p-1r(2 -1)]

19,375 = 10011,011(2

r = 2.

M = 10011011

E = -3

Sistema en desuso.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 35 –

Coma flotante con mantisa fraccionaria

Mantisa

Coma flotante entre bit de signo y primer bit significativo.

La mantisa suele estar normalizada:

Eliminar ceros por la izquierda.

Ajustar el exponente.

Si se normaliza hasta que el primer dígito sea distinto

de 0, éste puede no almacenarse (bit implícito).

Deja hueco alrededor del 0.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 36 –

12

Estándar IEEE 754

Dos formatos.

Simple precisión

1 bit de signo.

8 bits para exponente.

23 bits para mantisa.

Doble precisión

1 bit de signo.

11 bits para exponente.

52 bits para mantisa.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 37 –

Estándar IEEE 754

Mantisa fraccionaria normalizada sin almacenar el

primer bit (implícito).

Base r=2.

Exponente en exceso a 2q-1-1 (127)

Valores

(-1)s 1,M 2E-127

(-1)s 1,M 2E-1023

0 < E < 255

0 < E < 2047

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 38 –

Ejemplo

Representación del número -0.75

-0.75 = -0.112 = -0.112 x 20 = -1.12 x 2-1

Signo: 1

Mantisa: 0.1

Exponente: 126 (127 – 1)

Representación:

1 01111110 10000000000000000000000

1011 1111 0100 0000 0000 0000 0000 0000

BF80 0000

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 39 –

13

Estandar IEEE 754

E=255, M<>0 NAN = resultado sin sentido.

E=255, M=0 infinito (con signo indicado por bit de

signo).

E=0, M=0 representa al cero.

E=0, M<>0 números pequeños desnormalizados

(-1)s 2-126 0,M

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 40 –

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 41 –

Suma y resta

Suma en complemento a 2.

Se suma bit a bit utilizando acarreo si es necesario.

Resta en complemento a 2.

Se complementa a 2 el sustraendo.

Se suman minuendo y sustraendo.

En ambos casos puede producirse desbordamiento.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 42 –

14

Producto: Algoritmo de Booth

Basado en análisis de bit menos significativo:

00: No se hace nada

01: Sumar multiplicando a mitad izquierda.

10: Restar multiplicando de mitad izquierda.

11: No se hace nada.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 43 –

Ejemplo: Algoritmo de Booth (-7 x 6)

Iteración

Paso

Multiplicando

Producto

Bit anterior

0

Inicial

1001

0000 0110

0

1

00: Nada

1001

0000 0110

0

Desplazar

1001

0000 0011

0

2

3

4

10: Restar

1001

0111 0011

0

Desplazar

1001

0011 1001

1

11: Nada

1001

0011 1001

1

Desplazar

1001

0001 1100

1

01: Sumar

1001

1010 1100

1

Desplazar

1001

1101 0110

0

1101 0110 -0010 1010 -42

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 44 –

División

1. Desplazar resto 1 bit a la izquierda.

2. Alta(resto) Alta(resto) – divisor

3. Si resto <0

1. Alta(resto) Alta(resto) + divisor

2. Desplazar resto a la izquierda rellenando con 0

4. En otro caso

1. Desplazar resto a la izquierda rellenando con 1

5. Si repeticiones < ancho palabra Ir a 2

6. Desplazar Alta(resto) 1 bit a la derecha

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 45 –

15

Ejemplo de división 7 / 2

Iteración

Paso

Divisor

Resto

0

Inicial

0010

0000 0111

Desplazar izda

0010

0000 1110

A(R) A(R) – D

0010

1110 1110

A(R) A(R) + D

0010

0000 1110

Desplazar izda (0)

0010

0001 1100

1

2

3

4

Fin

A(R) A(R) – D

0010

1111 1100

A(R) A(R) + D

0010

0001 1100

0011 1000

Desplazar izda (0)

0010

A(R) A(R) – D

0010

0001 1000

Desplazar izda (1)

0010

0011 0001

A(R) A(R) – D

0010

0001 0001

Desplazar izda (1)

0010

0010 0011

Desplazar dcha A(R)

0010

0001 0011

Resto = 1

Cociente = 3

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 46 –

División: Tratamiento del signo

El algoritmo de división se aplica a los valores

absolutos.

Si los signos de los operando son contrarios se

niega el signo del cociente.

Si el resto es distinto de cero Se le aplica el mismo

signo que al dividendo.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 47 –

Contenido

Tipos de información: instrucciones y datos.

Representaciones numéricas y alfanuméricas.

Representación de caracteres: Código ASCII.

Representación en coma fija.

Representación en coma flotante: estándar IEEE 754.

Aritmética.

Operaciones en coma fija.

Operaciones en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 48 –

16

Suma en coma flotante

1. Desnormalizar el número de menor exponente para

que coincidan los exponentes.

2. Sumar mantisas

3. Repetir hasta que esté normalizado

1. Normalizar el resultado

2. Si hay desbordamiento excepción

3. Redondear mantisa

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 49 –

Ejemplo: Suma

0.5 - 0.4375

0.5 0.1 = 1.0 x 2-1 = 1.0 x 2126-127

X = 0 01111110 00000000000000000000000 = 3F00 0000

-0.4375 -0.0111 = -1.11 x 2-2= -1.11 x 2125-127

Y = 1 01111101 11000000000000000000000 = BDD0 0000

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 50 –

Ejemplo: Desnormalización

E(X) = 01111110

E(Y) = 01111101

E(X) – E(Y) = 00000001

Se desnormaliza Y

-1.11 x 2-2 = -0.111 x 2-1

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 51 –

17

Suma de mantisas y normalización

1.0 + (-0.111) = 0.001

Resultado = 0.001 x 2-1

El resultado está desnormalizado Normalizar

Resultado = 1.0 x 2-4 = 1.0 x 2123-127

1 01111011 00000000000000000000000 = BD80 0000

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 52 –

Producto en coma flotante

1. Sumar los exponentes restando el exceso

2. Multiplicar las mantisas

3. Hasta que el resultado esté normalizado

1. Normalizar el producto

2. Si hay desbordamiento Excepción

3. Redondear la mantisa

4. Determinar el signo del producto

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 53 –

Ejemplo: Producto

0.5 x (-0.4375)

0.5 0.1 = 1.0 x 2-1 = 1.0 x 2126-127

X = 0 01111110 00000000000000000000000 = 3F00 0000

-0.4375 -0.0111 = -1.11 x 2-2= -1.11 x 2125-127

Y = 1 01111101 11000000000000000000000 = BDD0 0000

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 54 –

18

Suma de exponentes con exceso

E(X) = 01111110

E(Y) = 01111101

E(X) + E(Y) - 127= 01111110 + 01111101 01111111 = 01111100 = 124

Exponente 124-127 = -3

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 55 –

Producto de mantisas

1.00 x 1.11 = 1.11

Resultado = 1.11 x 2-3

En este caso ya está normalizado

Signos distintos Resultado negativo

Resultado:

1 01111100 1100000000000000000000 = BD30 0000

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 56 –

Al final de este tema el alumno ...

Será capaz de identificar las propiedades de las

representaciones de caractéres y de cadenas.

Podrá interpretar valores en distintos formatos de

representación numéricos de coma fija y coma

flotante.

Podrá realizar operaciones aritméticas tanto en coma

fija como en coma flotante.

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 57 –

19

Lecturas recomendadas

Estructura y diseño de computadores (Tomo I)

Patterson & Hennessy

Capítulo 4

Fundamentos de los computadores

de Miguel

Capítulo 2

Organización y arquitectura de computadores

Stallings

Capítulo 8

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 58 –

Una historia relacionada

El bug del Pentium (1994/1995) costó a Intel más de

500 millones de dolares.

julio 1994: Intel detecta el fallo planificando los primeros

chips sin fallo para enero de 1995.

El coste de la corrección antes de iniciar la producción era

mínimo 200,000 $.

En septiembre de 1994 el error sale a la luz.

En noviembre de 1994 la noticia acaba en portadas de

periódicos y TV.

En diciembre de 1994: IBM paraliza la producción de PC

basados en Intel.

Intel se ve obligada a asumir su error y sustituir todos los

chips.

Más detalles en Patterson & Hennesssy (292 – 295).

Área de Arquitectura y Tecnolog ía de Computadores

UNIVERSIDAD CARLOS III DE MADRID

Estructura de Computadores – Representación de la información

Curso 2006/2007

Página – 59 –

20