Descarga

Anuncio

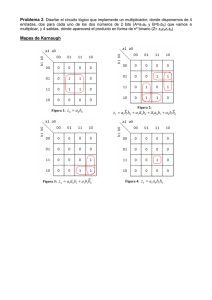

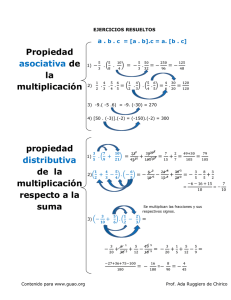

MULTIPLICADOR DE 3 BITS OMAR G N C 1 [email protected] OBJETIVO Diseñar, simular y armar un circuito combinacional multiplicador de dos datos de tres bits cada uno. INTRODUCCION La multiplicación de dos números binarios se hace con papel y lápiz por adiciones sucesivas y corrimientos. Los circuitos multiplic adores son ampliamente usados en sistemas digitales, estos sistemas pueden ser implementados en diversas formas, ya sea en forma combinacional, en forma secuencial mediante el uso de registros y contadores o mediante el uso de un arreglo lógico programable (PLA), esto de acuerdo a recursos y posibilidades. La multiplicación de números binarios se lleva a cabo de la misma forma que la multiplicación de números decimales. En realidad el proceso es más simple, ya que las cifras multiplicadoras son 0 o 1, de modo que siempre se multiplica por cero o por uno y no por otras cifras. El ejemplo siguiente ilustra la multiplicación de números binarios sin signo: La mayoría de las máquinas digitales sólo pueden sumar dos números binarios a la vez, por esta razón, los productos parciales que se forman durante la multiplicación no pueden sumarse todos al mismo tiempo. En su lugar, se suman de dos en dos, es decir, el primero se suma con el segundo, su suma se agrega al tercero y así sucesivamente. Forma de sumar los productos parciales en la multiplicación La multiplicación usando arreglos lógicos combinacionales toman muy poco tiempo. En esta técnica el producto es generado en la misma forma que el proceso de multiplicación manual. Teniendo el producto de dos números binarios: m −1 n−1 A = ∑ ai 2 A = ∑aj 2 j i i=0 j =0 el producto está dado por: m −1 n −1 A = ∑∑ ai b j 2 i + j i =0 j =0 MULTIPLICADOR DE 3 BITS OMAR G N C 2 [email protected] DESARROLLO Llegamos a la idea de desarrollar el multiplicador con sumadores completos, debido a que un circuito puramente combinacional que resolviera la multiplicación sería complejo e ineficiente; otra ventaja es que al usar sumadores de 4 bits logramos resolver no solo un circuito que multiplicara dos números de tres bits, sino que aumentamos a cuatro bits, debido a las características del sumador. Retomando la idea de la introducción, primero resolvimos cada uno de los productos bit a bit y después se fueron sumando correspondientemente los bits del menos significativo al mas significativo. Cabe mencionar que si en una suma se generaba un acarreo, tendríamos la oportunidad de sumarlo en la siguiente cadena de productos. El diagrama del circuito implementado es el siguiente: MULTIPLICADOR DE 3 BITS OMAR G N C 3 [email protected] CONCLUSIONES De la forma en que se implemento el multiplicador, no sólo se logró evitar el empleo de tablas de verdad sino que aumentó 1 bit en la capacidad de multiplicar, debido a esto nuestro multiplicador fue eficiente. BIBLIOGRAFIA Diseño Digital M. Morris Mano Prentice Hall Hispanoamericana Fast and LS TTL Data Motorola