2015 TRABAJO PRACTICO Nº 6: GABINETE SISTEMAS

Anuncio

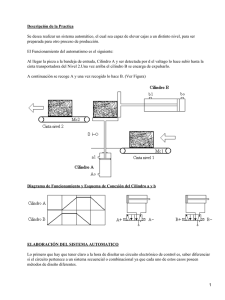

INGENIERIA ELECTRONICA Cátedra Técnicas Digitales I 3º Año 2015 TRABAJO PRACTICO Nº 6: GABINETE SISTEMAS SECUENCIALES: ASINCRONOS-SINCRONOS EJERCICIO Nro 1: Diseñar un sistema secuencial asíncrono para avisador de playas de estacionamiento, de tal forma que se active una señal luminosa cuando los vehículos salen de la playa, no así cuando entran. Se supone que el ingreso y egreso de los vehículos es por el mismo acceso y que el espacio de acceso es tal que no pueden ingresar ni salir dos vehículos al mismo tiempo. Tener en cuenta que el sistema no debe dispararse cuando sale una persona por la misma salida que los vehículos. EJERCICIO Nro 2: Idem anterior pero realizarlo con circuitos biestables SR EJERCICIO Nro 3: Se pretende construir un circuito como el de la figura, el cual podrá actuar como SR, D, T o JK dependiendo del valor de C, y Co (ver tabla). Diséñelo utilizando como único elemento de memoria un biestable tipo T. EJERCICIO Nro 4 :El sistema de apertura de una caja fuerte está compuesto por dos teclas A y B, un circuito secuencial a diseñar y un temporizador que mantiene la caja fuerte abierta durante 5 minutos cuando recibe un nivel lógico 1 desde el circuito secuencial. Este temporizador vuelve a cerrar la caja fuerte pasado dicho tiempo, independientemente del circuito secuencial. Cuando se pulsa la tecla A, se produce un nivel lógico 1 que entra al circuito secuencial, mientras que cuando se pulsa la tecla B se produce un nivel lógico 0 de entrada al circuito a diseñar. Mientras no se pulse ninguna tecla no se genera ningún nivel lógico de entrada al circuito secuencial. Para abrir la caja fuerte, la combinación secreta es: pulsar dos veces seguidas la tecla A, a continuación pulsar una vez la tecla B, y finalmente pulsar una vez la tecla A. Si se hace de esta manera, el circuito secuencial dará una salida a nivel lógico 1, que actuará sobre el temporizador, permitiendo la apertura de la caja fuerte durante 5 minutos. Si en cualquier momento se introdujera un error al pulsar la secuencia secreta, en el siguiente ciclo de reloj todos los biestables se pondrán a cero (el sistema pasará al estado inicial), y la secuencia debe volver a introducirse desde el principio. a) Dibujar el diagrama de estados, explicando claramente en qué consiste cada estado. b) Implementar el circuito secuencial a diseñar usando biestables JK y las puertas necesarias. Técnicas Digitales I - 2015 Trabajo Práctico Nº 6 - Gabinete Página 1 de 2 EJERCICIO Nro 5: Diseñe un chequeador de paridad para caracteres de 4 bits enviados en serie. El circuito recibirá, partiendo de un estado inicial, 4 bits en serie por una línea de entrada, X ; coincidiendo con el cuarto bit, la salida del circuito será 1, si y sólo si el número total de unos recibidos ha sido par. Tras la recepción del cuarto bit, el circuito volverá a aceptar en la entrada un nuevo carácter de 4 bits . Utilice en el diseño biestables D . EJERCICIO Nro 6: Un sistema recibe secuencialmente datos de 1 bit a través de su entrada X. Diseñe un circuito que dé salida Z=1 cuando se haya recibido X=1 durante tres o más intervalos de reloj consecutivos. Dé dos diseños alternativos: a) como autómata de Moore ; b) como autómata de Mealy. Discuta ventajas e inconvenientes de ambos diseños. EJERCICIO Nro 7: Obtenga los biestables JK y T a partir de un biestable D . EJERCICIO Nro 8: Para el circuito de la figura, dibuje la forma de onda de la salida para las secuencias que se muestran. Supongamos que el sistema parte del estado (q1,q2,q3,) = (0,0,0) oooOOOooo Técnicas Digitales I - 2015 Trabajo Práctico Nº 6 - Gabinete Página 2 de 2