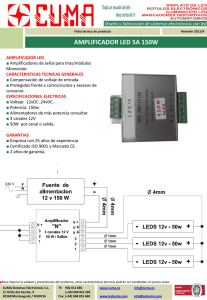

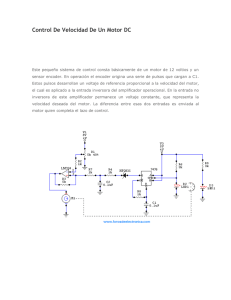

Diseño de etapa de amplificación y adecuación de señal en un

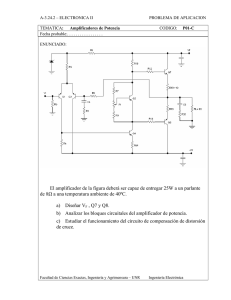

Anuncio