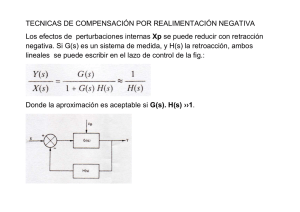

controlador de histéresis de bajo coste para convertidor buck

Anuncio