Informe - Escuela de Ingeniería Eléctrica

Anuncio

Universidad de Costa Rica

Facultad de Ingeniería

Escuela de Ingeniería Eléctrica

IE – 0502 Proyecto Eléctrico

Compuertas lógicas ópticas

Por:

Pierre van der Laat Ulate, 943654

Ciudad Universitaria Rodrigo Facio

Diciembre del 2007

Compuertas lógicas ópticas

Por:

Pierre van der Laat Ulate

Sometido a la Escuela de Ingeniería Eléctrica

de la Facultad de Ingeniería

de la Universidad de Costa Rica

como requisito parcial para optar por el grado de:

BACHILLER EN INGENIERÍA ELÉCTRICA

Aprobado por el Tribunal:

_________________________________

Ing. Luís Diego Marín Naranjo

Profesor Guía

_________________________________

Ing. Ignacio Ramírez Antillón

Profesor lector

_________________________________

Ing. Jaime Allen Flores

Profesor lector

ii

DEDICATORIA

A Dios, el único que nunca se equivoca, porque todos nosotros nos equivocamos

una y mil veces.

A mis padres, por su apoyo.

A mis profesores y a la Universidad de Costa Rica por haberme educado.

iii

ÍNDICE GENERAL

ÍNDICE DE FIGURAS...................................................................................vi

ÍNDICE DE TABLAS.................................................................................. viii

NOMENCLATURA........................................................................................ix

RESUMEN........................................................................................................x

CAPÍTULO 1: Introducción ...........................................................................1

1.1

Objetivos.................................................................................................................5

1.1.1

Objetivo general..............................................................................................5

1.1.2

Objetivos específicos ......................................................................................5

1.2

Metodología ............................................................................................................5

CAPÍTULO 2: Desarrollo teórico ..................................................................6

2.1

2.2

2.3

2.4

2.5

Compuertas lógicas optoelectrónicas con interferencia no-coherente....................7

2.1.1

Relaciones importantes en el desarrollo de las compuertas lógicas ópticas de

n-entradas......................................................................................................................13

2.1.2

Ecuaciones que rigen las compuertas ‘OR’, ‘NOR’, ‘AND’, ’NAND’ .......14

2.1.3

El ‘OR’ optoelectrónico................................................................................16

2.1.4

El ‘NAND’ optoelectrónico..........................................................................19

2.1.5

Compuertas ‘NOR’ y ‘AND’ optoelectrónicas ............................................22

Compuertas lógicas optoelectrónicas con interferencia coherente .......................23

Análisis teórico de la velocidad de conmutación y procesamiento de datos ........24

Fototransistores .....................................................................................................35

Fotorresistencias ...................................................................................................39

CAPÍTULO 3: Informes................................................................................40

3.1

Informe de la construcción de dos compuertas AND optoelectrónicas................40

3.2

Informe del diseño de compuertas optoelectrónicas utilizando interferencia

constructiva de ondas no-coherentes. ...................................................................................44

3.3

Informe del diseño de compuertas optoelectrónicas utilizando interferencia

constructiva de ondas no-coherentes. ...................................................................................46

CAPÍTULO 4: Conclusiones y recomendaciones .......................................47

BIBLIOGRAFÍA............................................................................................51

APÉNDICE A .................................................................................................53

A.1

Suma de ondas electromagnéticas coherentes: .....................................................53

iv

A.2

A.3

Suma de ondas electromagnéticas no-coherentes .................................................55

Interferencia de ondas electromagnéticas coherentes con desfase de 0° y 180°: .56

A.3.1

Ecuaciones para un desfase de 0°: ................................................................57

A.3.2

Ecuaciones para un desfase de 180°: ............................................................58

APÉNDICE B .................................................................................................59

B.1 Demostración del algoritmo de la sección 2.1.3 ............................................................59

B.2 Demostración del algoritmo de la sección 2.1.4 ............................................................60

APÉNDICE C .................................................................................................62

C.1

Demostración del mejor caso para compuertas optoelectrónicas. ........................62

C.2 Demostración de resultados de la sección 2.3................................................................66

C.2.1

Demostración de las desigualdades f 1 < f 2 (ecuación (2.3-16)) .................66

C.2.2 Demostración de la desigualdad f 3 < f 1 : ..........................................................69

APÉNDICE C .................................................................................................72

C.1

MUESTRAS Y ORDENACIONES .....................................................................72

ANEXO 1 ........................................................................................................76

1.1

1.2

Código fuente en MatLab 6.5 de Figura 2.14 .......................................................76

Código en MatLab para Figura C.1 ......................................................................78

ANEXO 2 ........................................................................................................80

2.1 Fotos de las compuertas de la sección 3.1. .....................................................................80

ANEXO 3 ........................................................................................................85

3.1 Datos del fabricante para componentes. .........................................................................85

v

ÍNDICE DE FIGURAS

Figura 1.1. Desarrollo del número de transistores en los procesadores de INTEL y la ley

de Moore. ............................................................................................................................2

Figura 2.1. (a) Circuito comúnmente utilizado para el fotodiodo detector, y que se

propuso inicialmente para el diseño de las compuertas OR y NAND. (b) Circuito del

comparador ventana, cuya salida estará en alto cuando la señal del fotodiodo esté entre

los valores deseados............................................................................................................8

Figura 2.2. (a) Entrada láser modulada por interferómetro Mach-Zehnder. (b) Entrada

LED modulada por corriente. ...........................................................................................10

Figura 2.3. (a) Recta característica de Potencia Óptica vrs. Corriente para los diodos

emisores de luz o LED’s. (b) Curva característica de Potencia Óptica vrs. Corriente

según la temperatura ambiente para el diodo láser. (c) Modulación digital del diodo

láser. ..................................................................................................................................11

Figura 2.4. Curva característica para el interferómetro Mach-Zehnder...........................12

Figura 2.5. (a) Diagrama de bloques para construir compuertas con láseres. (b)

Diagrama de bloques para construir compuertas con LED’s. El inversor electrónico se

coloca sólo cuando es necesario. ......................................................................................13

Figura 2.6 Circuito detector para el “OR” optoelectrónico. La flecha negra indica el

fotodiodo. ..........................................................................................................................16

Figura 2.7. Diagrama de bloques del circuito que NO INVIERTE la entrada. (a) Con

láser. (b) Con LED...........................................................................................................17

Figura 2.8. Diagrama de bloques del circuito que INVIERTE la entrada. . (a) Con láser.

(b) Con LED. ....................................................................................................................17

Figura 2.9. Circuito detector del ‘NAND’ optoelectrónico. Las flechas negras indican el

fotodiodo. ..........................................................................................................................19

Figura 2.10. Diagrama de bloques del circuito que INVIERTE la entrada para el bit ‘m’

NO NEGADO en ‘S’=0, (a) con láser, (b) con LED. .......................................................20

Figura 2.11. Diagrama de bloques del circuito que NO INVIERTE la entrada para el bit

‘l’ NEGADO en ‘S’=0, (a) con láser, (b) con LED. .........................................................20

Figura 2.12. Circuito detector del fotodiodo para las compuertas ‘NOR’ y ‘AND’. ......22

Figura 2.13. Circuitos equivalentes entre sí. (b) Circuito equivalente del fotodiodo. ....27

vi

Figura 2.14. Gráfico de las funciones f 1 , f 2 , y f 3 (ecuaciones (2.3-11), (2.3-14) y (2.312) respectivamente), para el ejemplo con Imax = 10mA, C = 1pF, Vcc = 5V, y n1 de 2 a

171 bits. Aquí se utiliza la función gamma. ....................................................................33

Figura 2.15. Conexiones externas hechas a un fototransistor n-p-n. (a) Radiación

absorbida en la región de la base causa que se fluya una corriente del emisor a través de

la resistencia de carga RL y por tanto aparecerá un voltaje de señal en ella. (b) Las

corrientes que se asumen fluyen en el fototransistor. .......................................................37

Figura 2.16.Estructura n-p-n del fototransistor basado en una heterounión InGaAsP/InP.

..........................................................................................................................................38

Figura 3.1. Circuito emisor con IRLED’s para los arreglos de la figura 3.2 y la Figura

3.3. ....................................................................................................................................41

Figura 3.2. Circuito emisor IRLED (izquierda), y circuito detector con fotorresistencias

y LED (LED genérico visible como indicador de salida).................................................42

Figura 3.3. Circuito emisor IRLED (izquierda), y circuito detector con fototransistores y

LED (LED verde como indicador de salida). ...................................................................43

Figura C.1 Gráfica de la función (C.1-1), para ‘n’=0 a 15. ..............................................63

Figura Anexo.2.1.1. Foto del arreglo optoelectrónico con fotorresistencias para el caso

en que ambas entradas están en bajo. LED verde apagado..............................................80

Figura Anexo.2.1.2. Foto del arreglo optoelectrónico con fotorresistencias para el caso

en que la primera de las entradas están en bajo, y la segunda de las entradas están en

bajo. LED verde apagado.................................................................................................81

Figura Anexo.2.1.3. Foto del arreglo optoelectrónico con fotorresistencias para el caso

en que la primera de las entradas estaba en alto, y la segunda de las entradas están en

bajo. LED verde apagado.................................................................................................81

Figura Anexo.2.1.4. Foto del arreglo optoelectrónico con fotorresistencias para el caso

en que ambas entradas están en alto, y se observa el LED verde encendido....................82

Figura Anexo.2.1.5. Foto del arreglo optoelectrónico con fototransistores para el caso en

que ambas entradas están en bajo. LED verde apagado. .................................................82

Figura Anexo.2.1.6. Foto del arreglo optoelectrónico con fototransistores para el caso en

que la primera entrada está en bajo y la segunda en alto. LED verde apagado. ..............83

Figura Anexo.2.1.7. Foto del arreglo optoelectrónico con fototransistores para el caso en

que la primera entrada está en alto y la segunda está en bajo. LED verde apagado........83

Figura Anexo.2.1.8. Foto del arreglo optoelectrónico con fototransistores para el caso

en que ambas entradas están en alto, y se observa el LED verde encendido....................84

vii

ÍNDICE DE TABLAS

Tabla 2.1. Tabla de verdad de las entradas y las salidas del circuito de la figura 2.1 (a). .7

Tabla 2.2. Tabla de verdad del circuito de la Figura 2.6. .................................................16

Tabla 2.3 Ejemplo para S= x3' + x2' + x1 .............................................................................18

Tabla 2.4. Tabla de verdad del circuito de la figura 2.9. .................................................19

Tabla 2.5 Ejemplo para ( x3' x2' x1 )’. ....................................................................................21

Tabla 2.6. Algunos resultados tabulados de las funciones f 1 , f 2 , y f 3 (ecuaciones (2.311), (2.3-14), y (2.3-12) respectivamente). Note que las frecuencias son las frecuencias

equivalentes para la compuerta de principio a fin y se consideró el peor caso para la

compuerta electrónica. Para estos datos se tomaron los valores Imax = 10mA, C = 1pF,

Vcc = 5V, y n1 de 2 a 128 bits de entrada. .......................................................................34

Tabla 3.1. Tabla de verdad de la compuerta AND con fotorresistencias del circuito de la

figura 3.2, y la Figura 3.3..................................................................................................42

Tabla Anexo.3.1.1. Datos del fabricante para uno de los fototransistores de la Figura 3.3.

Parte # 276-142 de Radio Shack.......................................................................................86

Tabla Anexo.3.1.2. Datos de cada IRLED. Parte #276-142 de Radio Shack.................86

viii

NOMENCLATURA

Rango(A)

Rango de la matriz A.

N

Conjunto de los números naturales ({0, 1, 2, 3, …})

x∈N

El elemento x pertenece al conjunto de números naturales.

‘S’

Salida de la interferencia constructiva o destructiva de todas las

entradas ópticas.

S

Salida de la compuerta lógica

bi

Resultado de la i-ésima ecuación de la matriz.

xi

i-ésimo bit significativo de los datos de entrada.

xm

Bit m-ésimo que NO está NEGADO en ‘S’ en bajo.

xl'

Bit l-ésimo que está NEGADO en ‘S’ en bajo.

C

Variable de ‘control’ utilizada para obtener un valor deseado en ‘S’,

tiene un valor constante en la tabla de verdad.

c

Valor de la variable C en el sistema.

∞

n!= Γ(n) = ∫ t n −1e −t ∂t

Función “factorial” o función “gamma”, definida para

0

números complejos, en nuestro caso los podemos

considerar tanto reales como enteros positivos.

ix

RESUMEN

El objetivo principal de este trabajo fue demostrar un principio de funcionamiento

de compuertas lógicas ópticas. Este objetivo fue llevado a cabo mediante dos modalidades

principales de compuertas optoelectrónicas:

•

Con fotodiodos.

•

Con fototransistores o fotorresistencias.

El primero fue estudiado desde el punto de vista teórico y comprende

principalmente su aplicación a compuertas de 2 ó más entradas. En la sección 2.3 se

analiza desde el punto de vista teórico-matemático los arreglos optoelectrónicos con

fotodiodos, demostrándose que los circuitos electrónicos superan a estos diseños

optoelectrónicos por al menos poco más de un orden de magnitud, bajo especificaciones

similares de velocidad de conmutación de los componentes. Por lo tanto aún cuando la

óptica puede superar la electrónica en cuanto a velocidad de ancho de banda, para que los

diseños de las secciones 2.1 y 2.2 tomen valor, los fotodetectores deberían superar a la

electrónica en al menos cerca de dos órdenes de magnitud.

Para el segundo punto, que se planteó como un objetivo extra, se analizó

brevemente, y se armó un experimento demostrativo basado en un diseño de la referencia 7.

Este arreglo óptico se pretende utilizar como experimento demostrativo para el LAFTLA.

Por fin, con esto se demostró que se pueden utilizar circuitos relativamente sencillos para

armar una compuerta lógica AND optoelectrónica de dos entradas.

x

CAPÍTULO 1: Introducción

La carrera para la creación de computadoras más potentes y más rápidas viene

dándose desde hace varias décadas. Esta carrera se ve mejor resumida en la Ley de Moore.

“En 1965 Gordon Moore afirmó que la tecnología tenía futuro, que el número de

transistores por pulgada en circuitos integrados se duplicaba cada año y que la tendencia

continuaría durante las siguientes dos décadas.

Algo más tarde modificó su propia ley al afirmar que el ritmo bajaría, y la densidad

de los datos se doblarían aproximadamente cada 18 meses. Esta progresión de crecimiento

exponencial, doblar la capacidad de los microprocesadores cada año y medio, es lo que se

considera la Ley de Moore.” 1

La figura 1.1 muestra la progresión del número de

transistores en los procesadores Intel.

Sin embargo, ya han pasado más de dos décadas, y en general la ley se siguió

cumpliendo. Entonces, ¿tiene límite la velocidad y densidad de los transistores en los

procesadores? Pues bien, la respuesta no es sencilla. Aunque por un lado, en la actualidad,

en el mercado se consiguen procesadores INTEL de alrededor de poco más de 3 GHz,

también es cierto que existen transistores capaces de conmutar a velocidades superiores a

los 800 GHz en laboratorios especializados2 y bajo condiciones especiales.

1

2

Ver referencia 5

Ver referencia 6

1

2

Figura 1.1. Desarrollo del número de transistores en los procesadores de INTEL y la

ley de Moore3.

Sin embargo, en el caso de la electrónica, se tiene la desventaja de que estos

transistores con los que se pueden construir compuertas lógicas, lo hacen muy bien para

compuertas lógicas de dos entradas y una salida, mientras que en los buses de datos (que

pueden considerarse como compuertas lógicas de más de dos entradas y si es necesario de

más de una salida) empiezan a tener un desempeño cada vez más pobre conforme aumenta

el número de entradas y salidas.

Es esta una de las posibles aplicaciones donde pudiera llegar a ser importante la

óptica para los procesadores. Debido a que las guías de onda, con su tamaño reducido y

capacidad actual de transmisión a altísimas velocidades (fácilmente a 10 GHz, aunque a un

precio aún no tan bajo), se convierte en una opción importante para la implementación de

2

3

los buses de datos (como las memorias RAM) y líneas de transmisión entre transistores que

se encuentren a “largas distancias entre sí” dentro de los procesadores. Y es que en los

últimos años se ha venido desarrollando enormemente la industria de la optoelectrónica, no

sólo con las guías de onda monomodo sobre silicio, sino también, con láseres bombeados

eléctricamente que son construidos virtualmente dentro de las capas de silicio 4 , y que

eliminan la necesidad de alineamientos manuales, que son costosos y engorrosos, y que

sirven para alinear el láser y la guía de onda. Inclusive, se sabe5 que mediante métodos

similares también se pueden construir moduladores de fase electro-ópticos y elementos nolineales tales como los SOA’s (Semiconductor Optical Amplifier), limpiando el camino

hacia la implementación de funciones lógicas complejas en “chips optoelectrónicos”.

A lo largo de este trabajo, se expone un modelo matemático, para aplicar algunas de

estas nuevas tecnologías y determinar la mejor manera de implementar “chips

optoelectrónicos”. Para lo anterior se usaron dos enfoques principales:

•

La optoelectrónica, con base en la interferencia constructiva de ondas

electromagnéticas no coherentes

•

Y la optoelectrónica, con base en la interferencia constructiva y

destructiva de ondas electromagnéticas coherentes.

Para el diseño mediante la tecnología optoelectrónica con base en la interferencia

constructiva no coherente, se pretende desarrollar una base teórica para poder implementar

casi cualquier tipo de compuerta lógica. Esta tecnología tiene la ventaja potencial de

3

4

Ver referencia 5.

Ver referencia 8 y 13.

3

4

poderse implementar mintérminos de 2 ó más entradas en una sola unidad y que permitiría

realizar en 1 solo ciclo operaciones que normalmente requerirían de 2 a más ciclos en total.

Para el diseño de la tecnología optoelectrónica con base en interferencia

constructiva y destructiva de ondas electromagnéticas coherentes, también se pretende

desarrollar una base teórica para la implementación de varias funciones lógicas, inclusive

con algunas funciones de más de un mintérmino, y que en algunos casos se podrían realizar

en sólo 1 ciclo.

Finalmente como aplicaciones a los temas aquí tratados tenemos para las

compuertas lógicas optoelectrónicas en general:

5

•

Bus de datos.

•

Matrices de memorias RAM.

•

Demultiplexores.

•

Routers.

•

Etc.

Ver referencia 9.

4

1.1 Objetivos

1.1.1

Objetivo general

•

Demostrar teóricamente un principio de funcionamiento para

compuertas lógicas ópticas.

1.1.2

Objetivos específicos

•

Demostrar de manera teórica un principio de funcionamiento a

partir de elementos ópticos y optoelectrónicos de cuatro

compuertas lógicas básicas:

o AND

o NAND

o OR

o NOR

1.2 Metodología

La metodología a seguir es de estudio teórico de algunos casos representativos de la

posibilidad de implementación de compuertas lógicas de básicamente 2 tipos:

•

La optoelectrónica, con base en la interferencia constructiva nocoherente de ondas electromagnéticas no-coherentes.

•

La optoelectrónica, con base en la interferencia constructiva y

destructiva de ondas electromagnéticas coherentes.

5

CAPÍTULO 2: Desarrollo teórico

Inicialmente se pensó en diseñar compuertas lógicas ópticas con elementos

optoelectrónicos que fuesen capaces de realizar, en un solo ciclo, lo que requiere de

muchos ciclos en las compuertas electrónicas tradicionales. Conforme se avanzó en el

desarrollo de estas ideas se encontraron varias limitantes teóricas que hacen que estas

compuertas lógicas, con el diseño que se planteó inicialmente, no fuesen viables desde el

punto de vista práctico.

En la sección 2.1 se incluyeron los lineamientos básicos para el diseño de las 4

compuertas lógicas básicas optoelectrónicas (a saber ‘OR’, ’NOR’, ’AND’, y ’NAND’).

En la sección 2.2, se aborda brevemente el tema de compuertas lógicas

optoelectrónicas basadas en interferencia coherente de ondas electromagnéticas, así como

un ejemplo de una compuerta.

En la sección 2.3 se incluyó una demostración teórico-matemática de porqué las

compuertas electrónicas de dos entradas (o ¿por qué no también, las compuertas ópticas de

dos entradas?) son, bajo condiciones similares de ancho de banda de los componentes,

mucho más veloces que las compuertas lógicas optoelectrónicas basadas en un principio

decodificación analógico.

6

7

2.1

Compuertas lógicas optoelectrónicas con interferencia no-coherente

En la bibliografía se encuentran reportes de LED’s que conmutan a velocidades de

hasta 4GHz6 y que podrían ser utilizados para la construcción de chips de memoria con

tecnología LED o láser, como por ejemplo se hace con los optoacopladores. O también se

pueden construir compuertas lógicas con el diseño que aquí se propuso. Para este diseño se

utilizó la teoría de interferencia no-coherente del Apéndice A.

En general se propuso un circuito muy utilizado para el fotodiodo detector, este se

muestra en la figura 2.1 (a) y (b).

Tabla 2.1. Tabla de verdad de las entradas y las salidas del circuito de la figura 2.1

(a).

6

Número de entradas en ‘on’

Salida

0

0

1 ó más

1

Ver referencia 11

7

8

D119

V+

8

U5A

3

+

V1

2

R3

5Vdc

-

LF353/NS

Salida

4

4k

5Vdc

1

V-

OUT

V3

V4

Vdc

Vdc

0

(a)

V+

8

U7A

3

+

R5

1

4

Vdc

OUT

2

V7

LF353/NS

V-

1k

V6

D120

5Vdc

0

R4

0

U6A

8

V8

3

+

V+

1k

Vdc

R6

0 2

R7

1

1k

-

R8

V-

1k

OUT

Salida

1k

4

LF353/NS

0

(b)

Figura 2.1. (a) Circuito comúnmente utilizado para el fotodiodo detector, y que se

propuso inicialmente para el diseño de las compuertas OR y NAND. (b) Circuito del

comparador ventana, cuya salida estará en alto cuando la señal del fotodiodo esté

entre los valores deseados.

Los detectores de la figura 2.1 constan de una fuente de polarización que alimenta

un fotodiodo y una resistencia, la resistencia sirve para convertir en voltaje la corriente del

fotodiodo. Por otro lado, el amplificador operacional en modo comparador, sirve para

comparar el voltaje producido por la corriente del fotodiodo con un voltaje dado que, por

8

9

ejemplo en el caso de una compuerta OR, podría indicar cuando en la entrada hay sólo una

entrada en alto, o sólo dos entradas en alto, y así por el estilo.

En lugar de un solo amplificador operacional también se pueden agregar varios en

paralelo en configuración comparador ventana, de manera que cuando el voltaje producido

por la corriente del fotodiodo que pasa por la resistencia está entre dos niveles dados se

produce una salida en alto en esa parte del circuito. Lo anterior funciona en general como

un convertidor analógico-digital. El detalle, está en que cambiando la función de entrada,

invirtiendo (por medio de un inversor electrónico) o dejando sin invertir la entrada, se

cambia también, la función de salida. Para estos casos, hay que tomar en cuenta que no se

pueden alimentar un número ilimitado de amplificadores operacionales por cuanto estos

consumen corriente que, aunque poca, le resta fuerza a la señal del fotodiodo.

Por otro lado, en las compuertas, inicialmente se consideró como posibles fuentes

de luz para implementar la entrada de la compuerta lógica optoelectrónica un láser CW

(onda continua, por sus siglas en inglés) modulado por una interferómetro Mach-Zehnder, o

en su defecto, un LED controlado por corriente, como en la figura 2.2. Con respecto al

láser, estos se modulan por medio de un interferómetro Mach-Zehnder, y no por corriente,

debido a la llamada corriente de umbral que es la corriente mínima necesaria para que un

láser empiece a emitir luz coherente y entre en la llamada zona lineal. La ecuación

característica del interferómetro Mach-Zehnder es la ecuación (2.1-1) y su gráfico (donde

‘ Vπ ’ se llama voltaje de media onda, y se refiere al voltaje necesario para que el ángulo de

desfase entre las trayectorias sea igual a 180°), se encuentra en la figura 2.4, mientras tanto,

9

10

el gráfico característico de la recta Corriente vrs. Potencia Óptica del LED es lineal, su

función es la ecuación (2.1-2) y se muestra en la figura 2.3.

πV

Pout

= 0.51 + cos

Pin

Vπ

(2.1-1)

En la ecuación (2.1-1) ‘Pout’ es la irradiancia de salida del interferómetro de MachZehnder (ver figura 2.4), ‘Pin’ es la irradiancia de entrada, ‘V’ es el voltaje aplicado a los

terminales del interferómetro.

(2.1-2)

P = ηiW g

En la ecuación (2.1-2) ‘P’ es la potencia óptica de salida del LED, ‘i’ es la carga

(corriente) inyectada por segundo, y ‘Wg’ es la energía de hueco del material (entre los

niveles de energía).

Por lo que queda demostrada la respuesta lineal de la relación

Potencia-Corriente en el LED.

Interferómetro.

Mach-Zehnder

Láser CW

(a)

(b)

Figura 2.2. (a) Entrada láser modulada por interferómetro Mach-Zehnder. (b)

Entrada LED modulada por corriente.

Como se muestra en la figura 2.3 (b) y (c), la potencia óptica equivalente a un cero

lógico en la modulación digital de un diodo láser, es considerable, y de ahí la importancia

10

11

del interferómetro Mach-Zehnder, ya que este provee un cero lógico con una potencia

relativa mucho menor al de la modulación digital.

(a)

(b)

(c)

Figura 2.3. (a) Recta característica de Potencia Óptica vrs. Corriente para los diodos

emisores de luz o LED’s7. (b) Curva característica de Potencia Óptica vrs. Corriente

según la temperatura ambiente para el diodo láser8. (c) Modulación digital del diodo

láser9.

7

Ver referencia [6]

Ver referencia [6]

9

Ver referencia [6]

8

11

12

Figura 2.4. Curva característica para el interferómetro Mach-Zehnder10.

El arreglo óptico general en que se pensó para construir las compuertas lógicas

ópticas fue el de la figura 2.5. En la figura 2.5(a) y (b) el inversor electrónico es para

aquellas compuertas lógicas en que se invierte la entrada a la compuerta, y por ende debe

estar sólo en caso necesario. Además se puede agregar un prisma, un acoplador de fibra

óptica, o un acoplador de guía de onda para unir las ondas electromagnéticas antes de ser

detectadas por el fotodiodo dependiendo del medio en que se esparzan las ondas. La suma

de las irradiancias no-coherentes debió ser tal que no se dañara el fotodiodo por exceso de

radiación; y la suma de las irradiancias de los emisores en bajo debió ser tal que, fuera

menor a cuando hay sólo un emisor en alto.

10

Ver referencia [6]

12

13

Entrada

X1

Entrada

Xn

Inversor

electrónico

(opcional)

Inversor

electrónico

(opcional)

Interf.

MachZehnder

Fotodiodo

detector

Circuito

electrónico

Fotodiodo

detector

Circuito

electrónico

Interf.

MachZehnder

(a)

Entrada

X1

Entrada

Xn

Inversor

electrónico

(opcional)

Inversor

electrónico

(opcional)

LED

LED

(b)

Figura 2.5. (a) Diagrama de bloques para construir compuertas con láseres. (b)

Diagrama de bloques para construir compuertas con LED’s. El inversor electrónico

se coloca sólo cuando es necesario.

2.1.1

Relaciones importantes en el desarrollo de las compuertas lógicas ópticas de nentradas

En los Apéndices A.1, A.2 y A.3 se demostró la interferencia de haces coherentes,

no-coherentes, y coherentes con desfases de 0° y 180°, respectivamente. Recordemos que

la irradiancia de la luz es proporcional al cuadrado del campo eléctrico multiplicado por

13

14

una constante, sin embargo, para nuestros efectos consideramos en la sección 2.1 la onda

electromagnética como no-coherente, como lo es la luz de dos LED’s o dos láseres

diferentes. En el apéndice A se demostró que la intensidad de la suma de las ondas en la

vida real varia entre, la suma de los cuadrados de los campos eléctricos multiplicado por

una constante y, el cuadrado de la suma de los campos eléctricos multiplicados por una

constante (ver Apéndices A.1 y A.2).

2.1.2

Ecuaciones que rigen las compuertas ‘OR’, ‘NOR’, ‘AND’, ’NAND’

Para calcular la irradiancia resultante, en este capítulo 2 se asumió el caso de

interferencia no-coherentes (ver apéndice A.2), es decir, que la irradiancia resultante es

igual a la suma de las irradiancias.

Con el sistema de ecuaciones, formado por los valores de los bits de entrada según

la tabla de verdad, se pudo definir una matriz de la forma (2.1.2-1).

1

M

M

0

0

M

0

0

K

O

K

K

K

O

K

K

0

M

1

0

0

M

0

0

0

M

0

1

0

M

0

0

0

M

0

0

1

M

0

0

K

O

K

K

K

O

K

K

0

M

0

0

0

M

1

0

0 x n bn

M M M

0 xi +1 bi +1

0 xi bi

*

=

0 xi −1 bi −1

M M M

0 x 2 b2

1 x1 b1

(2.1.2-1)

14

15

Donde se denotó, sin pérdida de generalidad, los bits de datos de entrada de las

compuertas lógicas ópticas como la variable real11 ‘ xi ’. Así mismo, se denotó como bi , la

constante que determina el valor de ‘ xi ’.

Los valores de cada una de estas variables, se varían según las características de

diseño, y estas se pueden definir según sea la función lógica de la compuerta óptica.

La matriz cuadrada (2.1.2-1) es la matriz identidad. Y su Rango(A) = n, ya que el

rango es igual al número de ecuaciones linealmente independientes del sistema de

ecuaciones lineales.

Además, es de ‘n’ variables independientes, por lo que a cada matriz se le debió

proporcionar ‘n’ ecuaciones linealmente independientes y consistentes para encontrar la

solución particular que se usó en la construcción de cada compuerta lógica.

11

El valor de la variable puede tomarse como la amplitud del campo eléctrico de la onda electromagnética,

siempre que luego se haga la conversión a irradiancia cuando calcule la potencia que recibirá el fotodiodo..

15

16

2.1.3

El ‘OR’ optoelectrónico.

Para obtener la función lógica booleana ‘OR’, se consideró el circuito detector de la

figura 2.6.

D119

+

V+

8

U5A

3

V1

2

R3

5Vdc

-

5Vdc

LF353/NS

Salida

4

4k

1

V-

OUT

V3

V4

Vdc

Vdc

0

Figura 2.6 Circuito detector para el “OR” optoelectrónico. La flecha negra indica el

fotodiodo.

Tabla 2.2. Tabla de verdad del circuito de la Figura 2.6.

Entrada del fotodiodo

Salida

0

0

1

1

A continuación se describe el algoritmo que se consideró para diseñar un ‘OR’

óptico de n-entradas. Considere la siguiente función lógica12 S= (x n + K + xl' + K + x1 ) :

a) El dato de entrada xm =0 en ‘S’=0, si el bit ‘m’ NO está NEGADO en

‘S’=0, y el diagrama del circuito fue el de la Figura 2.7

12

Ver Apéndice B.1 para una demostración matemática de este algoritmo.

16

17

b) El dato de entrada xl' =1 en ‘S’ ≠ 0 , si el bit ‘l’ está en NEGADO en

‘S’=0, y el diagrama del circuito fue el de la Figura 2.8.

Interferómetro

Mach-Zehnder

Dato de

entrada

(a)

Dato de

entrada

LED

(b)

Figura 2.7. Diagrama de bloques del circuito que NO INVIERTE la entrada. (a) Con

láser. (b) Con LED.

Dato de

entrada

Inversor

electrónico

Interferómetro

Mach-Zehnder

(a)

Dato de

entrada

Inversor

electrónico

LED

(b)

Figura 2.8. Diagrama de bloques del circuito que INVIERTE la entrada. . (a) Con

láser. (b) Con LED.

17

18

2.1.3.1 Ejemplo de un ‘OR’ optoelectrónico de 3 entradas

En el siguiente ejemplo se verificó el resultado del algoritmo anterior mediante la

tabla de verdad resultante de este planteamiento para un caso específico.

Tabla 2.3 Ejemplo para S= x3' + x2' + x1

x3

x2

x1

Interferencia

S=Salida de

constructiva

Compuerta

OR= x3' + x2' + x1

0

0

0

2

1

0

0

1

3

1

0

1

0

1

1

0

1

1

2

1

1

0

0

1

1

1

0

1

2

1

1

1

0

0

0

1

1

1

1

1

18

19

2.1.4

El ‘NAND’ optoelectrónico

Para el circuito detector del ‘NAND’ optoelectrónico se consideró un circuito como

el de la figura 2.9.

D119

+

V+

8

U5A

3

V1

2

R3

5Vdc

-

5Vdc

LF353/NS

Salida

4

4k

1

V-

OUT

V3

V4

Vdc

Vdc

0

Figura 2.9. Circuito detector del ‘NAND’ optoelectrónico. Las flechas negras indican

el fotodiodo.

Tabla 2.4. Tabla de verdad del circuito de la figura 2.9.

Entrada de fotodiodo

Salida

0

0

1

1

A continuación se describió el algoritmo que se consideró para diseñar un ‘NAND’

óptico de n-entradas, para la función lógica13 S= (x n K xl' K x1 ) ’:

a)

El dato de entrada xm =1 en ‘S’ ≠ 0 .

Si el bit ‘m’ NO está

NEGADO en ‘S’=0, y el diagrama del circuito fue el de la Figura

2.10.

13

Ver Apéndice B.2 para una demostración matemática de este algoritmo

19

20

b)

El dato de entrada xl' =0 en ‘S’=0. Si el bit ‘l’ esta NEGADO en

‘S’=0, y el diagrama del circuito fue el de la Figura 2.11.

Dato de

entrada

Interferómetro

Mach-Zehnder

Inversor

electrónico

(a)

Dato de

entrada

Inversor

electrónico

LED

(b)

Figura 2.10. Diagrama de bloques del circuito que INVIERTE la entrada para el bit

‘m’ NO NEGADO en ‘S’=0, (a) con láser, (b) con LED.

Dato de

entrada

Interferómetro

Mach-Zehnder

(a)

Dato de

entrada

LED

(b)

Figura 2.11. Diagrama de bloques del circuito que NO INVIERTE la entrada para el

bit ‘l’ NEGADO en ‘S’=0, (a) con láser, (b) con LED.

20

21

2.1.4.1 Ejemplo de tabla de verdad para un NAND de 3 entradas optoelectrónico

En el siguiente ejemplo se mostró la tabla de verdad resultante de este

planteamiento.

Tabla 2.5 Ejemplo para ( x3' x2' x1 )’.

x3

x2

x1

Salida de

S=Salida de

interferencia

compuerta

constructiva

“NAND”=

( x3' x2' x1 )’

0

0

0

1

1

0

0

1

0

0

0

1

0

2

1

0

1

1

1

1

1

0

0

2

1

1

0

1

1

1

1

1

0

3

1

1

1

1

2

1

21

22

2.1.5

Compuertas ‘NOR’ y ‘AND’ optoelectrónicas

Estas compuertas se pueden construir con el circuito detector de la figura 2.12. Este

consiste en un circuito detector idéntico al de las compuertas ‘OR’ y ’NAND’ unido en la

salida a un inversor electrónico CMOS. Las reglas para las entradas de la compuerta ‘OR’

son las mismas que para las de la compuerta ‘NOR’, y las de la entrada de la compuerta

‘AND’ son las mismas que para la compuerta ‘NAND’.

R1

D119

8

U5A

+

1k

V+

3

M2

OUT

1

V1

5Vdc

MbreakP

LF353/NS

M1

4

4k

5Vdc

-

V-

2

R3

V5

5Vdc

V3

V4

Vdc

MbreakN

Salida

Vdc

0

Figura 2.12. Circuito detector del fotodiodo para las compuertas ‘NOR’ y ‘AND’.

22

23

2.2

Compuertas lógicas optoelectrónicas con interferencia coherente

Como se demostró en el apéndice A.1 y A.3, la interferencia de ondas

electromagnéticas coherentes da como resultado una irradiancia tal que se cumple la

ecuación (2.2-1).

I total

n

= ∑ I j

j =1

2

(2.2-1)

Donde ‘Ij’ es cada una de las Irradiancias de las entradas.

Para diseñar las compuertas lógicas optoelectrónicas con interferencia no-coherente,

se puede seguir las mismas reglas de las compuertas de interferencia no-coherente, con la

salvedad de que la suma de cada entrada será según la ecuación (2.2-1), que crece mucho

más que para el caso de suma de ondas no-coherentes (correspondiente a la ecuación (2.22)). Lo anterior hace que la resistencia de carga tenga que ser mayor para abarcar la misma

cantidad de bits de entrada en cada compuerta, que, según se verá en la sección 2.3 implica

una menor velocidad de procesamiento real de datos.

n

I total = ∑ I j

(2.2-2)

j =1

23

24

2.3

Análisis teórico de la velocidad de conmutación y procesamiento de

datos

El diseño general que se pensó para las compuertas lógicas ópticas consiste en

utilizar un circuito detector con un fotodiodo, una resistencia, y varios amplificadores

operacionales, como en la figura 2.1. En general se trata de utilizar el mismo principio de

un convertidor analógico-digital, adaptándolo para decodificar, en uno o dos ciclos, una

señal óptica binaria.

La fortaleza de este arreglo consiste en que es capaz de procesar en pocos ciclos una

señal binaria de dos o más bits, aprovechando el mayor ancho de banda que presentan

algunos detectores comparado a los circuitos electrónicos 14 , y fue por esta razón que

inicialmente se pensó en realizar esta investigación. Sin embargo, según fue avanzando la

investigación, al calcular la velocidad de conmutación entre un nivel de tensión y otro, y en

particular su demanda sobre el llamado efecto ‘RC’ aún para el mejor de los casos, se llegó

a la conclusión de que esta velocidad o frecuencia lograda para procesar más de dos bits fue

muy baja, y aunque esto se puede corregir con fotodiodos extremadamente veloces, me

pareció que era más práctico simplemente seguir realizando de manera tradicional con las

compuertas electrónicas.

En efecto, para todas las compuertas electrónicas es necesario considerar la

siguiente ecuación (2.3-1) de ancho de banda a -3dB. En particular hubo que reconsiderar

14

Ver referencia 7

24

25

la magnitud de los dB para cada una de las compuertas optoelectrónicas como veremos a

continuación.

f −3dB =

1

2 * π * RL * C

(2.3-1)

Donde C es la capacitancia del fotodiodo, y RL es la resistencia de carga del

circuito del fotodiodo.

La resistencia de carga varió su valor un según la sensibilidad que se le quiera dar al

circuito y también, asociado a esta, la magnitud de los dB’s que se utilizó para obtener la

ecuación (2.3-1). Como ya se mencionó, la fórmula (2.3-1) (que varía un poco en el caso

de las compuertas optoelectrónicas, como se verá más adelante) fue el talón de Aquiles de

este trabajo, es decir su punto más débil. Si bien, por un lado se pudo tomar un RL más

grande para tener un sistema más sensible, que abarcara un mayor número de bits, un

mayor número de palabras lógicas en una sola compuerta, y que lo procesara todo en un

solo ciclo, el incremento en esta resistencia RL le restó velocidad a cada ciclo para un

fotodiodo dado con una capacitancia dada. Además, conforme aumentó el número de bits a

procesar, más preciso debía de ser la señal por lo que los dB’s aumentaron (menos

negativos) de manera estrepitosa, disminuyendo así también la frecuencia de corte.

Es por esto que la única manera que se encontró para contrarrestar esta disminución

en la frecuencia de conmutación, fue sugiriendo la utilización de fotodiodos con una

capacitancia cada vez menor conforme se incrementaba la sensibilidad, para así mantener la

25

26

misma frecuencia. Si bien es cierto que en revistas científicas15 recientes se mencionan

fotodiodos semiconductores que sobrepasan las capacidades de los chips aún más

(

avanzados con una detectividad específica de hasta 1x1013 Jones cm * Hz

1/ 2

W

)

a

temperatura ambiente y a una longitud de onda óptica de 1,3 µm; aún así es difícil saber lo

que sucederá a futuro, y como ya dijimos antes, y demostraremos a continuación, para

características similares de los componentes, las compuertas electrónicas sobrepasan en

velocidad a las optoelectrónicas. Sin embargo, si los componentes optoelectrónicos a la

larga llegasen a superar a los electrónicos, esta propuesta podría tener importancia Pero

veamos un pequeño ejemplo.

P

− 3dB = 10 * log 0

Pin

P

⇒ 0.5 = 0

Pin

(2.3-2)

Entonces, si por ejemplo, se quiere implementar una compuerta con n1 =8 entradas,

se necesita los siguientes dB’s.

7 .5

− 0,28dB = 10 * log

8

(2.3-3)

Por lo que en este caso, para n1 =8, los dB’s, en lugar de ser -3dB, fueron -0.28dB.

Se sabe que el circuito equivalente de un fotodiodo es el de la figura 2.13(b).

15

Ver referencia 12

26

27

R

1

V1 = 0 V

V2 = u(t) V

2

2

2

I1 = 0 A

I2 = u(t)/R A

V

C

TD =

TR =

TF =

PW =

PER =

1

=

(a)

2

I1

R

TD =

TR =

TF =

PW =

PER =

C

1

1

(b)

Figura 2.13. Circuitos equivalentes entre sí. (b) Circuito equivalente del fotodiodo.

Entonces, se hizo el análisis en el tiempo del circuito equivalente del fotodiodo de la

figura 2.13(b). En efecto, aplicando mallas en la figura 2.13 (b).

u (t ) V

∂V

= +C

R

R

∂t

(2.3-4)

Donde V, es el voltaje en el capacitor. Aplicando la Transformada de Laplace.

u ( s) V ( s)

V ( s)

1

=

+ CsV ( s ) ⇒

= H ( s) =

R

R

u( s)

RCs + 1

(2.3-5)

Luego, como la forma de una onda electromagnética que se extingue es semejante a

una señal coseno, y la función de transferencia de la ecuación (2.3-5), se puede, volviendo

al ejemplo cuando n1 =8 entradas, en la ecuación (2.3-6), tenemos que.

20 * log 1 − 20 * log 1 + R 2 C 2 w 2 = −0,28

⇒ 0,0328 = R 2 C 2 w 2

w

= 7,2 MHz

2 *π

V n

con R = máx 1 = 4kΩ; C = 1 pF .;Vmáx = 5V ;

I máx

⇒ f −0.28 =

(2.3-6)

n1 = 8; I máx = 10mA

27

28

Al seguirse el mismo algoritmo que para el ejemplo anterior se pudo deducir una

forma general para la frecuencia que tendrá este arreglo óptico en función de las constantes

siguientes:

•

La tensión de polarización a la que se encuentra el fotodiodo.

•

La corriente máxima del fotodiodo.

•

La capacitancia del fotodiodo a esa tensión.

Y de la variable:

•

n1 = el número de bits que incluye la compuerta, esto se logra variando la

resistencia de carga para variar así la sensibilidad del circuito detector.

Entonces, para un ‘ n1 ’ variable, y unos ‘Vmáx’, ‘Imáx’, y ‘C’, como en el ejemplo

anterior, tenemos el siguiente desarrollo matemático general.

n − 0.5

x = 10 log 1

n1

(2.3-7)

Nótese que la ecuación (2.3-7) sirve para las compuertas optoelectrónicas basadas

en interferencia no-coherente y además note que la desigualdad (2.3-8), cuyo término de la

izquierda sirve para el caso de compuertas optoelectrónicas con interferencia coherente,

también se cumple.

n12 − 0.5

n1 − 0.5

10 log

>

10

log

2

n

n

1

1

1

1

10 log1 − 2 > 10 log1 −

2n1

2n1

(2.3-8)

28

29

Luego, de la función de transferencia de la ecuación (2.3-5), y los dB’s de la

ecuación (2.3-7), tenemos el siguiente desarrollo matemático.

n − 0.5

20 log1 − 20 log 1 + R 2 C 2 w 2 = dB' s = 10 log 1

n

1

n − 0.5

log 1 + R 2 C 2 w 2 = −0.5 log 1

n1

2

2

2

1 + R C w = 10

w=

f1 =

10

n − 0.5

− 0.5 log 1

n1

n − 0.5

− 0.5 log 1

n1

(2.3-9)

−1

RC

10

n − 0.5

− 0.5 log 1

n1

−1

2πRC

Donde se debió usar la fórmula de la ecuación (2.3-10) para la resistencia de carga.

R=

Vmáx

V n

= máx 1

I máx

I máx

n1

(2.3-10)

De donde, al sustituirse en el resultado anterior se obtuvo la ecuación (2.3-11) que

es la frecuencia a la que se ejecuta cada ciclo para las compuertas optoelectrónicas con

interferencia no-coherente.

n − 0.5

− 0.5 log 1

n1

f1 =

I máx 10

2πVmáx n1C

−1

(2.3-11)

Por otro lado, para compuertas con interferencia coherente, se utiliza el primer

término de las desigualdades (2.3-8), y se consideró que para un número de bits ‘ n1 ’ que

29

30

abarque la compuerta, el rango de voltajes abarca un nivel máximo igual a ‘ n12 ’, de ahí que

dio como resultado la expresión (2.3-12), que considera la velocidad real de cada ciclo,

obteniéndose así la frecuencia que llamamos frecuencia equivalente.

La frecuencia

equivalente no es más que, la frecuencia de principio a fin de cada compuerta,

considerando a la compuerta como una caja negra.

1

− 0.5 log 1− 2

2n

1

f3 =

I máx 10

2πVmáx n12 C

−1

(2.3-12)

Por otro lado para los circuitos electrónicos cuando se desean procesar n1 bits, se

requieren de los n2 ciclos de la ecuación (2.3-13). Y el número máximo de mintérminos

n

para n par 16 , o de

para una sola compuerta optoelectrónica de ‘n’ entradas es

n

/

2

n

n

o lo que es lo mismo de

para ‘n’ impar17, que se ejecutan en n3

(n − 1) / 2

(n + 1) / 2

ciclos según también la ecuación (2.3-13).

16

17

Ver Apéndice C.1 para una demostración

Ver Apéndice C.1 para una demostración

30

31

log(n1 )

2 n2 = n1 ⇒

= n2

log(2)

2 n3

2

n3

n1!

log

2

((n1 / 2)!)

n1

n1!

=

=

⇒

= n3

2

log(2)

n1 / 2 ((n1 / 2)!)

n1

n1!

=

=

⇒

(

n

−

1

)

/

2

((

n

−

1

)

/

2

)!*((

n

+

1

)

/

2

)!

1

1

1

n1!

log

((n1 − 1) / 2)!*((n1 + 1) / 2)! = n

3

log(2)

con n1 par

(2.3-13)

con n1 impar

Donde en el caso del primer término (interferencia coherente) se considera la

posibilidad de conmutar desde un nivel alto máximo hasta la mitad entre el cero, o

viceversa, este resultado se utiliza más adelante.

Entonces, tomando como referencia los siguientes datos de fábrica para un

fotodiodo dado, podemos calcular la frecuencia equivalente para un circuito electrónico

dado, que toma n2 + n3 ciclos para ejecutarse, ejecutándose este circuito electrónico a una

frecuencia de Fmín:

•

C = 1pF.

•

R = 50 Ohms.

•

Vmáx = 5V.

•

Imáx = 10mA.

•

Fmín = 2 GHz.

De donde, la frecuencia equivalente del circuito electrónico si este lo decodificara

en un solo ciclo es la ecuación (2.3-14) (tomando en cuenta las ecuaciones (2.3-13))

31

32

2 *10 9

f2 =

=

n 2 + n3

2 *10 9

n1!

log

((n1 / 2)!) 2

log(n1 )

+

log(2)

log(2)

log(2)

f 2 = 2 *10 9 *

n1!

log(n1 ) + log

2

((n1 / 2)!)

para n1 par , ó

f 2 = 2 *10 9 *

=

(2.3-14)

log(2)

n1!

log(n1 ) + log

((n1 − 1) / 2)!*((n1 + 1) / 2)!

para n1 impar

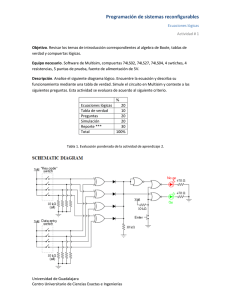

Las ecuaciones (2.3-11), (2.3-12) y (2.3-14) se grafican en la figura 2.14.

En la figura 2.14 se observa cómo las funciones f 1 , f 2 , y f 3 , son todas decrecientes,

sin embargo, para un mismo número de entradas, las compuertas electrónicas de dos

entradas tradicionales tienen siempre una velocidad real mayor, bajo condiciones similares,

que las compuertas optoelectrónicas que se propusieron en las secciones 2.1 y 2.2, aún

cuando estas compuertas ópticas procesen la información en un solo ciclo. Sin embargo, es

apropiado recordar, que se ha dado el caso en que los fotodetectores superan en velocidad a

la electrónica 18 , y es por ahí donde, en dado caso de que los detectores superen

grandemente a la electrónica, este trabajo puede llegar a ser importante, si se combinara

con la electrónica para casos de decodificación más sencillos.

18

Ver referencia 7

32

33

Figura 2.14. Gráfico de las funciones f 1 , f 2 , y f 3 (ecuaciones (2.3-11), (2.3-14) y (2.312) respectivamente), para el ejemplo con Imax = 10mA, C = 1pF, Vcc = 5V, y n1 de 2

a 171 bits. Aquí se utiliza la función gamma19.

19

Recuérdese que la función gamma tiene como rango los números complejos e incluye a la función factorial.

Ver Anexo 1.1 para ver el código fuente de este gráfico.

33

34

Tabla 2.6. Algunos resultados tabulados de las funciones f 1 , f 2 , y f 3 (ecuaciones (2.311), (2.3-14), y (2.3-12) respectivamente). Note que las frecuencias son las frecuencias

equivalentes para la compuerta de principio a fin y se consideró el peor caso para la

compuerta electrónica. Para estos datos se tomaron los valores Imax = 10mA, C =

1pF, Vcc = 5V, y n1 de 2 a 128 bits de entrada.

n1

f1 (optoelect. No-

f 2 (electrónica)

coherente)

f 3 (optoelec.

Coherente)

2

62,6MHz

2GHz

20,91MHz

4

20,91MHz

400MHz

2,52MHz

8

7,2MHz

166,67MHz

311,76kHz

16

2,52MHz

100MHz

38,89kHz

32

884,42kHz

52,64MHz

4,86kHz

64

311,76kHz

27,78MHz

608Hz

128

110kHz

14,5MHz

76Hz

Finalmente, se observa en la figura 2.14 que, para todo 2 ≤ n1 ≤ 171 , la función

f 2 .es mayor que las funciones f 1 y f 3 .

Entonces bastó con demostrar que, para

todo n1 ≥ 2 , que las siguientes desigualdades de la ecuación (2.3-15) se cumplen20.

f 3 < f1 < f 2

20

(2.3-15)

Ver Apéndice C.2 para la demostración.

34

35

2.4

Fototransistores21

Los fototransistores son dispositivos donde el flujo de corriente de una unión p-n

del detector es internamente amplificada.

Su construcción es básicamente la de un

transistor de unión, con la región base expuesta a la radiación incidente. Normalmente no

tiene conexión externa a la base. Para entender la operación del dispositivo, la corriente de

base es suplida por la corriente foto-generada.

La corriente de colector tiene dos

componentes: (a) la corriente normal reversa de saturación del diodo, y (b) la parte de la

corriente del emisor que logra pasar al colector. Ésta última corriente se escribió como αie ,

donde α es ligeramente menor a 1 (α es conocida como la ‘corriente común de ganancia de

base).

ico + αie = ie − ib

(2.4-1)

De donde,

ic =

ib + ico

α

= (ib + ico )

+ 1 = (ib + ico ) * (h fe + 1)

1−α

1−α

(2.4-2)

Donde h fe = α /(1 − α ) es conocida como ‘corriente de ganancia de colector común’

del transistor.

Valores típicos para h fe en fototransistores son cercanos a 100.

Sin

radiación incidente ib =0 y la corriente que fluye ico (h fe + 1) , es la corriente de oscuridad

del dispositivo.

Ésta es obviamente más grande que para dispositivos de unión p-n

comparables donde la corriente de oscuridad en esta notación es sólo ico .

21

Tomado de la referencia 1

35

36

Cuando sea iluminada habrá una corriente de base de magnitud iλ , donde

I Aeλ0

, y donde ‘η’ es la fracción de la radiación incidente que es absorbida en

iλ = η 0

hc

la región activa, ‘Io’ es la Irradiancia incidente, ‘A’ es el área, ‘e’ es la carga del electrón,

‘ λ0 ’ es la longitud de onda de la radiación incidente, ‘h’ es la constante de Planck, y ‘c’ es

la velocidad de la luz en el vacío.

(iλ + ico ) * (1 + h fe ) donde, si iλ

El flujo externo de corriente externo es ahora

>> ico , es igual a iλ (1 + h fe ) . Por tanto el dispositivo da una

ganancia interna, y tiene una responsitividad entre un fotodiodo p-i-n y un fotodiodo de

avalancha.

Los fototransistores de silicio, como los utilizados en el experimento de la sección

3.1, están disponibles a bajo costo. Estos detectores usualmente sufren de un bajo ancho de

banda, normalmente limitada a unos cientos de kilohertz.

Esto se debe a la alta

capacitancia de la unión base-colector y a los altos tiempos de de tránsito de las cargas a

través de la región de la base. Por otro lado, su amplificación hace que simplifique los

circuitos donde el ancho de banda no importe.

Es posible hacer fototransistores con un ancho de banda mucho mayor.

Las

estructuras n-p-n para fototransistores basadas en heterouniones de InGaAsP/InP. Como en

los fotodiodos p-i-n de InGaAs/InP, la radiación incidente con una longitud de onda mayor

a 0,92 µm pasa sin atenuarse a través de la capa superior de InP y longitudes de onda hasta

la longitud de onda del hueco entre bandas del material base es absorbido en la base.

36

37

Figura 2.15. Conexiones externas hechas a un fototransistor n-p-n. (a) Radiación

absorbida en la región de la base causa que se fluya una corriente del emisor a través

de la resistencia de carga RL y por tanto aparecerá un voltaje de señal en ella. (b) Las

corrientes que se asumen fluyen en el fototransistor22.

22

Tomado de la referencia 1

37

38

Figura 2.16.Estructura n-p-n del fototransistor basado en una heterounión

InGaAsP/InP23.

23

Ver referencia 1

38

39

2.5

Fotorresistencias24

Las fotorresistencias de Sulfuro de Cadmio (CdS) son utilizadas por su bajo costo,

como sensores de radiación visible, por ejemplo en medidores de luz para cámaras. Estos

dispositivos usualmente tiene ganancia fotoconductiva alta (de 1000 a 10 000) pero tiempos

de respuesta pobres (cerca de 50 ms). El tiempo de respuesta depende mucho del nivel de

iluminación, viéndose reducido a niveles altos, lo que refleja la presencia de trampas. Una

capa de polycristalino es depositada en un substrato aislante y los electrodos se forman

evaporando un metal adecuado, como por ejemplo oro, a través de una máscara para darle

la forma de peine.

Esta geometría, que resulta en un área relativamente grande de

superficie sensitiva y un espaciamiento relativamente pequeño entre electrodos, ayuda a

darle una mayor sensitividad al dispositivo.

24

Ver referencia 1

39

40

CAPÍTULO 3: Informes

En este capítulo se presentan dos informes, el de la sección 3.1 trata sobre la

construcción de una dos compuertas AND, la primera fue construida con fotorresistencias y

IRLED’s, entre otros componentes que se explican en la sección 3.1; y la segunda

compuerta AND fue construida con fototransistores en lugar de las fotorresistencias.

Ambas contaron con un LED verde que se encendía cuando la salida estuvo en nivel alto

como corresponde.

Este experimento no estaba dentro de los objetivos iniciales del

proyecto, pero se decidió incluirlo para ejemplificar el tema y como demostración para el

LAFTLA.

En la sección 3.2 se incluyó un informe del diseño de compuertas optoelectrónicas

utilizando interferencia constructiva de ondas no-coherentes.

Asimismo, en la sección 3.3 se incluyó un informe del diseño de compuertas

optoelectrónicas utilizando interferencia constructiva de ondas no-coherentes.

3.1

Informe

de

la

construcción

de

dos

compuertas

AND

optoelectrónicas

Como objetivo extra, se quiso construir dos pequeñas compuertas optoelectrónicas

basadas en diseños encontrados en un folleto de Radio Shack sobre este tema25. Estas

compuertas se construyeron con el objetivo de demostrar el principio de funcionamiento de

una compuerta optoelectrónica AND en general, mediante un pequeño experimento

práctico.

40

41

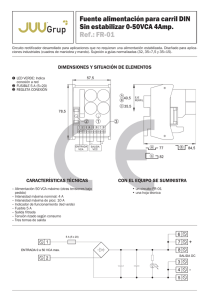

Los datos de los emisores IRLED’s están en el Anexo 3.

Para la primera compuerta optoelectrónica AND de la figura 3.2, se utilizaron dos

IRLED’s (que quiere decir ‘diodo emisor de luz infrarroja’ por sus siglas en inglés), una

resistencia de 220 Ohms, alimentados por una fuente a 5V; y como detectores se utilizaron

dos fotorresistencias (Parte # 276-1657 de Radio Shack), una resistencia corriente de 47

Ohms, alimentados por una fuente de 5V. La tabla 3.1 muestra la tabla de verdad para el

circuito de la figura 3.2.

El análisis del circuito emisor de la figura 3.1 es el siguiente:

RS =

Vin − VLED 6 − 1,7

=

= 215Ω ≈ 220Ω

I LED

0.02

(3.1-1)

De ahí el valor de la resistencia del circuito emisor de la figura 3.2, y la Figura 3.3.

R4

220 D3

V2

6Vdc

R1

6Vdc

V5 220

D2

Figura 3.1. Circuito emisor con IRLED’s26 para los arreglos de la figura 3.2 y la

Figura 3.3.

25

26

Ver referencia 7

Ver datos del fabricante para estos IRLED’s en Anexo 3

41

42

Las fotos de ambos circuitos, en los distintos valores de la tabla 3.1, están en el

Anexo 2.

R4

R3

220 D3

R2

47

V2

V1

6Vdc

5Vdc

R1

6Vdc

V5 220

D2

R2

D1

Figura 3.2. Circuito emisor IRLED (izquierda), y circuito detector con

fotorresistencias27 y LED (LED genérico visible como indicador de salida).

Tabla 3.1. Tabla de verdad de la compuerta AND con fotorresistencias del circuito de

la figura 3.2, y la Figura 3.3.

D3 (IRLED)

D2 (IRLED)

D1 (LED visible indicador)

0

0

0

0

1

0

1

0

0

1

1

1

El circuito de la figura 3.2 fue armado en el ‘LAFTLA’ (Laboratorio de Fotónica y

Tecnología Láser Aplicada) y fue fotografiado en cada uno de los estados de la tabla 3.1, en

las figuras siguientes.

42

43

Por otro lado, el arreglo optoelectrónico de la Figura 3.3 con fototransistores en

lugar en fotorresistencias, cumple la tabla de verdad de la tabla 3.1. Además utiliza el

circuito emisor de la figura 3.1, cuya resistencia fue calculada mediante la ecuación (3.1-1).

R4

R6

Q1

220 D3

220

V2

6Vdc

R1

6Vdc

V5 220

D2

Q2

V4

5Vdc

D6

Figura 3.3. Circuito emisor IRLED (izquierda), y circuito detector con

fototransistores28 y LED (LED verde como indicador de salida).

Los datos de uno de los fototransistores está en el Anexo 3.

El segundo

fototransistor es un fototransistor NPN Infrarrojo de Silicio con número de parte #276-145

de Radio Shack. A continuación se presentan las fotos del arreglo optoelectrónico en los

diferentes estados.

Las fotos de ambos circuitos, en los distintos valores de la tabla 3.1, están en el

Anexo 2.

27

28

Ver datos del fabricante para estas fotorresistencias en Anexo 3

Ver datos del fabricante para estos fototransistores en Anexo 3

43

44

3.2

Informe del diseño de compuertas optoelectrónicas utilizando

interferencia constructiva de ondas no-coherentes.

En la sección 2.1 se expuso la teoría para diseñar compuertas optoelectrónicas con

interferencia constructiva de ondas no-coherentes con dos o más entradas que se pueden

procesar en muchos menos ciclos que las compuertas electrónicas. Para tal efecto se ideó

una especie de convertidor A/D que convirtiera la Irradiancia de las ondas a señales

digitales. Como parte del diseño de demostró que las compuertas pueden ser variables, y su

salida puede ser equivalente a varios mintérminos unidos en la salida de una gran función

lógica, lo que en un principio (antes de iniciar la investigación con más detalle), hacía

pensar que al incluir un número bastante alto de mintérminos se podría compensar el

llamado efecto ‘RC’, que normalmente hace lentos a los convertidores A/D.

En la sección 2.3 se demostró que las compuertas electrónicas tradicionales de dos

entradas y una salida son más rápidas que ambos tipos de compuertas optoelectrónicas

expuestas en este proyecto, esto en términos del tiempo que tarda el sistema en procesar la

información de principio a fin, y para condiciones similares de velocidad de conmutación

de las compuertas electrónicas y del fotodiodo de las compuertas optoelectrónicas de la

sección 2.1, y la sección 2.2.

Sin embargo, lo único que podría hacer este tipo de compuerta optoelectrónica

factible, es que como existen limitaciones teóricas y prácticas para la velocidad máxima de

conmutación de los componentes electrónicos en silicio, y como estos límites han visto

44

45

superados por una técnica de construcción de fotodetectores en investigaciones recientes29,

existe la posibilidad, aunque remota, que aún en el límite máximo de las limitaciones de

estas tecnologías la técnica expuesta en la sección 2.1 pudiese llegar a encontrar una

aplicación, aunque reducida, en el futuro.

29

Ver referencia 12

45

46

3.3

Informe del diseño de compuertas optoelectrónicas utilizando

interferencia constructiva de ondas no-coherentes.

En la sección 2.2 se expuso la teoría para diseñar compuertas optoelectrónicas con

interferencia constructiva de ondas coherentes con dos o más entradas que se pueden

procesar en muchos menos ciclos que las compuertas electrónicas. Además, en la sección

2.3 se demostró que las compuertas electrónicas tradicionales de dos entradas y una salida

son más rápidas que ambos tipos de compuertas optoelectrónicas expuestas en este

proyecto, esto en términos del tiempo que tarda el sistema en procesar la información de

principio a fin, y para condiciones similares de velocidad de conmutación de las

compuertas electrónicas y del fotodiodo de las compuertas optoelectrónicas de la sección

2.1, y la sección 2.2.

Por otro lado, a diferencia de las compuertas expuestas en la sección 2.1, las

compuertas de la sección 2.2, como son más lentas que las de la sección 2.1, no se logró

encontrar aplicación alguna como compuerta optoelectrónica.

46

CAPÍTULO 4: Conclusiones y recomendaciones

•

La fortaleza de las compuertas optoelectrónicas de la sección 2.1 consiste

en que es capaz de procesar en pocos ciclos una señal binaria de dos o

más bits, aprovechando el mayor ancho de banda que presentan algunos

detectores comparado a los circuitos electrónicos30, y fue por esta razón

que inicialmente se pensó en realizar esta investigación.

•

Sin embargo, según fue avanzando la investigación, al calcular la

velocidad de conmutación entre un nivel de máximo y el mínimo, y en

particular su demanda sobre el llamado efecto ‘RC’, aún para el mejor de

los casos, se llegó a la conclusión de que esta velocidad o frecuencia

lograda para procesar más de dos bits fue muy baja considerando los

fotodiodos que existen en este momento.

•

Aunque esto se puede corregir con fotodiodos extremadamente veloces,

me pareció que era más práctico simplemente seguir realizando de

manera tradicional con las compuertas electrónicas.

•

En el dado caso que se desarrollen en el futuro fotodetectores muchísimo

más veloces que la electrónica, sería posible concebir una aplicación

híbrida de estos diseños, en los que para funciones de pocos bits se

utilice la electrónica, pero para funciones más complejas se utilicen

30

Ver referencia 7

47

48

tecnología optoelectrónica como la expuesta en la sección 2.1, siempre

que los detectores superen la velocidad de conmutación en al menos dos

órdenes de magnitud a la electrónica, tomando en cuenta que hasta el

momento algunos estudios sugieren que estos pueden superarla en un

orden de magnitud31.

•

Entre las consideraciones a tomar en cuenta para la implementación de

compuertas optoelectrónicas con fotodiodos están:

o Capacitancia del fotodiodo.

Esta es muy necesaria para

determinar la velocidad máxima de conmutación de un estado a

otro. Entre más pequeña sea, más veloz será la compuerta.

o La resistencia de carga. Esta varía según el número de estados a

decodificar y por ende según la sensibilidad del circuito

optoelectrónico detector. Para un número muy grande de bits de

entrada su valor crece grandemente.

o Si el número de valores o estados a decodificar es muy grande,

debe considerarse dividir la señal óptica en varias partes y

decodificar varios valores por separado. Con esto se evita que se

consuma la preciosa corriente generada por el fotodiodo en las

entradas de los amplificadores operacionales, lo que afecta la

señal eléctrica detectada.

31

Ver referencia 12

48

49

•

El ruido es algo que siempre está presente en los circuitos electrónicos y

optoelectrónicos, y por ende debe ser considerado.

•

Con respecto a las compuertas optoelectrónicas con fototransistores,

estas funcionan bien, pero los basados en silicio son muy lentos, y falta

investigación en para aumentar la velocidad de conmutación de estos

dispositivos.

•

Una de las tecnologías que más promete para la optoelectrónica, y la

electrónica en general, es la nanotecnología.

Entre las ventajas que

ofrece esta tecnología están:

o Mayor desempeño a bajo costo.

o Tamaño muy reducido aún para los estándares actuales de la

electrónica.

•

Entre las desventajas de la nanotecnología están:

o Falta más investigación para su completo desarrollo.

o Falta desarrollar más y mejores técnicas de construcción de

dispositivos basadas en esta tecnología.

o Falta investigar si esta tecnología es amigable con el ambiente o

no, y ¿qué tanto?

•

Por encima de las soluciones presentadas en este trabajo y por encima

aún de la electrónica, se encuentran las soluciones totalmente ópticas (y

49

50

por supuesto las muy publicitadas computadoras cuánticas, que van

mucho más allá de este trabajo). Entre las desventajas de estas están:

o Su alto costo actual.

o Ven limitada su velocidad por canal de transmisión por la interfaz

electrónica, que en la mayoría de los casos es infranqueable.

•

Entre las ventajas de los sistemas totalmente ópticos están:

o Aislamiento al ruido de otras señales.

o Potencialmente más veloz que la electrónica.

o Resistencia a condiciones extremas.

50

BIBLIOGRAFÍA

Libros:

1. Wilson, J. & Hawkes, J. “Optoelectronics, an introduction”, 3era edición,

Prentice Hall, EE. UU., 1998.

2. Arce, C., Castillo, W., González, J. “Algebra Lineal”, 3era edición, Editorial de la

Universidad de Costa Rica, Costa Rica, 2005.

3. Ríbnikov, K., traducido del ruso por Medkov, K. “Análisis combinatorio”, 1ª

edición, Editorial Mir, URSS, 1985, traducido al español en 1988.

4. Hecht, E. “Theory and problems of optics”. 1ª edición, McGraw-Hill, USA,

1975.

5. “Encyclopaedia Británica 2008 Ultimate DVD”.

6. Palais, J., “Fiber Optic Communications”.

4ª edición, Prentice Hall, Inc.,

Englewood Cliffs, NJ, 1998.

7. Minus, F. M. III, “Engineer’s Mini-Notebook, Optoelectronics Circuits”. 1ª

edición, 5ª reimpresión, A Siliconcepts Book, USA, 1998. Cat. No. 62-5012

Artículos de revistas:

8. University of Illinois at Urbana-Champaign. "World's Fastest Transistor

Approaches Goal Of Terahertz Device." ScienceDaily 13 December 2006. 5

December 2007. http://www.sciencedaily.com /releases/2006/12/061212091344.htm

9. Alexander W. Fang, Hyundai Park, Oded Cohen, Richard Jones, Mario J. Paniccia,

y John E. Bowers.

“Electrically pumped hybrid AlGaInAs-silicon evanescent

51

52

laser”,

“Optics

Express”,

USA,

Vol

14,

Issue

20,

pp.

9203-9210

http://www.opticsexpress.org/abstract.cfm?id=114596

10. Brian R. Koch, Alexander W. Fang, Oded Cohen, y John E. Bowers. “Mode-locked

silicon evanescent lasers”, “Optics Express”, USA, Vol 15, Issue 18, pp. 1122511233, 2007. http://www.opticsexpress.org/abstract.cfm?id=140973

11. Suzuki, T., Ebata, T., Fukuda, K., Hirakata, N., Yoshida, K., Hayashi, S., Takada,

H., Sugawa, T.

“High-speed 1.3-µm LED transmitter using GaAs driver IC”,

“Lightwave Technology, Journal of”, USA, Vol 4, Issue 7, págs. 790-794, 2007.

http://ieeexplore.ieee.org/xpl/freeabs_all.jsp?tp=&arnumber=1074814&isnumber=2

3156

12. Hoogland, S., Konstantatos, G., Sargent, Edward H. “Paint-On optoelectronics”.

Revista “Optics and Photonics News”, Optical Society of America (OSA). Vol 17

No. 11 Noviembre 2006, http://www.osa-opn.org

Páginas web:

13. Intel

Corporation.

“Meet

the

world’s

first

45

nm

Processor”,

http://www.intel.com/technology/silicon/45nm_technology.htm

52

APÉNDICE A

A.1

Suma de ondas electromagnéticas coherentes32:

Imagínese que hay dos ondas planas linealmente polarizadas de la misma longitud

de onda dada por las ecuaciones (A.1-1) y (A.1-2) que se traslapan en un punto dado.

E1 (r , t ) = E 01 cos(k1 r − ωt + ε 1 )

(A.1-1)

E 2 (r , t ) = E02 cos(k 2 r − ωt + ε 2 )

(A.1-2)

Donde k1 , k 2 , ω , ε 1 y ε 2 son todas constantes.

Estas ondas pueden surgir, por

ejemplo, de una misma fuente que las separó mediante un beam splitter.

El campo

resultante esta dado por la ecuación (A.1-3).

E = E1 + E 2

(A.1-3)

Pero dado que a frecuencias ópticas los campos oscilan a más de 1014 Hz la

irradiancia se torna en una cantidad de interés práctico, siendo directamente medible.

Despreciando un factor constante, se puede escribir la irradiancia como el promedio en el

tiempo del campo total:

I = E2

(A.1-4)

Donde E 2 = E ⋅ E . Es decir,

E 2 = (E1 + E 2 ) ⋅ (E1 + E 2 ) = E12 + E 22 + 2 E1 ⋅ E 2

(A.1-5)

Tomando el promedio obtenemos la ecuación (A.1-6).

I = I 1 + I 2 + I 12

53

(A.1-7)

54

Donde I 1 = E12 , I 2 = E 22

y I 12 = 2 E1 ⋅ E 2

, siendo el último el término