PRÁCTICA 5: SUMADOR COMBINACIONAL DE 3 BITS CON

Anuncio

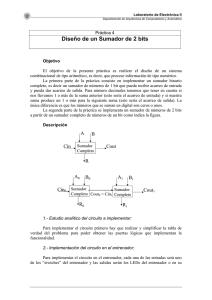

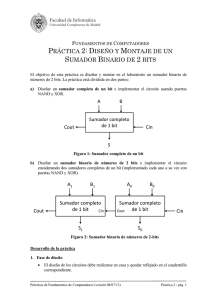

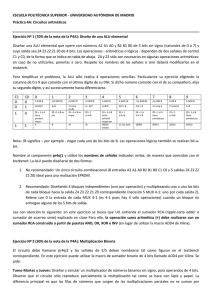

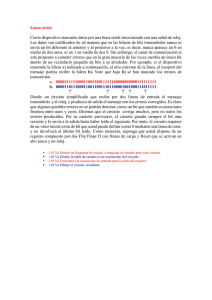

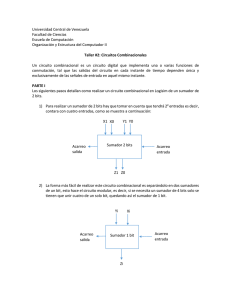

PRÁCTICA 5: SUMADOR COMBINACIONAL DE 3 BITS CON QUARTUS II OBJETIVOS El objetivo de esta práctica es el diseño e implantación de un sumador combinacional de 3 bits empleando tres sumadores de 1 bit con acarreo (ver Figura 1), formados únicamente con puertas lógicas. Al finalizar la práctica el alumno ha de ser capaz de: − Diseñar circuitos combinacionales, − Dividir un diseño complejo en bloques más pequeños, − Reutilizar componentes de otros diseños. MATERIAL − Ordenador personal con Quartus II, − Tarjeta de desarrollo de lógica programable DE1 de Altera. DURACIÓN 1 sesión. TRABAJO PREVIO Leer el enunciado de la práctica y realizar el diseño de un sumador combinacional de un bit. INTRODUCCIÓN Figura 1. Esquema del sumador de 3 bits. El circuito se diseñará mediante el programa Quartus II de Altera y se implementará en la tarjeta de desarrollo de lógica programable. 2 Práctica 5 Antes de comenzar a trabajar, crear el directorio de trabajo para la práctica de esta sesión. CARACTERÍSTICAS DEL CIRCUITO El circuito tiene siete entradas: − Tres bits correspondientes al primer número (A2, A1 y A0), − Tres bits correspondientes al segundo número (B2, B1 y B0), y − Un bit correspondiente al acarreo de entrada (C0). Y cuatro salidas: − Tres bits correspondientes a la suma (S2, S1 y S0), y − Un bit correspondiente al acarreo final (C3). Como entradas se utilizarán los interruptores de la tarjeta de desarrollo de lógica programable del laboratorio y como salida se utilizarán los LEDs. DESARROLLO PRÁCTICO DISEÑO Realice los siguientes pasos de diseño: − la tabla de verdad de un sumador de 1 bit, − la simplificación lógica, − el diseño de un circuito sumador de 1 bit utilizando solamente puertas lógicas, y − el diseño de un circuito sumador de 3 bits utilizando solamente sumadores de 1 bit. ¿Qué valor debe tener la entrada C0 del sumador de 3 bits, para que funcione correctamente? ESQUEMA Dibuje el esquema del sumador de 1 bit en una ventana de diseño de Quartus II y guárdelo con el nombre Sum1bit.bdf. A continuación, dibuje el esquema de la Figura 1, guárdelo con el nombre Sumador.bdf y declárelo como proyecto. Asigne las patillas de la FPGA indicadas en la Tabla 1 a las entradas y salidas del circuito. Consulte para ello el manual de usuario de la tarjeta de lógica programable (Altera DE1 Board).1 1 Disponible en la dirección http://www.iit.upcomillas.es/carlosrg/Docencia/LED/DE1_UserManual_v1018.pdf 3 Práctica 5 Señal Tipo Patilla FPGA Componente A2 Entrada SW[9] A1 Entrada SW[8] A0 Entrada SW[7] B2 Entrada SW[2] B1 Entrada SW[1] B0 Entrada SW[0] C3 Salida LEDG[3] S2 Salida LEDG[2] S1 Salida LEDG[1] S0 Salida LEDG[0] Tabla 1. Asignación de patillas de la FPGA a las señales del circuito. Compile el circuito para el dispositivo EP2C20F484C7 de la familia Cyclone II. Realice la simulación del circuito comprobando las operaciones. Muestre al profesor los resultados de la simulación. CONFIGURACIÓN Configure la FPGA y compruebe el correcto funcionamiento con la tarjeta del laboratorio realizando diferentes operaciones. Enseñe al profesor dicho funcionamiento. EJERCICIO OPCIONAL (I) En lugar de mostrar el resultado en cuatro LED de la tarjeta del laboratorio, utilizar el bloque Bina7Seg.bdf, realizado en las prácticas anteriores, para mostrar el resultado de la suma en un display de siete segmentos. Para realizar este ejercicio opcional es necesario copiar el archivo Bina7Seg.bdf a la carpeta de trabajo de la práctica de hoy, generar el símbolo e insertarlo en el esquema. Utilizar la asignación de componentes de la Tabla 2 para las nuevas señales de salida. Busque los números de patillas en el manual de usuario de la tarjeta. Señal Tipo Patilla FPGA Componente a Salida HEX0[0] b Salida HEX0[1] c Salida HEX0[2] d Salida HEX0[3] e Salida HEX0[4] f Salida HEX0[5] g Salida HEX0[6] Tabla 2. Asignación de patillas de la FPGA a las señales del display de siete segmentos. EJERCICIO OPCIONAL (II) A partir del sumador diseñado anteriormente, implantar un sumador / restador de números de tres bits. Mediante el interruptor SW5 se indicará la operación a realizar (suma/resta).