VIABILIDAD DE LA TARJETA BASYS2 PARA SU

Anuncio

INSTITUTO TECNOLÓGICO DE TEHUACÁN

Departamento de Ingeniería Eléctrica-Electrónica

Reporte de Residencia Profesional

Proyecto:

VIABILIDAD DE LA TARJETA BASYS2

PARA SU IMPLEMENTACIÓN EN EL

CONTROL DE UN PROCESO

Presenta:

Mario Merino Márquez

Asesor Interno:

Ing. Juan José Ortiz Flores

Asesor Externo:

Dr. Oscar Leopoldo Pérez Castañeda

Tehuacán, Puebla; a 24 Mayo de 2012

pág. 1

ÍNDICE

ÍNDICE .................................................................................................................... 2

INTRODUCCIÓN ................................................................................................... 4

JUSTIFICACIÓN .................................................................................................... 6

OBJETIVOS............................................................................................................ 8

OBJETIVO GENERAL .................................................................................... 8

OBJETIVOS ESPECÍFICOS ............................................................................. 8

ÁREA DE PARTICIPACIÓN ................................................................................. 9

PROBLEMAS A RESOLVER.............................................................................. 10

CRONOGRAMA DE ACTIVIDADES ................................................................. 10

Búsqueda y Compra de Tarjeta basada en FPGA XILINX Spartan 3E 100K ... 10

Instalación y Manejo del Software ISE Design Suite 13.4 y Digilent Adept ....... 10

Investigación de la Arquitectura de la Tarjeta basada en FPGA ....................... 10

Manejo del Lenguaje de Programación VHDL ................................................... 11

Desarrollo e Implementación de Prácticas de Circuitos Digitales básicos con

VHDL y la Tarjeta basada en FPGA ............................................................................... 11

Desarrollo e Implementación de Máquinas de Estados Finitos (FSM) .............. 11

Acondicionamiento de Entradas y Salidas de la Tarjeta basada en FPGA para

adquisición de datos y activación de actuadores............................................................ 12

Desarrollo e Implementación del Control de un Proceso por medio de la Tarjeta

basada en FPGA ............................................................................................................. 12

ALCANCES Y LIMITACIONES........................................................................... 13

ALCANCES ................................................................................................ 13

LIMITACIONES............................................................................................ 13

MARCO TEÓRICO .............................................................................................. 15

SISTEMAS DE CONTROL Y SISTEMAS DIGITALES .......................................... 15

DISPOSITIVOS FPGA ................................................................................. 17

FAMILIAS COMERCIALES DE FPGAS. ........................................................... 19

FPGA’s de Xilinx. ............................................................................................... 19

FPGA’s de Altera. ............................................................................................... 19

FPGA’s de Actel ................................................................................................. 20

FAMILIA XILINX SPARTAN-3E FPGA............................................................ 21

TARJETA BASYS2 ...................................................................................... 22

Características Generales: ................................................................................. 23

TENDENCIAS TECNOLÓGICAS POR MERCADO DEL FPGA ............................. 25

Comunicaciones ................................................................................................. 25

Aeroespacial y Militar ......................................................................................... 26

Automotriz .......................................................................................................... 26

Industrial ............................................................................................................. 26

Electrónica de Consumo .................................................................................... 27

Procesamiento de Datos .................................................................................... 27

LENGUAJE VHDL ...................................................................................... 27

pág. 2

Formas de describir un circuito .......................................................................... 27

Secuencia de diseño .......................................................................................... 28

Ventajas de los lenguajes HDL .......................................................................... 31

Entity................................................................................................................... 31

Architecture ........................................................................................................ 33

Bibliotecas .......................................................................................................... 34

Paquetes ............................................................................................................ 34

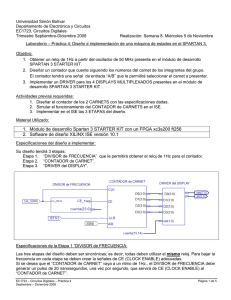

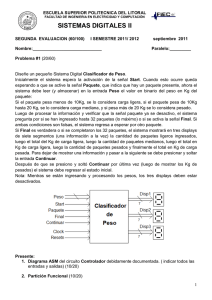

PROCEDIMIENTO Y DESCRIPCIÓN DE LAS ACTIVIDADES REALIZADAS .. 35

ADQUISICIÓN DE LA TARJETA BASYS2 ......................................................... 35

DESCARGA E INSTALACIÓN DE SOFTWARE ISE DESIGN SUITE 13.4 Y ADEPT

2.6.1 SYSTEM ....................................................................................................... 36

USO DEL SOFTWARE ISE DESIGN SUITE 13.4, ADEPT 2.6.1 SYSTEM Y

CONFIGURACIÓN DE LA TARJETA BASYS2 ............................................................... 38

Entidad y Arquitectura .......................................................................... 43

Simulación............................................................................................ 47

Diseño Estructural en VHDL ................................................................. 56

Configuración de la Tarjeta Basys2 ...................................................... 66

RESULTADOS ..................................................................................................... 74

DESARROLLO DE PRÁCTICAS UTILIZANDO LA TARJETA BASYS2 .................... 74

Practica 1 – Decoder Display ............................................................................. 74

Practica 2 - Contador Ascendente ..................................................................... 77

Practica 3 - Contador con salida a Display ........................................................ 81

Practica 4 - Encendido de un motor de CD....................................................... 83

Práctica 5 - Motor Reversible ............................................................................. 85

Practica 6 – Sumador Aritmético con Salida a Display ...................................... 88

Practica 7 – Unidad Aritmética Lógica (ALU) ..................................................... 97

Practica 8 – Elementos de Memoria (Flip-Flops) Pulsador .............................105

Practica 9 – Maquinas de Estados Finitos (FSM) ............................................108

Práctica 10 – Circuito Anti rebotes (Debounce Circuit) ...................................120

Practica 11 - Generación de una señal PWM .................................................125

Practica 12 - PWM con salida a display. ..........................................................129

Practica 13 – Señal PWM con Potenciómetro. ...............................................135

Practica 14 - Control de un motor debido a la señal de un sensor. .................140

Práctica 15 - Señal PWM controlada con Pushbuttons ...................................152

Práctica 16 - Contador Parametrizable (Mod_m_Counter) ..............................157

Práctica 17 - FIFO Buffer .................................................................................159

Práctica 18 – Comunicación Serial Puerto PS2 – Teclado ..............................162

CONCLUSIONES Y RECOMENDACIONES .................................................. 171

REFERENCIAS BIBLIOGRÁFICAS ................................................................. 172

pág. 3

INTRODUCCIÓN

Viabilidad de la Tarjeta Basys2 para su Implementación en el

Control de un Proceso

Ante las diferentes aplicaciones a realizar dentro del campo de los

Sistemas Digitales, nuevas tecnologías han emergido como herramientas a

las mismas. La adquisición de datos es una de estas aplicaciones, para la

cual se han utilizado diferentes herramientas como son sistemas basados en

microprocesadores, microcontroladores, CPLD, entre otros.

Con la aparición de los dispositivos FPGA’s (Fiel Programmable Gate

Array), se dispone de una nueva herramienta para los sistemas digitales. Su

alta disponibilidad de recursos lógicos, bloques de memoria SRAM, bloques

MAC, aumento de las entradas y salidas y sobre todo su reprogramación,

han colocado a estos dispositivos como una de las herramientas más

versátiles en estos momentos.

La opción de generar maquinas de estados finitos FSM (Finite State

Machines) de forma rápida y sencilla gracias a los lenguajes HDL (Lenguajes

de Descripción de Hardware), colocan a los dispositivos FPGA’s como una

solución eficaz ante el diseño de sistemas digitales.

La combinación del lenguaje HDL y los dispositivos FPGA’s permiten a

los diseñadores simular, probar e implementar físicamente circuitos digitales

sofisticados, reduciendo el tiempo que existe desde el diseño hasta la

producción final.

En este documento se propone analizar la viabilidad de la tarjeta

Basys2, basada en tecnología FPGA para su aplicación en el Control de un

Proceso.

Para demostrar la viabilidad y poner a prueba la Tarjeta Basys2 se

proponen una serie de prácticas que servirán como guía de aprendizaje de

las bases del Lenguaje de Programación VHDL (Very High Speed Hardware

Description Language), la instalación y uso del software XILINX ISE13.4, la

traducción por medio del software Digilent Adept y el manejo de la Tarjeta

Basys2.

pág. 4

Se recomienda al lector tener conocimientos de Electrónica Digital y

Electrónica Analógica Básica para la total comprensión de los temas

expuestos.

El FPGA utilizado es el XILINX Spartan 3E-100K por lo cual este

documento puede servir de referencia para el manejo de otras Tarjetas tales

como la Spartan-3 Starterboard, Spartan-3E Starterboard, Nexys-2 board,

Pegasus, Basys o de arquitecturas semejantes.

pág. 5

JUSTIFICACIÓN

Velocidad, Reprogramación, Múltiples I/0, Rendimiento, Costo

Los Dispositivos Lógicos Programables ofrecen múltiples ventajas en

el diseño de sistemas digitales; son una alternativa viable ante

microprocesadores, microcontroladores y ASIC’s (Circuitos Integrados de

Aplicación Específica) debido a su naturaleza reprogramable, alto

rendimiento y facilidad de uso; todo esto a un costo accesible.

Diseñadores de Sistemas Digitales pueden desarrollar prototipos para

el control de procesos de forma rápida y sencilla, evitando retrasos en la

adecuada elección de un microprocesador o microcontrolador. Con un FPGA

de gama baja se cuenta con los suficientes recursos para diseñar, probar e

implementar el control de múltiples procesos.

La Tarjeta Basys2 basada en el FPGA XILINX Spartan 3E-100K es un

laboratorio completo para el diseño de circuitos digitales ya que cuenta con

Memoria Flash, Interfaz programable USB2, push buttons, switches, led’s,

puerto PS2, puerto VGA y 4 módulos de expansión. Al tener todo lo

necesario en una sola placa se reduce el tiempo de salida del prototipo, ya

que se evita el tener que diseñar un PCB (Printed Circuit Board) o utilizar

protoboards que por lo general ocasionan fallos en las señales eléctricas.

El Lenguaje de Descripción de Hardware VHDL representa una

ventaja debido a lo sencilla e intuitiva que es su programación y su síntesis

que no ocupa demasiados recursos; en comparación al Lenguaje

Ensamblador que es más complejo y poco entendible, o el uso de Lenguajes

de alto nivel como lo son C, Basic, Java para microcontroladores y

microprocesadores que gastan recursos excesivamente.

El uso de múltiples microprocesadores embebidos en un FPGA

significa una de las mayores ventajas de estos dispositivos lógicos

programables, la creación de un microprocesador a la medida proporciona un

diseño flexible y escalable que satisface las necesidades del productor y

evita el hecho de que el microprocesador, microcontrolador o ASIC elegido

para el control del proceso quede obsoleto.

El mercado de los FPGA’s ha ido en aumento y XILINX, la empresa

creadora de estos dispositivos lógicos programables se coloca como líder

mundial con el 56% de las ventas de FPGA’s, seguido por Altera, Lattice y

pág. 6

Actel. Las aplicaciones finales que se le dan a estos dispositivos suelen ser

diversas y se presentan en campos tales como telecomunicaciones, industria

automotriz, industria de consumo, entre otros.

Este documento busca además de demostrar la viabilidad de la

Tarjeta Basys2 para ser utilizada en el control de un proceso, beneficiar y

orientar a todos aquellos que se comienzan a sumergir dentro del campo de

los dispositivos lógicos programables para el diseño de sistemas digitales a

través de FPGA’s, de modo que puedan hacer consideraciones para la

elección de la arquitectura que controle sus procesos.

pág. 7

OBJETIVOS

Objetivo General

-

Determinar la Viabilidad de la Tarjeta Basys2 para Implementar el

Control de un Proceso

Objetivos Específicos

-

Manejar VHDL (Very High Speed Integrated Circuit Hardware

Description Language) para la Descripción de circuitos Digitales en

un FPGA Spartan 3E

-

Manejar la Tarjeta Basys2 basada en el FPGA XILINX Spartan 3E

100K y sus Similares

-

Manejar el Software compilador y traductor necesario para utilizar

el FPGA XILINX Spartan 3E 100K

-

Determinar e Implementar el control de un proceso

pág. 8

ÁREA DE PARTICIPACIÓN

Ingeniería Electrónica – “Ciencia Aplicada para Crear e Innovar”

El desarrollo de este documento así como las prácticas propuestas se

han llevado a cabo en el Instituto Tecnológico de Tehuacán en el área de

Ingeniería Eléctrica-Electrónica por parte del equipo de Residentes

investigadores del área.

En la Figura1 se muestra el organigrama del Instituto Tecnológico de

Tehuacán, siendo el área de Ingeniería Electrónica dentro del departamento

de investigación el lugar donde se ha desarrollado este proyecto.

Figura 1 - Organigrama del Instituto Tecnológico de Tehuacán

pág. 9

PROBLEMAS A RESOLVER

Cronograma de Actividades

A continuación se exponen los problemas a resolver para el desarrollo

del proyecto, asi como una breve descripción de los mismos.

Búsqueda y Compra de Tarjeta basada en FPGA XILINX Spartan 3E

100K

-

Duración: 2 semanas

-

Objetivo: Buscar y Comprar una Tarjeta de prototipos basada en

un FPGA

-

Descripción: Durante el tiempo propuesto se buscará en internet y

proveedores locales una Tarjeta de Prototipos basada en un FPGA

sencillo.

Instalación y Manejo del Software ISE Design Suite 13.4 y Digilent Adept

-

Duración: 1 semana

-

Objetivo: Descargar e instalar el software necesario para el manejo

de la Tarjeta basada en el FPGA de elección

-

Descripción: Durante el tiempo propuesto se descargarán e

instalarán los programas necesarios para el manejo de la Tarjeta

adquirida, así como el acondicionamiento del equipo de cómputo

necesario.

Investigación de la Arquitectura de la Tarjeta basada en FPGA

-

Duración: 1 semana

-

Objetivo: Investigar y analizar la arquitectura de la Tarjeta basada

en FPGA

pág. 10

-

Descripción: Durante el tiempo propuesto se buscarán y analizarán

las hojas de datos de la Tarjeta adquirida así como del FPGA que

contenga.

Manejo del Lenguaje de Programación VHDL

-

Duración: 3 semanas

-

Objetivo: Conocer y manejar el lenguaje de Descripción de

Hardware VHDL

-

Descripción: Durante el tiempo propuesto se buscará información

acerca del lenguaje VHDL en biblioteca e internet y se aprenderán

las bases del mismo para la programación de la Tarjeta basada en

FPGA.

Desarrollo e Implementación de Prácticas de Circuitos Digitales básicos

con VHDL y la Tarjeta basada en FPGA

-

Duración: 3 semanas

-

Objetivo: Diseñar e Implementar en la Tarjeta basada en FPGA

circuitos digitales combinacionales y secuenciales básicos.

-

Descripción: Durante el tiempo propuesto se diseñaran e

implementarán prácticas de circuitos combinacionales y

secuenciales básicos programados en lenguaje VHDL y

compilados a través del software necesario para la descarga hacia

la Tarjeta basada en FPGA.

Desarrollo e Implementación de Máquinas de Estados Finitos (FSM)

-

Duración: 3 semanas

-

Objetivo: Diseñar e implementar circuitos digitales secuenciales

avanzados.

pág. 11

-

Descripción: Durante el tiempo propuesto se diseñaran e

implementarán prácticas de circuitos combinacionales avanzados

utilizando para ello Maquinas de Estados Finitos (FSM). Se

analizarán las diversas opciones con las que se cuenta para

diseñarlas y se elegirá la más viable.

Acondicionamiento de Entradas y Salidas de la Tarjeta basada en FPGA

para adquisición de datos y activación de actuadores.

-

Duración: 2 semanas

-

Objetivo: Acondicionar las señales eléctricas para hacer interfaces

humano-sensores-actuadores-CI-tarjeta

-

Descripción: Durante el tiempo propuesto se investigará acerca de

los dispositivos analógicos necesarios para hacer la interconexión

de actuadores, sensores, circuitos integrados y demás dispositivos

que interactúen con la tarjeta basada en FPGA para su correcto

funcionamiento sin dañarla; así como las etapas de potencia

necesarias.

Desarrollo e Implementación del Control de un Proceso por medio de la

Tarjeta basada en FPGA

-

Duración: 3 semanas

-

Objetivo: Controlar un Proceso a través de la Tarjeta basada en

FPGA seleccionada

-

Descripción: Durante el tiempo propuesto se buscará una

aplicación de control utilizando la tarjeta basada en FPGA

seleccionada, se diseñará, implementará y se determinará la

viabilidad de su uso.

pág. 12

ALCANCES Y LIMITACIONES

Alcances

Las prácticas expuestas en este documento pretenden demostrar la

viabilidad del uso de una tarjeta de desarrollo basada en FPGA para su

implementación en el control de un proceso, además servirán de guía para

todos aquellos que busquen diseñar sistemas digitales con dispositivos

lógicos programables.

El impacto de este proyecto beneficia a la carrera de Ingeniería

Electrónica en sus cursos de Electrónica Digital y Diseño Digital con VHDL.

La tarjeta Basys 2 cuenta con 4 módulos de expansión PMOD los

cuales cuentan con 4 entradas y salidas externas cada uno que nos permiten

ingresar señales eléctricas de sensores u otros dispositivos, o enviar señales

eléctricas para activar actuadores o establecer comunicación entre el FPGA y

un ordenador.

La Tarjeta Basys2 nos permite trabajar a velocidades de 50Mhz y

controlar múltiples procesos de forma paralela, lo cual es su principal ventaja

en comparación a un microcontrolador.

Limitaciones

La adquisición de la Tarjeta Basys2 en el territorio nacional es

complicada; los distribuidores autorizados de la empresa Digilent se

encuentran fuera del estado de Puebla. Es más sencillo pedirla directamente

al proveedor en USA pero se debe pagar un impuesto aduanal.

Se debe analizar el proceso a controlar para determinar si las entradas

y salidas con las que cuenta la Tarjeta Basys2 son suficientes para su

implementación.

Los componentes electrónicos con los que se cuenta dentro del área

de Ingeniería Electrónica son insuficientes, por lo cual se opta por adquirirlos

en distribuidores locales generando gastos adicionales.

El voltaje de las entradas y salidas de la Tarjeta Basys2 utiliza

tecnología LVTTL de 3.3V por lo tanto se requiere acondicionar

pág. 13

correctamente las señales eléctricas. Además, no cuenta con puerto serial,

LCD (Liquid Crystal Display), ni convertidor analógico-digital integrados en la

tarjeta, por lo que hay que comprarlos y diseñar su interfaz.

La licencia del software ISE Design Suite 13.4 utilizada es de versión

gratuita, por lo tanto para proyectos de mayor volumen o que utilicen FPGA’s

mas avanzados se debe comprar la licencia completa.

El control de procesos más sofisticados está sujeto a la disposición de

recursos económicos, equipo de laboratorio disponible en el área de

Ingeniería Electrónica y componentes electrónicos extras.

pág. 14

MARCO TEÓRICO

Sistemas de Control y Sistemas Digitales

El control de procesos a través de tecnologías reprogramables es un

área en constante crecimiento con dispositivos lógicos programables

evolucionando rápidamente.

Un proceso es un conjunto de actividades o eventos que se realizan

o suceden (alternativa o simultáneamente) bajo ciertas circunstancias con un

fin determinado.

Los sistemas de control son parte integrante de la sociedad moderna y

sus numerosas aplicaciones están alrededor de nosotros: Un sistema de

control esta formado por subsistemas y procesos unidos con el fin de

controlar las salidad de los procesos. En su forma más sencilla, un sistema

de control produce una salida o respuesta para una entrada o estímulo dado.

En la Figura 2 se muestra un sistema de control simple.

Entrada; Estimulo

Salida; Respuesta

Sistema de Control

Respuesta Deseada

Respuesta Real

Figura 2 – Diagrama Sistema de Control

Los sistemas de control se dividen en sistemas en lazo abierto y en

lazo cerrado. Un sistema genérico en lazo abierto se ilustra en la Figura 3 (a),

formado por un subsistema llamado transductor de entrada, que convierte la

forma de la entrada a la empleada por el controlador. El controlador maneja

un proceso o planta. A veces, la entrada se denomina referencia, mientras

que la salida se puede llamar variable controlada. Otras señales, por ejemplo

las perturbaciones se muestran agregadas al controlador y a las salidas del

proceso por medio de puntos de suma que dan la suma algebraica de sus

señales de salida por medio de signos asociados. La característica distintiva

de un sistema en lazo abierto es que no puede compensar ninguna

perturbación que se sume a la señal de actuación del controlador;

simplemente se comandan por la entrada.

pág. 15

Figura 3 – Diagramas a bloques de Sistemas de Control

a) En Lazo Abierto b) En Lazo Cerrado

La estructura genérica de un sistema en lazo cerrado se ilustra en la

Figura 3(b). En diferencia a los sitemas en lazo abierto estos compensan

perturbaciones al medir la respuesta de salida, alimentando esa medida a

una trayectoria de realimentación comparando esa respuesta con la entrada

en el punto de suma. Si hay alguna diferencia entre las dos respuestas, el

sistema acciona el proceso, por medio de una señal de actuación, para hacer

la corrección. 1

El controlador (o compensador) puede ser un dispositivo lógico

programable o un microcontrolador que ejecute las acciones de control.

Un sistema digital es un conjunto de dispositivos destinados a la

generación,

transmisión,

procesamiento

o

almacenamiento

de

señales digitales. También un sistema digital es una combinación de

dispositivos diseñados para manipular cantidades físicas o información que

estén representadas en forma digital; es decir, que sólo puedan tomar

valores discretos.

Para el análisis y la síntesis de sistemas digitales binarios se utiliza

como herramienta el álgebra de Boole.

1

Norman S. Nise, Sistemas de Control para Ingeniería. (1a Edición), Compañía Editorial Continental, Mexico: 2004

pág. 16

Sistemas digitales combinacionales: Aquellos en los que sus

salidas sólo depende del estado de sus entradas en un momento

dado. Por lo tanto, no necesita módulos de memoria, ya que las

salidas no dependen de los estados previos de las entradas.

Sistemas digitales secuenciales: Aquellos en los que sus salidas

dependen además del estado de sus entradas en un momento dado,

de estados previos. Esta clase de sistemas necesitan elementos

de memoria que recojan la información de la “historia pasada” del

sistema.

Dispositivos FPGA

Un FPGA (Field programable gate array) es un dispositivo lógico que

contiene una matriz de celdas lógicas idénticas, con interconexiones

programables (switches programables). La estructura conceptual de un

dispositivo FPGA se muestra en la Figura 4. Una celda lógica puede ser

configurada (programada) para realizar una función simple, y un switch

programable puede ser configurado para proveer interconexión a través de

las celdas lógicas. Un diseño puede ser implementado en un FPGA

especificando la función de cada celda lógica y estableciendo selectivamente

la conexión de cada switch programable. Una vez que el diseño y la síntesis

son completados, podemos utilizar un simple cable adaptador para descargar

la celda lógica deseada y la configuración del switch programable al

dispositivo FPGA, para obtener el circuito digital diseñado.

Figura 4 – Estructura Conceptual FPGA

pág. 17

Las celdas lógicas usualmente contienen un pequeño circuito

combinacional y un flip-flop D (DFF). El método mas común para

implementar un circuito combinacional configurable es a través de una tabla

de búsqueda (look-up table LUT). Una LUT de n entradas puede ser

considerada como una pequeña memoria de 2 n-por-1. Escribiendo

adecuadamente el contenido de la memoria, podemos utilizar una LUT para

implementar cualquier función combinacional de n entradas. El diagrama

conceptual de una celda lógica basada en una LUT de 3 entradas es

mostrado en la Figura 5 (a). La función a⊕b⊕c implementada en una LUT

de 3 entradas es mostrada en la Figura 5(b). Nótese que la salida de la LUT

puede ser utilizada directamente o puede ser almacenada en el Flip-Flop D.

Figura 5 - LUT (Look-up Table)

Macro Celda (Macro cell). La mayoría de los dispositivos FPGA

cuentan con macro celdas o macro bloques embebidos. Estos son diseñados

y fabricados a nivel de transistores, y sus funcionalidades complementan a

las celdas lógicas. Comúnmente las macro celdas usadas incluyen bloques

de memoria, multiplicadores combinacionales, circuitos de manejo de reloj y

circuitos de interface entre entradas y salidas. Dispositivos FPGA mas

sofisticados suelen contener uno o más núcleos de procesador

prefabricados.2

2

Pong P. Chu, FPGA Prototyping by VHDL Examples XILINX Spartan-3 Version. (1a Edición), John Wiley

& Sons Inc, Hoboken, New Jersey: 2008

pág. 18

Familias comerciales de FPGAs.

Existen tres fabricantes mayoritarios en la distribución de FPGA’s y

software de soporte, estos son Xilinx, Altera y Actel. Sin embargo, en el

mercado mundial también existen otros como Lucent, Texas Instruments,

Philips, QuickLogic, Cypress, Atmel, entre otros. No obstante, por la

importancia de las tres primeras compañías se mencionaran algunas de las

familias lógicas que ofrecen.

FPGA’s de Xilinx.

Son uno de los fabricantes más fuertes en el nivel mundial. Sus

FPGAs están basados en la tecnología SRAM, son dispositivos

reprogramables (Many-Times Programable, MTP) y programables en

sistema (ISP).

Sus principales familias son: XC3000, XC4000, XC Virtex y XC

Spartan. Dichos dispositivos están compuestos por módulos lógicos CLBs,

basados en tablas de búsqueda. Cada CLB contiene circuitos que permiten

realizar operaciones aritméticas eficientes. Los usuarios también pueden

configurar las tablas de búsqueda como celdas lectura/escritura (read/write)

de RAM. Asimismo, a partir de la seria XC 4000 se incluye un generador

interno de señal de reloj, con 5 diferentes frecuencia.

Además de los CLBs, los FPGAs de este fabricante incluyen otros

bloques complejos que configuran la entrada de los pines físicos, estos a si

ves conectan el interior del dispositivo con el exterior y los bloques son

llamados bloques de Entrada/Salida (Input/Output Blocks, IOBs). Cada

IOB contiene una lógica compleja que permite que un pin actué como

entrada, salida o triestado (el triestado puede tomar valores de 0, 1 o de alta

impedancia).

FPGA’s de Altera.

Altera ofrece dos familias de FPGAs con características diferentes,

pero conservando algunas básicas que representan las ventajas originales

de las primeras familias estándar: FLEX 6000, 8000 y 10K; así como la más

novedosa, APEX 20K. Las primeras familias estándar, la FLEX 6000 y la

8000 aún se utilizan ampliamente. La serie FLEX (Matriz Flexible de

Elementos Lógicos, Flexible Logic Element Matrix) estándar contiene un

numero considerando de compuertas en tecnología SRAM con tablas de

búsqueda, agregando mayor flexibilidad a los diseños.

pág. 19

La serie estándar FLEX combina la arquitectura de los CPLD con los

FPGAs. El dispositivo consiste de una arquitectura muy parecida a la de un

CPLD; en su nivel más bajo de la jerarquía tiene un conjunto de tablas de

búsqueda, en lugar de un bloque muy similar a un SPLD, por ello se

considera un FPGA. El modulo lógico básico, nombrado por Altera, elemento

lógico (Logic Element), contiene una LUT de 4 entradas, un flip-flop y un

elemento de acarreo (carry) de propósito especial para circuito aritméticos. El

elemento lógico también incluye circuitos en cascada, que permiten una

implementación eficiente de funciones AND amplias.

Esta arquitectura agrupa elementos lógicos en grupos de 8, y los llama

bloques de arreglos lógicos (Arrays Logic Blocks, ALBs). Cada ALB,

contiene una interconexión local que le permite conectarse con otro ALB y a

la vez, la misma interconexión sirve para conectarse a la interconexión global

de la crossbar (matriz de interconexiones), nombrada por Altera como

FastTrack. Así, las interconexiones se hacen al estilo de los CPLDs, pero la

configuración de los bloques de arreglos lógicos utiliza tecnología SRAM

propia de los FPGAs.

FPGA’s de Actel

Actel ofrece una seria de familias OTP que resultan ampliamente

utilizadas después de haber probado satisfactoriamente un diseño (emigrar a

otro FPGA). Las principales son: la serie estándar ACT, y las más nuevas por

orden cronológico de aparición, sX, sX-A, mX y eX. Todas las anteriores son

programables fuera del sistema (OPS). También ofrece una familia

reprogramable a la llamada Pro ASIC (por ser de alta densidad de

componentes, Actel no la considera parte de los FPGAs), basada en una

tecnología Flash EEPROM programable en sistema (ISP).

Los FPGAs de Actel, emplean como modulo o elemento básico una

estructura tipo arreglo fijo de compuertas. La lógica del arreglo está

dispuesta en renglones de módulos lógicos interconectables, rodeados hacia

afuera por módulos de E/S. la estructura de interconexiones consiste en

pistas o líneas fijas de interconexión, horizontales y verticales, con

segmentos de alambrado. Hay muchas pistas en cada canal entre los

renglones de la lógica. Las pistas verticales son menos y pasan sobre los

canales horizontales y los módulos lógicos.

El FPGA de Actel utiliza tecnología antifusible que proporciona una

programación permanente y no volátil. El dispositivo tiene muchos

antifusibles para conectar las entradas y salidas de los módulos de lógica y

E/S, a los segmentos de alambrado de los canales. También tiene antifusible

pág. 20

que interconectan los segmentos de alambrado entre las pistas para ofrecer

conexiones de diferentes longitudes.

Una de las principales características de los módulos lógicos de los

FPGAs de Actel, es que los módulos no se programan para que efectúen una

operación, sino que toda la programación se hace mediante antifusibles en

las pistas de alambrado.3

Familia Xilinx Spartan-3E FPGA

El FPGA utilizado en este proyecto es el Spartan-3E 100K de la marca

Xilinx.

Las características y capacidades de la familia Spartan-3E se han

optimizado para un alto volumen y aplicaciones de bajo costo. Debido a su

excepcional bajo costo, los FPGA de la familia Spartan-3E son viables para

un extenso mercado de aplicaciones electrónicas, incluyendo accesos de

banda ancha, redes locales, control de procesos y equipos de televisión

digital.

Celdas Lógicas, Slice, y Bloques Lógicos Configurables (CLB). El

elemento mas básico de un dispositivo Spartan-3 es una celda lógica (Logic

Cell LC), el cual contiene LUTs de 4 entradas y un Flip-Flop D similar al de la

figura 3. Además, una celda lógica contiene un circuito de acarreo (carry), el

cual es usado para implementar funciones aritméticas, y un circuito

multiplexor. Las LUT pueden ser configuradas como memorias estáticas de

acceso aleatorio (Static Random Access Memory SRAM) de 16-por-1 o como

registros de corrimiento (Shift Register) de 16-bit.

Para incrementar la flexibilidad y mejorar el rendimiento, 8 celdas

lógicas son combinadas con una estructura especial en el ruteo interno. En

términos del fabricante Xilinx, 2 celdas lógicas son agrupadas para formar un

Slice, y 4 slices son agrupado para formar un bloque lógico configurable

(Configurable Logic Block (CLB)).

Macro Celdas del Spartan-3. El dispositivo Spartan-3 cuenta con 4

tipos de macro bloques: multiplicador combinacional, bloque RAM, digital

clock manager (DCM) y bloque de entrada/salida (IOB). El bloque

multiplicador combinacional acepta dos números de 18-bits como entrada y

calcula el producto. El bloque RAM es una SRAM de 18K-bit síncrona que

3

Menéndez Ortiz María Alejandra, Arquitectura FPGA para la adquisición de Datos Térmicos. Universidad

del Mar Campus Puerto Escondido Oaxaca México: 2010.

pág. 21

puede ser configurada de distintas formas. El DCM usa un ciclo “digitaldelayed” para reducir los problemas con los tiempos y controlar la frecuencia

y fase de las señales de reloj. Las IOB controlan el flujo de datos entre los

pines de E/S y la lógica interna.4 La arquitectura del Spartan-3E es mostrada

en la Figura 6.

La Familia Spartan-3E cuenta con 5 miembros que ofrecen distintas

densidades, las cuales van desde los 100,000 hasta los 1.6 millones de

compuertas, tal y como se muestra en la Tabla 1.

Tabla 1- Densidades Familia Spartan-3E

Las características generales del Spartan 3-E se pueden encontrar en

su datasheet a través del siguiente enlace 5

www.xilinx.com/support/documentation/data_sheets/ds312.pdf

Tarjeta Basys2

La tarjeta Basys2 es una plataforma para el diseño e implementación

de circuitos digitales. La tarjeta esta construida en base a un FPGA Spartan3E de Xilinx y un controlador USB Atmel AT90USB2. La tarjeta Basys2

provee el hardware necesario listo para usarse capaz de soportar circuitos

que van desde el rango de lo básico hasta el control complejo de procesos.

Una amplia gama de dispositivos de E/S y todas las conexiones del FPGA

son incluidas, por lo que incontables diseños pueden ser creados sin la

necesidad de componentes adicionales.

4

Pong P. Chu, FPGA Prototyping by VHDL Examples XILINX Spartan-3 Version. (1a Edición), John Wiley

& Sons Inc, Hoboken, New Jersey: 2008

5

Sitio web oficial de Xilinx sección documentación de productos.

www.xilinx.com/support/documentation/data_sheets/ds312.pdf

pág. 22

Figura 6 – Arquitectura Spartan 3-E FPGA

Cuatro conectores de expansión estándar permiten a la tarjeta Basys2

crecer utilizando circuitos diseñados por el usuario o PMods. (Los PMods son

módulos de E/S analógicos y digitales de bajo costo que ofrecen conversión

A/D y D/A, drivers para motor, entradas de sensor y muchas otras

características). Las señales en los conectores de 6 pines están protegidas

contra corto circuito, garantizando una larga vida de funcionamiento en

cualquier ambiente. La tarjeta Basys2 trabaja en cualquier versión del

compilador Xilinx ISE tools, incluyendo la licencia gratuita WebPack.

Contiene un cable USB que le proporciona energía y es utilizado como

interfaz de programación, por lo que ninguna otra fuente de poder o cable de

programación es requerido. 6 En la Figura 7 se muestra el diagrama a

bloques de la tarjeta Basys2.

Características Generales:

-

Xilinx Spartan 3-E FPGA, 100K or 250K gate

6

Manual de Referencia Tarjeta Basys2:http://www.digilentinc.com/Data/Products/BASYS2/Basys2_rm.pdf

pág. 23

-

FPGA con multiplicadores de 18-bit, 72Kbits de bloque RAM dual-port,

y 500MHz+ velocidad de operación

Puerto USB2 full-speed para la configuración y transferencia de datos

hacia el FPGA (utilizando el software Adept 2.0 disponible en

descarga gratuita)

XCF02 Platform Flash ROM que almacena las configuraciones del

FPGA

Frecuencia de oscilación ajustable (25, 50, and 100 MHz), además

cuenta con socket para un oscilador extra

3 reguladores de voltaje incluidos (1.2V, 2.5V, and 3.3V) que permiten

el uso de fuentes externas de 3.5V a 5.5V.

Figura 7– Diagrama a bloques Tarjeta Basys2

-

8 LEDs, 4 displays de siete segmentos, 4 pushbuttons, 8 slide

switches, Puerto PS/2, y un puerto VGA de 8-bit

Cuatro conectores de 6-pines para E/S del usuario, y compatibles con

los circuitos Digilent PMOD.

La compra, asi como la documentación completa y ejemplos acerca de

la tarjeta Basys2 se encuentran en el siguiente enlace7.

7

Documentación Completa, Compra y ejemplos de la Tarjeta Basys2 de Digilent INC.

http://www.digilentinc.com/Products/Detail.cfm?NavPath=2,400,790&Prod=BASYS2

pág. 24

Tendencias Tecnológicas por Mercado del FPGA

Las tendencias de Aplicaciones FPGA a nivel Mundial se muestran en

la Figura 8.

Figura 8– Aplicaciones FPGA a nivel Mundial

Comunicaciones

De acuerdo a la empresa de consultoría industrial Gartner, durante el

ciclo fiscal 2008-2009, el mercado de la tecnología FPGAs para

Comunicaciones generó aproximadamente USD $ 1,45 millones de dólares,

mientras que las proyecciones para el 2012 ascienden a unos USD $ 2,096

millones de dólares.

En cuanto a la cantidad de patentes registradas con esta tecnología

para Comunicaciones, indica que a la fecha se tiene un total de 2,527

documentos y solicitudes a nivel internacional. Los campos en donde se ha

generado mayor propiedad intelectual son: Comunicaciones ópticas,

Comunicaciones Inalámbricas/Alámbricas, Antenas, Moduladores y

Codificadores y Redes.

pág. 25

Aeroespacial y Militar

El mercado de la tecnología FPGA en el 2008 fue de

aproximadamente USD$447 millones y se estima que para el 2012 sea de

USD$717 millones.

Aplicaciones:

-

Sistemas de radar

Enlaces de comunicaciones de alta velocidad

Misiles

Aplicaciones de alta confiablidad en el espacio

Procesamiento digital de señales robusto y de alta seguridad

Automotriz

El mercado de la tecnología FPGA en el 2008 fue de

aproximadamente USD$83 millones y se estima que para el 2012 sea de

USD$358 millones.

-

Aplicaciones:

GPS

Infoentretenimiento

Control de frenos

Control de luces

Sistemas de seguridad

Industrial

Los sectores industriales que mayor consumo de FPGAs registran son

para aplicaciones de Sistemas de Manufactura, Equipo Médico y Monitoreo

de Pacientes, Seguridad, Administración de Energía, Pruebas y Mediciones,

Redes y Domótica. En el 2008 el sector industrial recaudó 852 millones de

dólares (mdd) y se estima que para el 2012 ascienda a unos 1,406 mdd. La

cantidad de patentes internacionales en el sector Industrial con tecnología

FPGAs llega a 524 documentos y solicitudes.

pág. 26

Electrónica de Consumo

En el área de electrónica de consumo, los FPGAs generaron en el

2008 un total de 469 mdd por ingresos y se estima que para el año 2012 se

eleve a 672 mdd. En cuanto a propiedad intelectual a nivel internacional se

han registrado 102 documentos y solicitudes. Las aplicaciones más comunes

en las que son utilizados son: Audio, Video y Equipo de Oficina.

Procesamiento de Datos

El mercado de FPGAs en el 2008 para este campo sumó 312 mdd y

se tiene proyectado que para el año 2012 alcance los 335 mdd. Sus

principales aplicaciones han sido para el desarrollo de Súper computadoras,

Tarjetas Inteligentes, Servidores, Procesadores y Computadoras Personales

(PCs). 8

Lenguaje VHDL

VHDL es el acrónimo que representa la combinación

de VHSIC y HDL, donde VHSIC es el acrónimo de Very High Speed

Integrated Circuit y HDL es a su vez el acrónimo de Hardware Description

Language.

Es un lenguaje definido por el IEEE (Institute of Electrical and

Electronics Engineers) (ANSI/IEEE 1076-1993) usado por ingenieros para

describir circuitos digitales.

Aunque puede ser usado de forma general para describir cualquier

circuito se usa principalmente para programar PLD (Programable Logic

Device - Dispositivo Lógico Programable), FPGA (Field Programmable Gate

Array), ASIC y similares.

Formas de describir un circuito

Dentro del VHDL hay varias formas con las que podemos diseñar el

mismo circuito y es tarea del diseñador elegir la más apropiada.

8

Red Estrategica de Tecnologia FPGA (AERI – FPGA):

http://www.conacyt.gob.mx/fondos/institucionales/Tecnologia/Avance/Redes/1-FPGA-FUMEC-AERI.pdf

pág. 27

Funcional: Describimos la forma en que se comporta el circuito. Esta

es la forma que más se parece a los lenguajes de software ya que la

descripción es secuencial. Estas sentencias secuenciales se

encuentran dentro de los llamados procesos en VHDL. Los procesos

son ejecutados en paralelo entre sí, y en paralelo con asignaciones

concurrentes de señales y con las instancias a otros componentes.

Flujo de datos: describe asignaciones concurrentes (en paralelo) de

señales.

Estructural: se describe el circuito con instancias de componentes.

Estas instancias forman un diseño de jerarquía superior, al conectar

los puertos de estas instancias con las señales internas del circuito, o

con puertos del circuito de jerarquía superior.

Mixta: combinación de todas o algunas de las anteriores.

En VHDL también existen formas metódicas para el

de máquinas de estados, filtros digitales, bancos de pruebas etc.

diseño

Secuencia de diseño

El flujo de diseño de un sistema es:

Construcción del diagrama en bloque del sistema.

Elaboración del código en VHDL para cada modulo, para sus

interfaces y sus detalles internos. Como el VHDL es un lenguaje

basado en texto, se puede utilizar cualquier editor para esta tarea,

aunque el entorno de los programas de VHDL incluye su propio editor

de texto.

Compilación. El compilador de VHDL analiza el código y determina

los errores de sintaxis y chequea la compatibilidad entre módulos.

Crea toda la información necesaria para la simulación.

Simulación funcional. En este tipo de simulación se comprueba que

el código VHDL ejecuta correctamente lo que se pretende.

Síntesis. En este paso se adapta el diseño anterior a un hardware en

concreto, ya sea una FPGA o un ASIC. Hay sentencias del lenguaje

que no son sintetizables, como por ejemplo divisiones o

exponenciaciones con números no constantes. El hecho de que no

todas las expresiones en VHDL sean sintetizables es que el VHDL es

un lenguaje genérico para modelado de sistemas (no sólo para diseño

pág. 28

de circuitos digitales), por lo que hay expresiones que no pueden ser

transformadas a circuitos digitales. Durante la síntesis se tiene en

cuenta la estructura interna del dispositivo, y se definen restricciones,

como la asignación de pines. El sintetizador optimiza las expresiones

lógicas con objeto de que ocupen menor área, o bien son eliminadas

las expresiones lógicas que no son usadas por el circuito.

Simulación post-síntesis. En este tipo de simulación se comprueba

que el sintetizador ha realizado correctamente la síntesis del circuito,

al transformar el código HDL en bloques lógicos conectados entre sí.

Este paso es necesario ya que, a veces, los sintetizadores producen

resultados de síntesis incorrectos, o bien realiza simplificaciones del

circuito al optimizarlo.

Ubicación y enrutamiento. El proceso de ubicación consiste en situar

los bloques digitales obtenidos en la síntesis de forma óptima, de

forma que aquellos bloques que se encuentran muy interconectados

entre sí se sitúen próximamente. El proceso de enrutamiento consiste

en interconectar adecuadamente los bloques entre sí, intentando

minimizar retardos de propagación para maximizar la frecuencia

máxima de funcionamiento del dispositivo.

Anotación final. Una vez ha sido completado el proceso de ubicación

y enrutamiento, se extraen los retardos de los bloques y sus

interconexiones, con objeto de poder realizar una simulación temporal

(también llamada simulación post-layout). Estos retardos son anotados

en un fichero SDF (Standard Delay Format) que asocia a cada bloque

o interconexión un retardo mínimo/típico/máximo.

Simulación temporal. A pesar de la simulación anterior puede que el

diseño no funcione cuando se programa, una de las causas puede ser

por los retardos internos del chip. Con esta simulación se puede

comprobar, y si hay errores se tiene que volver a uno de los pasos

anteriores.

Programación en el dispositivo. Se implementa el diseño en el

dispositivo final y se comprueba el resultado.

En la Figura 9 se muestra el diagrama de flujo con la secuencia de

diseño necesaria.

pág. 29

Inicio

Diagrama a bloques del

sistema

Código en VHDL

No

Compilación

Si

Simulación

Funcional

No

Si

No

Síntesis

Si

Simulación

Pos-Sintesis

No

Si

Ubicación y

Enrrutamiento

Fichero SDF

Anotación Final

Simulación

Temporal

No

Programación del

Dispositivo

Fin

Figura 9- Diagrama de Flujo Secuencia de Diseño

pág. 30

Ventajas de los lenguajes HDL

El empleo de HDL presenta ventajas respecto al empleo de

descripciones basadas en esquemáticos. Algunas de ellas son las siguientes:

1)

Puesto que una descripción HDL es simplemente un fichero de

texto, es mucho más portable que un diseño esquemático, que

debe ser visualizado y editado empleando la herramienta gráfica

específica del entorno de CAD (Computer-Aided Design - Diseño

asistido por ordenador) con el que se ha creado.

2)

Una descripción esquemática únicamente describe el diseño de

manera estructural, mostrando los módulos y la conexión entre

ellos. Por el contrario, la descripción del circuito usando un HDL

puede realizarse bien mostrando la estructura, o bien describiendo

el comportamiento. Es decir, los HDL permiten describir el

comportamiento que se desea que tenga el circuito, sin hacer

ninguna referencia a su estructura. Las herramientas de síntesis

permiten generar automáticamente la estructura del circuito lógico a

partir de la descripción de su comportamiento.

3)

El mismo HDL que se ha usado para la descripción del circuito,

puede emplearse para describir los vectores de test y los resultados

esperados del test. Los vectores de test son los valores de las

señales aplicadas a los pines de entrada del circuito con la finalidad

de probar si el funcionamiento del circuito es correcto. Así pues,

pueden realizarse los programas de test (vectores de test e

instantes en los cuales son aplicados) del circuito a medida que se

diseña el propio circuito, pudiéndose con ello ir realizando

diferentes pruebas a medida que se avanza en el diseño. Como

ventajas añadidas, la descripción de los programas de test usando

HDL es altamente portable y repetible.

Entity

La entity define la interfaz externa de la entidad de diseño. Incluye:

– El nombre de la entidad de diseño.

– La lista de las señales de salida y de entrada que componen la

interfaz (normalmente se aplica el convenio de escribir primero las salidas y a

continuación las entradas). A cada una de estas señales se le denomina

pág. 31

puerto (port). Existen tres tipos de puertos: in (entrada), out (salida) e inout

(bidireccional).

La palabra reservada entity, seguida del nombre de la interfaz y de las

palabras reservadas is port, indica el comienzo de la definición de la interfaz.

A continuación, se especifica el nombre de cada uno de los puertos, su

dirección (in, out o inout) y su tipo. En el ejemplo mostrado en la Figura 10,

todos los puertos son señales del tipo std_logic.

Finalmente, las palabras reservadas end entity, seguidas del nombre

de la interfaz, indican el final de la definición.

Figura 10 – Definición de Entidad de compuertas NOT, XOR y AND

Los nombres definidos por el usuario deben comenzar por una letra,

seguida opcionalmente por cualquier secuencia de letras, números y

caracteres guion bajo, con la limitación de que ni pueden aparecer dos

guiones bajos seguidos, ni el guion bajo puede ser el ultimo caracter del

nombre. En VHDL no se diferencia entre los caracteres en mayúscula y en

minúscula.

Los tipos de señales utilizados en el lenguaje VHDL se muestran en la

Tabla 2.

TIPO

Características

BIT

En este tipo las señales solo toman los valores de "1" y

"0"

Booleana

En este tipo las señales solo toman los valores de True y

False

pág. 32

Std_logic

En este tipo las señales toman 9 valores, entre ellos

tenemos: "1", "0", "Z" (para el 3er estado), "-" (para

los opcionales).

Integer

En este tipo las señales toman valores enteros. Los 1 y

los 0 se escriben sin “

Bit_Vector

En este tipo los valores de las señales son una cadena de

unos y ceros. Ejemplo: “1000”

Std_Logic_Vector

En este tipo los valores de las señales son una cadena de

los nueve valores permisibles para el tipo std_logic.

Character

Contiene todos los caracteres ISO de 8 bits, donde los

primeros 128 son los caracteres ASCII.

Tabla 2 – Tipos de Datos VHDL

Architecture

La architecture describe el comportamiento o la estructura de la

entidad de diseño. En la Figura 11 se muestra la arquitectura de las

compuertas NOT, XOR y AND.9

Figura 11 – Arquitectura compuertas NOT, XOR y AND

9

Urquía Alfonso, Martín Villalba Carla, Casos prácticos de diseño de circuitos digitales con VHDL,

Universidad Nacional de Educación a Distancia (UNED) Departamento de Informática y Automática, Madrid,

España: 2008

pág. 33

Bibliotecas

Una biblioteca en VHDL es un lugar en donde se guarda la

información relacionada con un diseño determinado. Al comienzo de cada

diseño el compilador crea automáticamente una biblioteca llamada WORK

con este objetivo. Además de esta biblioteca particular existen otras

bibliotecas de tipo general que contienen un conjunto de definiciones que

pueden utilizarse en cualquier diseño. Un ejemplo de biblioteca general es la

llamada Library IEEE, que contiene definiciones estándar para VHDL. Para

utilizar una biblioteca general es necesario escribir su nombre al inicio del

programa, por eso es muy común que en la primera línea de un diseño en

VHDL aparezca escrito "Library IEEE", de ésta forma dicha biblioteca se

hace visible para el diseño.

Paquetes

En los paquetes se guardan definiciones de tipos y objetos que

pueden ser utilizados en los diferentes diseños que invoquen su utilización.

Un

paquete

muy

utilizado

es

el

paquete

estándar

IEEE_STD_LOGIC_1164.ALL; La utilización de un paquete en un diseño se

realiza invocando su empleo mediante la cláusula USE y el nombre del

paquete. Por ejemplo USE IEEE_STD_LOGIC_1164.ALL;

La terminación ALL, permite utilizar todas las definiciones y objetos

que contiene dicho paquete. Además del estándar, existen otros paquetes de

utilización general y también los diseñadores que trabajan con VHDL pueden

definir sus propios paquetes, lo que les permite reutilizar diseños realizados

anteriormente como parte de nuevos diseños.

pág. 34

PROCEDIMIENTO Y DESCRIPCIÓN DE LAS

ACTIVIDADES REALIZADAS

Adquisición de la Tarjeta Basys2

La Tarjeta Basys2 y otros instrumentos fueron solicitados a la empresa

Digilent a través de su sitio web oficial www.digilentinc.com.

El catálogo completo de las tarjetas basadas en FPGA’s y CPLD’s se

encuentra en el siguiente vínculo:

http://www.digilentinc.com/Products/Catalog.cfm?NavPath=2,400&Cat=10&F

PGA

Cantidad

Producto

1

Basys2

Basys2 Spartan 3E FPGA Board

2

Multimete

r-MS821

PMOD-TMP

Autorange Digital Multimeter

1

Descripción

PMOD-TMP Thermometer

Precio

Unitario

$ 59.00

USD

$ 29.99

USD

$ 24.99

USD

Sub

Total

$ 59.00

USD

$ 59.98

USD

$ 24.99

USD

Tabla 3: Gastos en Digilent Inc

El envió desde USA se hizo a través del servicio de paquetería Fed-Ex

en un lapso de 3 días hábiles.

Cantidad

Producto

1

Envío

1

Impuesto

Descripción

Servicio de Paquetería FedEx

Impuesto Aduanal

Precio

Unitario

$ 81.77

USD

$ 30.00

USD

Sub

Total

$ 81.77

USD

$ 30.00

USD

Tabla 4: Gastos de Envio

Además se utilizaron componentes electrónicos pasivos y activos para

la implementación de las prácticas que implicaron un gasto extra en el

desarrollo del proyecto. Estos componentes fueron adquiridos en

distribuidores locales.

pág. 35

Cantidad

Producto

Descripción

Precio

Unitario

2

Protoboard

Tablilla para Prototipos

1

SN754410

Quadruple Half-H Driver

1

NE555

Multivibrador 555

30

Resistor

5

Capacitor

20

2N25

Resistores de distintos

valores

Capacitores Electrolíticos

y Cerámicos

Optoacoplador MOC

10

2N2222

NPN Transistor

1

Motor

Motro de 5V CD

2

Relay

Relays de 5V CD

3

Cable

Telefónico

Metros de Cable Telefónico

$ 9.00

USD

$ 2.99

USD

$ 0.95

USD

$ 0.10

USD

$ 0.30

USD

$ 0.80

USD

$ 0.23

USD

$ 1.00

USD

$ 1.00

USD

$ 0.88

USD

Sub

Total

$ 18.00

USD

$ 2.99

USD

$ 0.95

USD

$ 3.00

USD

$ 1.50

USD

$ 16.00

USD

$ 2.30

USD

$ 1.00

USD

$ 2.00

USD

$ 2.64

USD

Tabla 5: Gastos Extras

Por lo tanto el gasto total es de:

$

306.12 USD

Convertido a moneda nacional a una tasa de cambio de $ 13.43 MN el

gasto total es de:

$ 4111.18 MN

Descarga e Instalación de Software ISE Design Suite 13.4 y Adept

2.6.1 System

Xilinx ofrece una licencia gratuita de su entorno de desarrollo y diseño

para sus dispositivos reconfigurables, la versión gratuita se conoce como

Webpack, en últimas versiones no se trata de un software separado del

principal sino de una licencia de uso especial para el mismo, a continuación

se muestran los pasos necesarios para descargar el software y obtener la

licencia gratuita.

1- Ingresar y registrarse en el sitio web de Xilinx: www.xilinx.com. Al

ingresar al sitio, en el menú de la parte superior se tiene la opción

“Sign In”, que permite ingresar con una cuenta creada con

anterioridad o registrarse con una nueva mediante el enlace

“Create Account”.

pág. 36

Figura 12– Página Principal de Xilinx

Para el registro se deben proporcionar algunos datos personales tales

como nombre, dirección y correo electrónico.

2- Una vez registrados en el sitio, se puede acceder a la sección de

descargas, puede hacerse desde el enlace “Downloads” en la

parte superior del sitio. El software que nos interesa se llama ISE

Design Suite, en la página se puede seleccionar la versión a

descargar así como el sistema operativo con el cual trabajaremos:

hay tres opciones de descarga, instalador para Windows,

instalador para Linux o los binarios. La versión más reciente del

software y la utilizada en este documento es la 13.4.

3- La descarga no es directa, sino que al hacer clic en alguno de los

enlaces se instala el administrador de descargas de Xilinx, es

necesario permitir la ejecución del mismo, el cual permitirá pausar

y continuar la descarga de los archivos, algo bastante útil ya que el

software pesa 5.67 GB.

4- Una vez descargado el software, es necesario obtener una licencia

de uso, se utilizará la licencia Webpack que es gratuita, como se

ha expuesto anteriormente la principal diferencia con la versión de

pago es que soporta menos dispositivos, por lo tanto para el

desarrollo de proyectos de mayor volumen no será de utilidad. En

la misma página de descargas, a la derecha de los enlaces para

descargar ISE Design Suite se encuentra el enlace “License

Solution Center”

pág. 37

Figura 13– Sección de Descargas

5- Una vez adquirido el software ISE Design Suite y la Licencia,

procedemos a instalarlo; basta con seguir los sencillos pasos y

ubicar el directorio de la licencia. Para el uso de las tarjetas de

Digilent que cuentan con conector Mini-USB como lo son la Basys2

y Nexys2 se requiere un software extra para poder realizar la

comunicación: Adept de Digilent; El software puede descargarse

de manera gratuita en el sitio web de Digilent www.digilentinc.com ,

en la sección “Software”: Digilent Adept, el paquete a descargar

para Windows es Adept 2.6.1 System, 32/64-bit. Su instalación es

muy sencilla, basta con hacer doble clic en el icono del software

descargado y seguir las instrucciones.

Con esto se tiene instalado el software necesario para el uso de la

Tarjeta Basys2.

Uso del Software ISE Design Suite 13.4, Adept 2.6.1 System y

configuración de la Tarjeta Basys2

Para explicar el uso del software ISE Design Suite 13.4, Adept 2.6.1

System, la descarga y configuración de los programas hacia la Tarjeta

Basys2 así como las bases del lenguaje de programación VHDL, se

desarrollará una práctica sencilla que servirá de guía a través de la creación,

simulación y descarga del proyecto. Iniciaremos por compuertas lógicas

pág. 38

AND, OR y XOR, y estas mismas serán utilizadas para hacer un medio

sumador y a su vez un sumador completo. A continuación se muestran todos

los pasos que se realizarán:

Se inicia por abrir ISE Project Navigator. Al iniciar el programa, carga

automáticamente el último proyecto con el cual se trabajó. Se crea un nuevo

proyecto, para ello se selecciona el menú File y después New Project, con

esto se iniciará el asistente de creación de nuevo proyecto, en la primera

ventana que se muestra habrá que indicar el nombre del proyecto, la carpeta

de trabajo del proyecto (al introducir el nombre del proyecto se indicará

automáticamente una carpeta con el mismo nombre), una descripción del

proyecto (opcional) y en la parte inferior se tiene que indicar el tipo de archivo

fuente que será el módulo principal del proyecto, se deja en HDL.

Figura 14– Asistente de Creación de un nuevo Proyecto

A continuación se da clic en el botón Next, lo cual mostrará la ventana

Project Settings, donde se indica el modelo del dispositivo utilizado en el

proyecto, además de las herramientas a utilizar para las diferentes etapas del

diseño. Para el uso de la Tarjeta Basys2, las opciones necesarias son las

mostradas en la Figura 15.

pág. 39

Figura 15– Opciones de Configuración de Tarjeta Basys2

Una vez indicadas las opciones adecuadas, se hace clic en el botón

Next, se mostrará un resumen del proyecto, finalmente se da clic en el botón

Finish y se creará el proyecto nuevo, todavía sin ningún archivo fuente

agregado, solamente se verá el nombre del archivo de proyecto en la parte

superior y en la ventana Hierarchy dentro del panel Design el dispositivo

seleccionado.

Ahora se procede a agregar un nuevo archivo fuente al proyecto, esto

se realizará utilizando el menú Project => New Source…, con lo que

aparecerá una ventana donde se debe indicar el tipo de módulo que se

desea agregar al proyecto, se selecciona VHDL Module y como nombre del

programa compuerta_and. Es importante que esté seleccionada la opción

Add to Project. Observe la Figura 16.

pág. 40

Figura 16 – Ventana New Source Wizard

Después se da clic en el botón Next lo cual mostrará la ventana

Define Module, aquí se deben indicar las características del módulo; el

nombre de la entidad, el nombre de la arquitectura y las entradas y salidas

con las que contará. Se debe tener algo como lo mostrado en la Figura 17.

Figura 17 – Ventana Define Module

pág. 41

A continuación se da clic en el botón Next, con lo que se mostrará un

resumen del nuevo archivo fuente que se ha agregado al proyecto. Por

último se da clic en el botón Finish para que se agregue la nueva fuente al

proyecto, se abrirá la ventana del editor donde se cargará el contenido del

nuevo archivo compuerta_and.vhd (el nombre indicado para el nuevo

archivo fuente con la extensión .vhd que corresponde a un módulo VHDL)

Analice el código que se presenta al terminar de crear la nueva fuente

del proyecto; la primera sección que se aprecia con dos guiones al inicio, es

código predefinido que ISE Project Navigator inserta al inicio de cada módulo

que se agrega a un proyecto, se puede notar que todas las líneas en esta

primera sección inician con un par de guiones “–”: al igual que en los

lenguajes de programación de software, VHDL permite insertar comentarios

en el código, los cuales se indican mediante esos dos guiones, todo el texto

que siga a estos guiones se toma como un comentario.

---------------------------------------------------------------------------------- Company:

-- Engineer:

--- Create Date:

15:11:22 05/10/2012

-- Design Name:

-- Module Name:

compuerta_and - Behavioral

-- Project Name:

-- Target Devices:

-- Tool versions:

-- Description:

--- Dependencies:

--- Revision:

-- Revision 0.01 - File Created

-- Additional Comments:

---------------------------------------------------------------------------------Código 1 – Código Predefinido por ISE Project Navigator

Mas adelante se tiene el siguiente código:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

Código 2– Librerías utilizadas en el programa

La instrucción library permite indicar una biblioteca externa de la cual

se desee utilizar sus tipos de datos, operadores y algunas otras

declaraciones; sería equiparable a la instrucción #include de los lenguajes C

pág. 42

y C++. De manera similar a estos lenguajes, VHDL termina cada instrucción

con punto y coma: “;”.

Después se tiene una instrucción use, que permite indicar qué

paquete se va a utilizar de la biblioteca que antes se había declarado con

library. En este caso, se indica que se va a hacer uso de la biblioteca IEEE,

que es una biblioteca estándar definida por el Institute of Electrical and

Electronics Engineers, seguido de use se tiene STD_LOGIC_1164 lo cual

hace referencia al paquete de la biblioteca que se utilizará y por ultimo se

indica que de ese paquete se utilizaran todas sus declaraciones por medio

de la instrucción ALL.

Cabe mencionar que VHDL es un lenguaje que no distingue

minúsculas de mayúsculas.

Entidad y Arquitectura

En VHDL, cada módulo está compuesto por dos partes: la entidad y la

arquitectura. La entidad es la sección donde se indican las conexiones

(señales) del módulo con el resto de componentes, se indican el número de

entradas y salidas, además del tipo de cada una de ellas. La sintaxis de

declaración de entidad y de sus conexiones es la siguiente:

entity NOMBRE_ENTIDAD is

port (

NOMBRE_SEÑAL1 : MODO TIPO;

NOMBRE_SEÑAL2 : MODO TIPO

);

end NOMBRE_ENTIDAD;

Código 3– Sintaxis de la Entidad

En primer lugar se indica el nombre de la entidad, utilizando la palabra

reservada entity, y después de la instrucción is se inicia la descripción de la

entidad, en este caso de las señales o puertos mediante los cuales se

comunicará con el exterior; para cada señal se indica su nombre, el modo

(entrada, salida o ambos) y el tipo. Notese que las declaraciones de puertos

finalizan con punto y coma, excepto la última antes del paréntesis que

culmina la instrucción port.

Por lo tanto, continuando con el módulo, ISE Project Navigator ha

insertado el código mostrado en el recuadro de código 4:

entity compuerta_and is

Port ( a : in STD_LOGIC;

b : in STD_LOGIC;

pág. 43

s : out

end compuerta_and;

STD_LOGIC);

Código 4 – Entidad Compuerta_and

La entidad cuyo nombre es compuerta_and, tiene tres puertos, todos

de tipo std_logic, los dos primeros denominados a y b, son entradas (in),

mientras que el tercero, denominado s, es una salida (out), el diagrama

esquemático de la entidad creada se puede representar de la siguiente

manera:

Figura 18 – Diagrama esquemático compuerta_and

De cierta forma, se considera la declaración de la entidad como una

“caja negra”, para la cual se conocen sus entradas y salidas, pero no su

funcionamiento interno, el cual se describe en la arquitectura.

La arquitectura es la sección de un módulo VHDL en la que se

describe el funcionamiento de la entidad, y puede hacerse de dos maneras

diferentes: describiendo su estructura interna mediante interconexiones entre

compuertas y componentes que constituyen al módulo, lo que se denomina

una descripción estructural, o con una descripción de lo que hace el módulo,

ya sea mediante funciones booleanas o mediante una descripción

algorítmica, lo que se conoce como una descripción de comportamiento. La

sintaxis para declarar una arquitectura es mostrada en el recuadro de código

5.

architecture NOMBRE_ARQUITECTURA of NOMBRE_ENTIDAD is

-- Aquí se declaran elementos auxiliares para usar en la descripción

begin

-- Aquí se realiza la descripción de la arquitectura,

-- mediante la utilización de sentencias secuenciales,

pág. 44

-- combinacionales o subprogramas.

end NOMBRE_ARQUITECTURA;

Código 5– Sintaxis de la Arquitectura

Como se puede observar se utiliza la instrucción architecture para

iniciar la declaración de la arquitectura, después se indica su nombre y el

nombre de la entidad a la cual corresponde la descripción que se realizará,

se continua con la instrucción begin para indicar el inicio del código que

describe el funcionamiento de la arquitectura, y finaliza con la instrucción end

seguido del nombre de la arquitectura. Entre las instrucciones is y begin, es

posible declarar señales, componentes o elementos auxiliares para la

descripción de la arquitectura, algunos de estos elementos se verán más

adelante.

ISE Project Navigator nos crea la plantilla de la arquitectura, para que

el programa compuerta_and funcione se debe describir su comportamiento;

para lo cual se agrega después de la instrucción begin lo que se desea que

haga el programa. El resultado se muestra en el recuadro de código 6.

architecture behavioral of compuerta_and is

begin

s <= a and b;

end behavioral;

Código 6– Arquitectura compuerta_and

Con esto, se asigna el resultado de la operación and entre las señales

de entrada a y b a la señal de salida s. Como se observa, la pareja de

caracteres “<=" son el operador de asignación de señales en VHDL, también,

se hace uso del operador and, que realiza la operación lógica AND entre sus

dos operandos. Además del operador and, en VHDL se tienen definidos los

siguientes operadores lógicos: or, nand, nor, xor y xnor. Finalmente, se

termina la instrucción con un punto y coma.

Una vez que se ha adicionado este código al módulo, se procede a

guardar los cambios realizados usando el comando Save dentro del menú

File o pulsando en el botón con icono de un disco flexible en la barra de

herramientas. Para comprobar que no se han cometido errores en el código

del módulo, se debe realizar una revisión de sintaxis, para ello, en la ventana

Hierarchy, se da clic en el nombre del módulo (compuerta_and), después,

en la ventana Processes, se expande la sección Synthesize – XST, de

manera que se pueda ver el proceso Check Syntax tal y como se muestra

en la figura 19.

pág. 45

Figura 19– Revisión de Sintaxis

Para iniciar la revisión de sitanxis del código, se hace doble clic sobre

el nombre del proceso o con un clic derecho y luego seleccionando el

comando Run del menú contextual. Se puede observar el resultado del

proceso de revisión de sintaxis en la parte inferior del programa en la

ventana de resultados.

Figura 20– Resultado del Chequeo de Sintaxis

Al terminar el proceso, un icono con una palomita blanca indica que la

revisión de sintaxis ha concluido exitosamente pues no se encontraron

errores en el código.

pág. 46

Con esto se ha revisado el código del módulo, resta comprobar que

funcione correctamente, para ello se puede realizar una simulación antes de

proceder a la implementación en un dispositivo reconfigurable.

Simulación

Analicemos cómo realizar una simulación del componente

compuerta_and. En primer lugar, dentro de Project Navigator, en la sección

Design, en la opción View, se selecciona Simulation:

Figura 21 – Simulación

A continuación, dentro de la ventana Hierarchy, se selecciona el

componente que se desea simular, al hacerlo cambiarán las opciones

disponibles en la ventana Processes, en este caso se muestra ISim

Simulator, se da clic en el signo “+” a la izquierda de ISim Simulator con lo

que se mostrarán dos procesos: Behavioral Check Syntax y Simulate

Behavioral Model

pág. 47

Figura 22– Ventana Processes ISim Simulator

Este último proceso es el que permitirá realizar la simulación, se hace

doble clic en Simulate Behavioral Model y se espera a que inicie ISim.

Figura 23– Ventana ISim Simulator

ISim muestra por defecto cuatro ventanas o secciones, una en la parte

inferior y tres en el medio: Instances and Processes, muestra las entidades,

bibliotecas y procesos existentes en el módulo; Objects, despliega una lista

de los puertos que forman parte del módulo, indicando con un pequeño icono

con la letra I aquellos que son entradas y con la letra O los que son salidas; y

la ventana de simulación, donde se despliegan nuevamente los puertos del

pág. 48

módulo con líneas de tiempo que permitirán visualizar el comportamiento de

cada uno de dichos puertos para cada instante de la simulación.

La tabla de verdad de una compuerta AND de dos entradas se

muestra en la Tabla 6.

b

a

s

0

0

1

1

0

1

0

1

0

0

0

1

Tabla 6 – Tabla de verdad compuerta AND

Se tienen cuatro combinaciones posibles de valores para las entradas

a y b, para comprobar el funcionamiento del módulo es conveniente simular

estos cuatro casos; para ello, se asignan valores a las entradas de manera

que se tengan las cuatro combinaciones posibles y se pueda evaluar el valor

que toma la salida para cada una de ellas.

Se inicia por la primera combinación, cuando ambas entradas valen 0,

para indicar que una entrada tendrá el valor 0 en el simulador, se da clic con

el botón derecho del ratón sobre dicha entrada en la ventana de simulación,

del menú que se despliega se selecciona la opción Force Constant…

Aparecerá la ventana Force Selected Signal; en la opción Force to

Value: escribiremos un 0 como se muestra en la Figura 24. Se hace clic en el

botón OK.

Se repiten estos pasos para la señal de entrada b: se hace clic con el

botón derecho sobre el nombre de la entrada en la ventana de simulación, se

selecciona la opción Force Constant…, y se establece a 0 la opción Force

to Valué: se da clic en el botón OK.

Al hacer esto no se nota ningún cambio en la ventana de simulación

una vez que se han indicado los valores de 0 para las dos señales, estos se

notarán hasta que se ejecute la simulación. Para ello se hará uso de la barra

de herramientas de ISim.

pág. 49

Figura 24 – Ventana Force Selected Signal

Se da clic en el botón que tiene como icono una punta de flecha y un

reloj de arena, esto ejecuta la simulación por un tiempo determinado, el cual

se indica a la derecha del botón; en este caso, 1 us, la ventana de simulación

ahora muestra lo que se observa en la figura 25.

Figura 25 – Resultado Simulación Valor 1

Como se puede observar, los valores en la columna Value han

cambiado de U a 0, la U indica valor desconocido, que era el caso antes de

iniciar la simulación, ahora que se ha simulado por un tiempo de 1us, las

entradas se encuentran en valores de 0, que fue como se “forzó”, además la

señal de salida s también tiene el valor de 0, esta no se forzó, sino que toma

el valor especificado en el módulo: la operación AND entre las

entradas a y b, que en este caso es 0.

Ahora, cambie el valor de la entrada a por 1, para evaluar el segundo

caso de la tabla de verdad de la operación AND de dos entradas, se hace

clic con el botón derecho sobre el nombre de la señal y se selecciona el

comando Force Constant nuevamente; en esta ocasión se establecerá un 1

en la opción Force to value. Se hace clic en el botón para ejecutar la