Prácticas 1-2-3

Anuncio

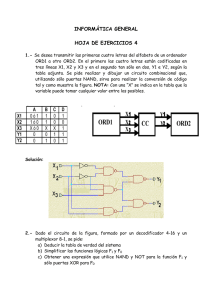

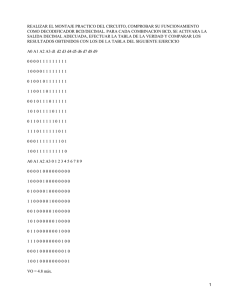

PRACTICAS DE LABORATORIO ELECTRONICA DIGITAL / SISTEMAS DIGITALES Practica nº 1 - curso 2008 / 09 DISEÑO DE FUNCIONES LÓGICAS SENCILLAS OBJETIVO.El objetivo de esta práctica es el diseño de funciones lógicas sencillas a partir de las especificaciones iniciales, siguiendo los pasos del diseño de los circuitos combinacionales. En nuestro caso, se implementarán las siguientes funciones de la forma más sencilla posible, utilizando puertas lógicas de dos entradas e inversores. a) La función Pi (X, Y, Z) que corresponde a un generador de paridad impar para un mensaje de 3 bits. b) La función F(A, B, C, D) = Σ4 (0,1,2,3,5,6,9,10) Para ello se deberá: • Obtener la tabla de verdad de dichas funciones. • Simplificarlas mediante mapas de Karnaugh. • Simular el resultado anterior en EWB (Electronic WorkBench). • Implementar sus diagramas lógicos resultantes con el menor número de puertas posible. Para ello es muy importante tener en cuenta que todos los circuitos integrados que se utilizan tienen dos entradas de alimentación, que se deben conectar adecuadamente (+Vcc y GND). • Realizar las pruebas de funcionamiento adecuadas. • Obtener la función lógica que permite implementarla mediante puertas NAND exclusivamente y simularla mediante el EWB. Observación: Como habrá podido observar, parte del trabajo de la práctica puede ser desarrollada en casa, dejando para el día fijado de laboratorio, la implementación física del circuito. Se aconseja seguir este modo de funcionamiento y venir al laboratorio con la práctica pensada, diseñada y simulada, de lo contrario puede que no os de tiempo a terminar la práctica, con lo que eso puede implicar en el resultado final de la asignatura. MEMORIA.La memoria deberá contener todos los cálculos realizados explicados detalladamente, así como todos los esquemas de los montajes realizados con un listado de los componentes físicos utilizados y el fichero(s) de simulación obtenido en EWB. DEPARTAMENTO DE INGENIERIA INDUSTRIAL DEPARTAMENTO DE INGENIERÍA INFORMATICA PROFESOR: Luis García Cervantes Pág. 1 / 3 PRACTICAS DE LABORATORIO ELECTRONICA DIGITAL / SISTEMAS DIGITALES Práctica nº 2 - curso 2008 / 09 DISEÑO DE FUNCIONES LÓGICAS SENCILLAS MEDIANTE EL USO DE MULTIPLEXORES Y CODIFICADORES OBJETIVO.El objetivo de esta práctica es el diseño de un comparador de palabras de dos bits. Las entradas serán A1, A0 y B1, B0 respectivamente para cada una de las palabras, mientras que las salidas son L (A < B), E (A = B), G (A > B). Se pide: • La tabla de verdad de dicho sistema. • Expresión de las funciones L, E y G como suma de minitérminos en las formas abreviadas ( Σ (…) ). • Implementar L y G con un MUX 8:1 y las puertas lógicas necesarias, previa simulación mediante EWB. • Implementar E con DEC 4:16 y las puertas lógicas de 2 entradas necesarias, previa simulación mediante EWB. • ¿ Se podría realizar el diseño de alguna otra forma más sencilla ? Razonar la respuesta. Observación: Como habrá podido observar, parte del trabajo de la práctica puede ser desarrollada en casa, dejando para el día fijado de laboratorio, la implementación física del circuito. Se aconseja seguir este modo de funcionamiento y venir al laboratorio con la práctica pensada, diseñada y simulada, de lo contrario puede que no os de tiempo a terminar la práctica, con lo que eso puede implicar en el resultado final de la asignatura. MEMORIA.La memoria deberá contener todos los cálculos realizados explicados detalladamente, así como todos los esquemas de los montajes realizados con un listado de los componentes físicos utilizados y el fichero(s) de simulación obtenido en EWB. DEPARTAMENTO DE INGENIERIA INDUSTRIAL DEPARTAMENTO DE INGENIERÍA INFORMATICA PROFESOR: Luis García Cervantes Pág. 2 / 3 PRACTICAS DE LABORATORIO ELECTRONICA DIGITAL / SISTEMAS DIGITALES Práctica nº 3 - curso 2008 / 09 DISEÑO DE UN CONVERTIDOR DE CÓDIGO REVERSIBLE OBJETIVO.Algunos de los sistemas digitales combinacionales más comunes son aquellos que realizan operaciones aritméticas (sumas, restas, etc.) y lógicas (AND, OR, etc.). Un sumador total de 1 bit es capaz de sumar dos bits de idéntico peso con el acarreo que proviene de una etapa anterior. El objetivo de esta práctica es el diseño de un convertidor de código reversible, utilizando para ello un sumador total de 4 bits y las puertas lógicas de dos entradas necesarias. El convertidor de código reversible será de código BCD natural a BCD exceso a 3, utilizando una señal de control adicional (C), de tal forma que: • Si C = 0 se realizará la conversión de BCD natural a BCD exceso 3. • Si C = 1 se realizará la conversión de BCD exceso 3 a BCD natural. El código de entrada (A) vendrá representado por A3, A2, A1 y A0, mientras que el código de salida (S) vendrá representado por S3, S2, S1 y S0. Se pide: a) Obtener la tabla de verdad que relaciona las entradas con las salidas, para cada uno de los casos anteriores ( C = 0 / C = 1) y determinar la corrección (B = S – A) que vendrá expresada por B3, B2, B1 y B0 en función de las señales A y C. b) Simular (EWB) el circuito resultante. c) Implementar el circuito resultante utilizando un sumador total de 4 bits y las puertas lógicas de dos entradas necesarias. d) El sistema necesario para visualizar la señal S en un display de 7 segmentos, empleando un decodificador BCD a 7 segmentos. Observación: Como habrá podido observar, parte del trabajo de la práctica puede ser desarrollada en casa, dejando para el día fijado de laboratorio, la implementación física del circuito. Se aconseja seguir este modo de funcionamiento y venir al laboratorio con la práctica pensada, diseñada y simulada, de lo contrario puede que no os de tiempo a terminar la práctica, con lo que eso puede implicar en el resultado final de la asignatura. MEMORIA.La memoria deberá contener todos los cálculos realizados explicados detalladamente, así como todos los esquemas de los montajes realizados con un listado de los componentes físicos utilizados y el fichero(s) de simulación obtenido en EWB. DEPARTAMENTO DE INGENIERIA INDUSTRIAL DEPARTAMENTO DE INGENIERÍA INFORMATICA PROFESOR: Luis García Cervantes Pág. 3 / 3