Flip-flops ópticos - RiuNet repositorio UPV

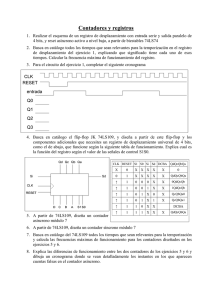

Anuncio