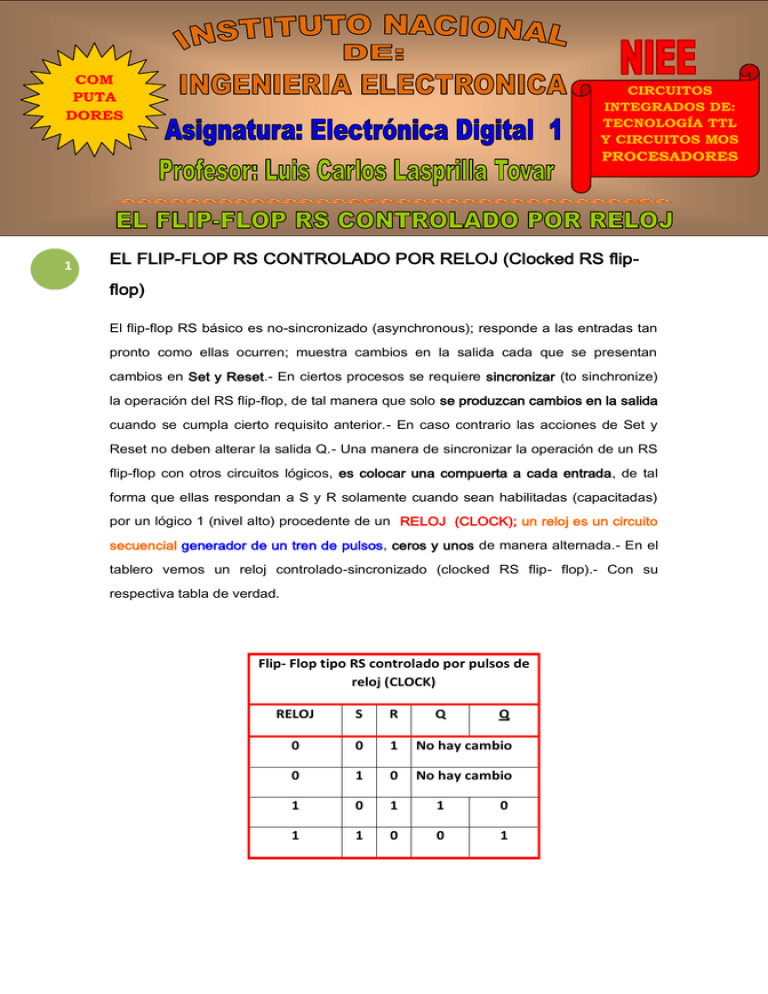

el flip-flop rs controlado por reloj

Anuncio

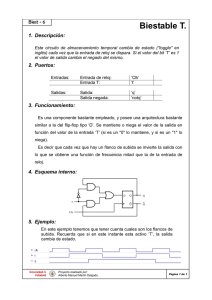

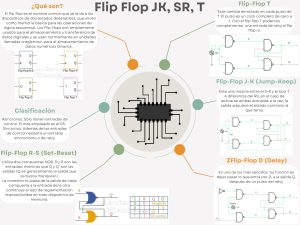

COM PUTA DORES CIRCUITOS INTEGRADOS DE: TECNOLOGÍA TTL Y CIRCUITOS MOS PROCESADORES 1 EL FLIP-FLOP RS CONTROLADO POR RELOJ (Clocked RS flipflop) El flip-flop RS básico es no-sincronizado (asynchronous); responde a las entradas tan pronto como ellas ocurren; muestra cambios en la salida cada que se presentan cambios en Set y Reset.- En ciertos procesos se requiere sincronizar (to sinchronize) la operación del RS flip-flop, de tal manera que solo se produzcan cambios en la salida cuando se cumpla cierto requisito anterior.- En caso contrario las acciones de Set y Reset no deben alterar la salida Q.- Una manera de sincronizar la operación de un RS flip-flop con otros circuitos lógicos, es colocar una compuerta a cada entrada, de tal forma que ellas respondan a S y R solamente cuando sean habilitadas (capacitadas) por un lógico 1 (nivel alto) procedente de un RELOJ (CLOCK); un reloj es un circuito secuencial generador de un tren de pulsos, ceros y unos de manera alternada.- En el tablero vemos un reloj controlado-sincronizado (clocked RS flip- flop).- Con su respectiva tabla de verdad. Flip- Flop tipo RS controlado por pulsos de reloj (CLOCK) RELOJ S R Q Q 0 0 1 No hay cambio 0 1 0 No hay cambio 1 0 1 1 0 1 1 0 0 1 S Q CLOCK 2 Q R Un componente o circuito integrado Clocked R-S sincronizado o controlado por reloj. Flip-Flop.- Es un circuito VISTA DEL DIAGRAMA ESQUEMATICO DE UN PROTOBOARD 3 VISTA DEL COBRE PERFORADO PARA ENSAMBLAJE DE LOS COMPONENTES ELECTRONICOS.