departamento de ingeniería electrónica estudio, diseño e

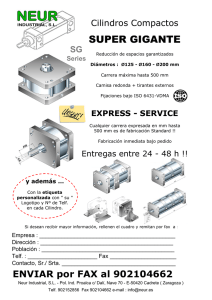

Anuncio