1 - Cenidet

Anuncio

S.E.P.

S.E.I.T.

.

D.G.I.T.

CENTRO NACIONAL DE INVESTIGACI~N

Y DESARROLLO TECNOL6GICQ

18

I

’,

i

cenidet

“SISTEMA DIGITAL DE PROCESAMIENTO CONCURRENTE

ORIENTADO A APLICACIONES EN TIEMPO REAL”

1

I

1

TESIS

PARA OBTENER EL GRADO DE

MAESTRO EN CIENCIAS EN

INGENIERIA

ELECTRONICA

P R E S E N T A:

I’

1/

SISTEMA NACIONAL DE INSTITUTOS TECNOLÓGICOS

Centro Nacional de Investigación y Desarrollo Tecnológico

Cuernavaca, Moreloc a 31 de julio de 1998

Ing. Javier Reyes Sánchez

Candidato al grado de Maestro en Ciencias

en Ingeniería Electronica

Presente

Despues de haber sometido a revision su trabajo final de tesis titulado: “SISTEMA DIGITAL

DE PROCESAMIENTO CONCURRENTE ORIENTADO A APLICACIONES EN TIEMPO

REAL”, y habiendo cumplido con todas las indicaciones que el jurado revisor de tesis le hizo,

le comunico que se le concede autorización para que proceda a la impresión de la misma.

como requisito para la obtención del grado.

Reciba un cordial saludo

/

C.C.P.: Ing. Jaime Rosas ÁIvaredJefe de Servicios Escolares

Expediente

dinwarism

Institutos Tecnológicos

50 años de educación superin: lecnc.

‘Ógica en México

_- .

APARTADO POSTAL 5-164. CP 62051. CUERNAVACA. MOR. MEXICO. TELS. (73’

EMAIL Cenidell @infosei.nei.mr

7 6 1 3 . Fr

I:

(73)i z 2434 -

li

I

S.E.1.T

S.E.P.

S.N.1 T

I

-

CENTRO NACIONAL DE INVESTIGACION Y DESARROLLO TECNOLOGICO

1

cenidel

ACADEMIA DE LA MAESTRIA

8

EN E L E C T R ~ N I C A

1

FORMAR11

ACEPTACION DEL TRABAJO DE TESIS

I

I

Dr. Juan Manuel Ricaño Castillo

Director del cenidet

Presente

1

f

Cuernavaca. Mor. a 3 1 de julio de 1998

At’n. Dr. Jaime E. Arau Roffiel

Jefe del Depto. de Electrónica

I

1

i

I

Después de haber revisado el trabajo, de tesis titulado: “Sistema digital de procesamiento

concurrente orientado a aplicaciones.en

I tiempo real”, elaborado por el alumno Javier Reyes

Sánchez. bajo la dirección del M.C., José Martin Gómez López, el trabajo presentado se

ACEPTA para proceder a su impresión.;

ATENTAMENTE

,

C.C.P.:

I

I

Javier Meneses Ruíz

M.C. Javier Meneses Ruíz/ Pdte, de la Academia de Electrónica

I

Ing. Jaime Rosas Álvarez / Jefe,del

Depto. de Servicios Escolares

Expediente.

!

i

I

!

cenidet/

Interior Internado Palmira SR.I C.1’. 62490

Apanado Postal 5.164. C,P. 62050. Cuernavaca Mor.. Mexico

Tels. (73) 18-77-41 ! 12-76-13. Fav. 12-24-34

~

I

Dedico mi trabajo y mi esfuerzo

I;

~

I

A Dios y a Dios en el Hombre

A mipadre José Carmelo Reyes Franco

A mi madre Catalina Sánchez Muñiz

Graciaspor darme la oportunidad y creer en mi

~

1

I

¡I

1

Agradecimientos:

Agradezco a mi familia por todo el apoyo que me han brindado a lo largo de todos

estos años. A mis padres. A mis hermanos: Miguel, Arturo, Lucha, Daniel, Lety, Chayo,

Silvia y a los agregados y agregadas culturales. En especial a Lety por su apoyo al inicio de

m i s estudios.

Agradezco a la Secretaría de Educación Pública (SEP), al Consejo Nacional de

Ciencia y Tecnología (CONACYT) y al Centro Nacional de Investigación y Desarrollo

Tecnológico (CENIDET), por el apoyo recibido para la realización de mis estudios.

Ai M.C. José Martin Gómez López por su asesoría y por su esfuerzo para la

realización de este trabajo.

A los profesores: M.I. Hugo Calleja, M.C. Carlos Ramírez y M.C. Javier Meneses,

por sus aportaciones realizadas.

A mis compañeros del depa: Aido, Nacho y Rafa, gracias por saber ser los mejores

amigos.

A mis amigos y compañeros de generación: Adriana “ACTA’ A., Leobardo C.,

Jaime O., Enrique R., David A. y Liliana T.

A la señora Maria Elena, Mario Moreno, Alfred0 Gonzalez y Mayra Correa por su

apoyo y su amistad mostrada a lo largo de este tiempo.

Ai Dr. Sergio A. Horta Mejía por haber gestado la idea original de esta tesis

A mis amigos: Claudia Ibarra, Sandra Aguilar, Ricardo Carrillo, Javier h a , Julio C.

Sosa, Alberto Rueda, Andrea Magadán, Alfonso May, Edson Peralta, Boris, Angel, Alex e

Hilmara, Huante. A todos los que he olvidado mencionar les debo una disculpa, pero no

bastan unas cuantas líneas para manifestar todo el agradecimiento que siento en este

momento.

Y para cerrar con broche de oro quiero agradecer a una persona muy especial, que

con sus atenciones, cariño, dedicación, comprensión y apoyo, se ha convertido en una parte

muy importante de mi vida:

Ldí: Gracias.

Te amo.

,

1/

l.

1;

,,

li

Tabla de contenido.

Tabla de figuras.

VI

j

'i

I!

11

Introducción.

vm

Antecedentes.

Objetivo.

¡I

"

i:

',

M

X

Metas de diseño.

Contenido.

Capítulo 1. Sistemas de procesamiento concurrente.

1.1 Generalidades.

1.1

1.2 Software operativo.

1.1

1.2.1 Sistemas de tiempo real.

1.2

1.2.2 Sistemas concurrentes.

1.2

1.3

1.3 Núcleo del sistema operativo.

Ij

I

I

II

,I

I!

!

I\

I!

I1

I!

IjI

1.3.1 Elementos del sistema operativo.

1.3

1:

1.3.2 Procesos.

1.5

1!

1.4 Gestión de procesos.

1.5

I!

1.5 Comunicación y sincronización entre procesos.

1.6

1.6 Manejo de los elementos de hardware.

1.6

\

I!

I

1.7 Manejo de interrupciones.

1.8 Aplicaciones de control en tiempo real.

'I

Capítulo 2. Descripción del sistema.

2.1 Introducción.

I/

i

1:

2.2 Descripción del sistema.

2.1

2.1

2.3 Módulo de procesamiento concurrente.

2.2

/i

2.3.1 Descripción funcional del módulo de procesamiento.

2.3

I!

2.3.2 Consideraciones del módulo de procesamiento.

2.4

2.3.3 Descripción general del hardware.

2.4

2.3.4 Descripción general del software.

2.5

2.3.4.1 Software operativo.

2.6

2.3.4.2 Software de aplicación.

2.7

I

I

,/

ij

I1

,

!'

2.3.5 Características del módulo de procesamiento.

2.4 Descripción de los procesos físicos controlados.

2.4.1 Periodo de muestreo.

I

2.7

'I

2.8

I'

1,

2.8

1;

1'

2.9

2.4.2 Simulación de los procesos.

Capítulo 3. Desarrollo del hardware.

3.1 Introducción.

j

II

3.1

I!

II

3.2 Diseño del módulo de procesamiento.

3.1

3.2.1 Submódulo de procesamiento.

3.1

3.2.2 Submódulo de memoria.

3.2

3.2.3 Lnterfaz de entradashalidas analógicas.

3.3

3.2.4 Interfaz local.

3.4

,I

3.2.5 Interfaz serie.

3.5

I1

3.2.6 Interfaz E/S digitales.

3.5

3.2.7 Generadores de PWM.

3.6

3.2.8 Fuentes de alimentación.

3.1

'1

3.7

11

3.3 Mapa de memoria.

3.3.1 Direccionamiento de los submódulos.

1

lj

'I

I

li1

I,

I;

3.8

,

I!

3.9

3.4 Diagrama eléctrico del circuito.

!j

Capítulo 4. Desarrollo del software.

/I

4.1 Organización del software.

4.1

4.2 Desarrollo del software operativo.

4.1

.

,

'1

'/

4.2 'i

4.2.1 Núcleo del software operativo.

1,

4.2

4.3 Inicialización del sistema.

li

4.2 ,I

4.4 Gestión de procesos.

4.4.1 Elementos del software.

4.3

4.4.2 Elementos en la gestión de procesos.

4.3

4.4.3 Planificador.

4.3

4.4.4 Manejo de las colas de procesos.

4.6

4.4.5 Contexto de los procesos.

4.6

4.4.5.1 Salvar contexto.

4.6

4.4.5.2 Cargar contexto.

4.1

I1

11

lj

I

~

I

4.7

4.4.5.3 Restablece contexto.

4.7

4.4.6 Pila de los procesos.

4.5 Sincronización y comunicación entre procesos.

4.6 Gestión de interrupciones.

4.6.1 Descripción de las interrupciones usadas.

4.7 Manejo del hardware.

4.8

4.8

4.8

4.9

4.9

4.7.1 Memoria.

4.10

4.7.2. Manejo del procesador.

4.10

4.7.3 Manejo del timer.

4.10

4.7.4 Pantalla de cristal liquido.

4.11

4.7.5 Interfaces de EIS analógicas.

4.11

4.8 Software de aplicación.

4.8.1 Descripción de las tareas de aplicación.

4.11

4.8.2 Control de los procesos físicos.

4.12

4.8.2.1 Descripción de los módulos de control de los procesos físicos.

4.12

4.13

4.8.3 Interfaz al usuario.

4.8.3.1 Diagnóstico del hardware del controlador.

4.14

4.8.3.2 Opciones de los procesos.

4.15 I!

4.8.3.3 Despliegue de variables.

4.15

11

4.8.4 Interfaz de comunicación serial.

4.16

I!

4.8.5 Operaciones aritméticas de punto flotante.

4.16

11

'I

4.8.5.1 Adición y substracción.

4.17 I/

4.8.5.2 Multiplicación.

4.18 'i

4.9 Herramientas de generación de código.

4.9.1 Generación del código ejecutable.

4.10 Alta de los procesos de software de usuario.

I(

I

4.18

!I

4.18 j

II

4.19:I:

Capítulo 5. Pruebas y Resultados.

5.1 Introducción.

5.11

5.2 Pruebas de diseño del hardware.

5.2

5.3 Pruebas del software operativo.

5.3

5.3.1 Pruebas de gestión de procesos.

5.4

5.3.2 Pruebas de sincronización y comunicación.

5.5

1:

I

I11

I

!i

5.3.3 Pruebas de manejo de interrupciones.

5.4 Pruebas funcionales.

5.4.1 Pruebas a los procesos controlados.

5.4.2 Pruebas de los algoritmos de control PID.

5.4.3 Pruebas del sistema de control.

Capítulo 6. Desarrollo de procesos de usuario.

5.7

I!

/I

5.8

I/

5.8

,'

5.10

11

5.10

;i

I

I¡

I

I;

6.1

)I

6.2 Elementos requeridos en el sistema.

6.1

,;

6.3 Descripción del archivo TESIS.ASM.

6.1

6.2

1,

/i

6.1 Introducción

6.4 Procesos de software de usuario.

i

//

6.4.1 Limitantes en los procesos de usuario.

6.3

6.4.2 Manejo de buzones y semáforos y memoria disponible al usuario.

6.4

j

1

,/

'i

6.4

6.5 Rutinas de aplicación general.

6.5.1 Rutinas de manejo de la pantalla LCD.

I;

6.4

6.5.1.1 Rutina despliega cadena.

6.4 1;

6.5.1.2 Despliega carácter, ejecuta comando y limpia pantalla.

6.5 )

6.5.2 Rutinas de comunicación serie.

6.5

6.5.3 Retardos.

6.6 '1

6.5.4 Transferencias de bloques de memoria.

6.6

6.5.5 Rutinas de operaciones aritméticas.

6.7

'I

Ii

'

II

6.5.5.1 Conversión de entero a punto flotante.

6.1

6.5.5.2 Conversión de punto flotante a entero.

6.1

6.5.6 Otras rutinas.

;j

/

11

6.7

6.6 Ejemplos de procesos de software a nivel de usuario.

6.6.1 Algoritmos de control PID.

6.8 li

I!

6.8

6.6.2 Manejo de la interfaz local.

6.9 I

1;

6.7 Alta de un proceso de software de usuario.

!I

6.9!I

Capítulo 7. Conclusiones.

Hardware

7.1

Software

7.2

Problemática.

7.3

I!

N

I

1.3

Aspectos de operación

~

1.4

Aportación.

7.5

Trabajos futuros.

Apéndice A. Descripción de conectores.

A.l. Conector J1 Control del AEF4752

A.2. Conector 52 EntradaslSalidas digitales

A.3. Conector 53 Canal Serie

I,

I¡

A.l

1;

I

A.l

lj

A.l

I

A.4. Conector 54 Teclado

A.5. Conector J 5 Pantalla LCD

A.6. Conector JS Control de convertidores.

A.7 Conector J 9 Salidasmntradas Analógicas

A.2

I;

A.2

/j

11

Apéndice B. Descripción de componentes.

I!

B.l Lista de componentes utilizados.

B.1

B.2 Microcontrolador DSSOC310.

B.2 /j

B.3 Memoria RAM no volátil DS1225Y.

B.3

B.4 Convertidor AnalógicoíDigital MAX182.

B.4

B.5 Convertidor Digital/Analógico MAX527.

B.5

B.6 Generador PWM HEF4752.

B.6

:I

I

'1

I'

!

/j

I'

,I

B.7 Amplificador operacional OP490.

4

B.7 /j

B.8 Pantalla de cristal líquido AND491.

B.8 '1

I!

Apéndice C. Referencias.

I/

C.l Referencias bibliográficas.

c.1I!

C.2. Referencias técnicas.

c.3'!

c.3'j

C.3. Referencias en internet.

I,<

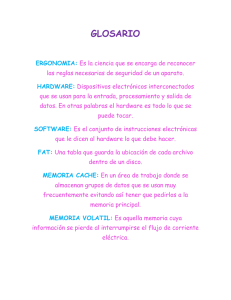

Apéndice D. Glosario.

D.l Definiciones y abreviaturas.

D.l

V

Tabla de figuras.

Figura 1.1 Estructura básica de un sistema operativo.

s roce so s.

1.5

i;

Figura 2.1 Diagrama a bloques del Sistema.

2.1

il

Figura 2.2 Conformación del módulo de control

2.2

1,

Figura 2.3 Diagrama a bloques del módulo de procesamiento.

2.4

Figura 2.4 Esquema general del software.

2.6

Figura 2.5 Respuesta al escalón de los procesos controlados.

2.9

Figura 1.2 Estados de 10s

'1

1;

,,

!I

,j

Figura 2.6 Diagrama de los procesos físicos controlados.

2.10

/j

Figura 2.7 Diagrama de flujo de los procesos físicos.

2.11

Ir

Figura 3.1 Hardware del módulo de procesamiento.

3.1

ii

Figura 3.2 Submódulo de procesamiento y control.

3.2

lj

Figura 3.3 Submódulo de memoria.

Figura 3.4 Interfaz de E/S analógicas.

3.3

3.3

Figura 3.5 Interfaz local.

3.4 1

Figura 3.6 Conexión de teclado.

3.5

Figura 3.7 Diagrama de la interfaz serie.

Figura 3.8 Interfaz de E/S digitales.

3.5 Ij

3.6 1

Figura 3.9 Diagrama a bloques de los generadores de PWM.

3.7 /j

Figura 3.10 Fuente de alimentación del módulo.

3.7 I¡

Figura 3.11 Espacio de memoria externa.

3.8'1

Figura 3.12 Direccionamiento de los submódulos.

3.9'!

Figura 4.1. Relación entre los niveles de software.

4.1

Figura 4.2. Inicialización del sistema.

4.2

Figura 4.3. Política de multinivel de colas.

Figura 4.4. Planificador de asignación cíclica.

Figura 4.5. Diagrama de flujo del planificador.

Figura 4.6. Algoritmo de control de procesos iísicos.

Figura 4.7. Menú principal del sistema.

Figura 4.8. Registro de diagnóstico del hardware.

Figura 4.9 Formato de punto flotante.

I¡

1;

I1

4.4

4.4

4.5

I

4.12

4.14

4.1'5

I

4.17

I

/I

!

'!

I

i

!j

I

11

I;

Ni

Figura 5.1 Esquema de pruebas del sistema.

Figura 5.2 Esquema de prueba de procesamiento Y controlFigura 5.3 Procesos de prueba de la concurrencia.

Figura 5.4 Esquema de prueba de concurrencia.

Figura 5.5 Prueba de sincronización entre procesos.

5.1

li

I'

5.2

I1

5.4

'I

5.5

li

Figura 5.6 Esquema de prueba de sincronización.

Figura 5.7 Prueba del manejo de interrupciones.

Figura 5.8 Esquema de prueba de interrupciones.

5.8

Figura 5.10 Respuesta ai escalón del simulador.

5.9

Figura 5.9 Esquema de prueba de los procesos simulados.

Figura 5.11 Validación de los algoritmos de control.

Figura 5.12 Control de un proceso.

Figura 5.13 Respuesta del proceso controlado.

Figura 5.14 Esquema de prueba del sistema completo.

Figura 5.15 Respuesta de tres procesos en operación simultánea.

Figura 6.1. Estructura de los procesos

'I

!j

11

5.9

li

5.10

I!

5.11

I/

5.11

,i

i

5.12

5.13 I1

6.3

I!

!

'i

6

I'

Introducción.

Antecedentes.

Las aplicaciones convencionales de los sistemas digitales basados en procesador han

sido tradicionalmente en el procesamiento de datos, como en computadoras, sistemas de

comunicación, procesamiento de información, etc., donde el tiempo de procesamiento no

siempre es un factor crítico. Las aplicaciones asociadas con el control de procesos fisicos,

demandan dispositivos de procesamiento que respondan de manera rápida ante la ocurrencia

de eventos, ejecutando en períodos de tiempo muy cortos algoritmos y programas de control

que permitan efectuar acciones en tiempo real.

!I

Ij

'j

11

ij

!j

;I

il

Los dispositivos de procesamiento más adecuados para estas funciones son los

procesadores especializados como los microcontroladores, los procesadores de señales y los

dispositivos ASIC. Estos dispositivos poseen en mayor o menor grado, la capacidad de

procesamiento y la velocidad de respuesta suficiente para ejecutar diversos algoritmos en

forma "simultánea", de manera tal que cada algoritmo puede ser concebido como una tarea

independiente que realiza una secuencia de actividades y que incluye puntos en los cuales el

procesador puede abandonar y regresar ai proceso para ejecutarlo. La velocidad de operación

de los procesadores les permite ejecutar programas en períodos de tiempo muy cortos Esta

alta velocidad, relativa a la baja velocidad de respuesta de los procesos fisicos da la

posibilidad de ejecutar los algoritmos de control de manera concurrente. Esta filosofia

operativa permite la aplicación de los sistemas monoprocesador, al control de diversos

eventos de manera concurrente.

Un sistema con esta filosofia de operación requiere de un sistema operativo que !Ij

administre los recursos de hardware y software, y que mediante ciertas políticas resuelva y

atienda los conflictos que se presenten durante el procesamiento, además de permitir la 11

concurrencia. El sistema o software operativo concurrente implica el paralelismo, !

simultaneidad y solapamiento de procesos de software activos, cuyo manejo debe permitir !i

que sus resultados sean obtenidos dentro de los limites de tiempo establecidos por las li;

características dinámicas de la aplicación que deben satisfacer.

li

En este trabajo se plantea el desarrollo de un sistema digital con capacidades de

procesamiento concurrente orientado al control de procesos fisicos en tiempo real, dentro del

cual se incluye el desarrollo en hardware de módulo de procesamiento bajo' un esquema

monoprocesador, un esquema de procesamiento concurrente en tiempo real y un software de

usuario orientado a aplicaciones de control de procesos. En la aplicación especifica de este

sistema se requiere controlar tres procesos fisicos y atender interfaces de usuario-sistemas.

Dentro de las tareas que debe realizar el sistema en el control de los procesos: los algoritmos

de control PiD son la principal actividad a realizar, la ejecución concurrente de algoritmos de

control o de cualquier tarea en general, se encuentra relacionada con la siguiente

problemática:

VI11

,I

ii

I!

8;

I

ij

I

I!

Un manejo eficiente de las tareas o procesos que debe ejecutar concurrentemente el

sistema, esto implica a que tarea se le asigna el procesador. LOS algoritmos PID

son la tarea principal y deben ser ejecutados en tiempo real, para poder mantener

condiciones estables en los procesos.

Manejo de cierta política para decidir en qué orden deben ejecutarse las tareas que

realiza el sistema para alcanzar un máximo desempeño en el funcionamiento.

Comunicación y sincronización entre las tareas de software para facilitar su

ejecución concurrente.

Manejo de interrupciones y cambios de contexto con tiempos mínimos.

Administración eficiente de los recursos de hardware del sistema.

Tiempo de respuesta mínimo a los procesos fisicos controlados.

ij

I.

!I

J!

!I

!I

En el trabajo de tesis se planteó la solución sobre un esquema monoprocesador con un

software operativo concurrente. El componente principal del hardware 10 constituye un

procesador especializado o microcontrolador que permite satisfacer los requerimientos

específicos de procesamiento mencionados. Por su parte el software operativo permite

atender a cada una de las tareas o procesos de software que debe realizar el sistema,

manteniendo independencia entre ellas y manteniendo la concurrencia.

jl

Ij

li

'j

I/

Objetivo.

El objetivo de este trabajo de tesis consiste en resolver una problemática asociada con

el control de múltiples procesos fisicos, mediante el desarrollo de un sistema digital basado en

un elemento procesador para ejecutar concurrentemente algoritmos de control y orientado a

procesamiento en tiempo real.

i

11

/I

I

Ij

El trabajo es probado aplicando el sistema como un controlador de múltiples procesos

que operan simultáneamente. En el desarrollo del trabajo se incluye el hardware del sistema 'I

digital, el software operativo, el software de aplicación como controlador y la implementación 1;

de un simulador de los procesos fisicos a controlar. El proyecto incluye el desarrollo del 1;

software de control (tipo PID).

1:

,

'I

!i

Metas de diseño.

Los aspectos más importantes del sistema completo desarrollado se presentan a

continuación:

Ii

I1

Sistema digital basado en microcontrolador, con E/S analógicas y digitales e

'1

interfaces de comunicación local y serie.

Arquitectura de procesamiento concurrente,

Controlar tres procesos fisicos por medio de algoritmos de control PID que se

encuentran en operación simultánea.

I!

Generación de las señales de control para los tres procesos controlados en un lapso ,i

de tiempo menor a 10 ms.

Simulación de los procesos fisicos en una computadora personal (PC) modelados I!i

'I

I/

IX

,'I

11

I!

por una ecuación lineal de primer orden. Las características analógicas. .de., cada

proceso físico simulado son obtenidas a través de un sistema de adquisicion de

datos.

Interfaces al sistema, local, y remota a través del canal serie, de fácil manejo que

permiten manipular al sistema y realizar cambios en línea de todos los parámetros

de control.

Contenido.

El desarrollo de la tesis se presenta en cinco capítulos, a continuación se presenta una

breve descripción de cada uno de ellos.

En el capítulo 1 se presenta un marco teórico sobre sistemas operativos y se enfoca

sobre todo a los sistemas de procesamiento concurrente orientados a tiempo real. En el

segundo capítulo, se realiza la descripción general del sistema implementado, el cual se

describe en cuanto a su integración y su funcionalidad. Se presentan las descripciones del

hardware del módulo de procesamiento concurrente, el software operativo y el software de

aplicación. En el capítulo 3 se describe el diseño y la implementación del hardware del

sistema, desglosado al nivel de bloques funcionales y del sistema integrado completo. En el

capítulo 4 se presentan los niveles de detalle del desarrollo e implementación del software.

Aquí mismo se divide el software operativo del software de aplicación, describiendo los

detalles importantes de cada uno de ellos. En el capítulo 5 se presenta las pruebas al sistema y

los resultados obtenidos. En el capítulo 6 se describen los procedimientos y las

consideraciones que se deben tomar para el desarrollo de aplicaciones en la plataforma

desarrollada. En el capítulo 7 se presentan conclusiones, aspectos importantes del sistema y

sugerencias de trabajos futuros.

Finalmente se presentan una serie de apéndices; en el apéndice A se presenta la

descripción de los conectores necesarios en el hardware del sistema y complementa a los

diagramas presentados en el capítulo 3 . En el apéndice B se presentan los principales

componentes de hardware utilizados en el módulo de procesamiento concurrente. El apéndice

C presenta las referencias utilizadas en el desarrollo del trabajo y finalmente se incluye un

glosario con los términos más importantes empleados en el sistema,

X

Capítulo 1. Sistemas de procesamiento concurrente.

1.1 Generalidades.

I,

Un sistema de procesamiento concurrente orientado a tiempo real encuentra Su nicho

en aplicaciones en las que un solo sistema requiere realizar de una diversidad de tareas, Y por

la importancia de cada tarea, deben ser atendidas con un mínimo de retraso y generar SUS

resultados en un intervalo de tiempo adecuado. En este trabajo se pretende resolver una

problemática asociada al control de múltiples procesos que operan simultáneamente, mediante

un solo módulo que funcione como controlador Como solución es posible plantear esquemas

de procesamiento en una arquitectura de multiprocesador o esquemas monoprocesador. En

un esquema multiprocesador se tiene un hardware sumamente complejo, que requiere de

políticas complejas para el manejo de la intercomunicación entre los procesadores y por lo

tanto se tiene un hardware de alto costo pero que no requiere de un esfuerzo notable en su

programación. Por otro lado en los esquemas monoprocesador se tiene una arquitectura de

hardware sencilla y de bajo costo, sin embargo cuando se requiere que el sistema realice

procesamiento concurrente es necesario un software complejo, cuya función sea coordinar la

ejecución en paralelo de un conjunto de tareas o procesos que se encuentran activos

simultáneamente; dicho software recibe el nombre de software operativo concurrente o de

multiproceso. El término software operativo o sistema operativo, es utilizado a lo largo de

este capítulo indistintamente, sin embargo se considera al software operativo como un

subconjunto de elementos y funciones básicas de un sistema operativo complejo.

1.2 Software operativo.

I,

Un software operativo es un conjunto de programas que administran la distribución de

los recursos de un sistema entre los diferentes procesos o tareas que deben ejecutarse. El

software operativo actúa directamente sobre el hardware del sistema de procesamiento y es

por lo tanto una interfaz entre los elementos de hardware y los programas de usuario o tareas

que se deben realizar. Cuando se genera un requerimiento o sucede algún evento en el

módulo de procesamiento, el sistema o software operativo coordina todas las acciones para

manejar de forma adecuada cada tipo de situación que se presente. El software operativo

debe resolver los conflictos que se presenten en el sistema mediante la implantación de

políticas adecuadas [Daza].

~

'1

li

'

'ij

!

Los sistemas operativos se pueden clasificar de acuerdo al número de tareas o

procesos activos que soportan en sistemas monotarea o multitarea:

Un ejemplo de monotarea se presenta en el procesamiento serie o por lotes y en

general un sistema monotarea se caracteriza por que sólo una tarea se encuentra

activa a la vez, la cual acapara el tiempo de procesador hasta que ella termine su

ejecución y sólo entonces una nueva tarea puede ser ejecutada [Milan].

1.1

1:

'3

1)

Conceptos básicos de sistemas operativos.

Capítulo 1

1

Un sistema multitarea permite realizar varias tareas distintas "al mismo tiempo", en

estos casos el sistema operativo soporta varios procesos que se encuentran activos al

mismo tiempo. Dentro de este tipo se tienen los sistemas multiprogramados y de

tiempo compartido [Hwang].

Los sistemas operativos por otra parte pueden estar orientados ai manejo de

aplicaciones, como manipulación de archivos o desarrollo de software, donde el tiempo no es

un parámetro importante, o pueden estar orientados a aplicaciones en tiempo real en las que

el sistema debe dar servicio a tareas cuya ejecución se sincroniza con eventos externos a ellas.

1.2.1 Sistemas de tiempo real.

En los sistemas de tiempo real las salidas no sólo dependen de las entradas y

secuencias en las que estas se presentan, sino también del instante en el que la salida debe

hacerse presente. La relación de un sistema de tiempo real con respecto al momento que se

deben presentar las salidas establece la constante de tiempo del sistema, cuyo valor determina

la velocidad con la que el sistema debe actuar ante las distintas entradas.

En sistemas de tiempo real, los eventos con los que se sincronizan las tareas pueden

ser programados o indeterminados con respecto al tiempo, estos eventos se relacionan

normalmente con señales eléctricas generadas por el mismo sistema digital o por los

elementos fisicos que conforman a la aplicación. El procesador por lo tanto debe incluir

características que permitan la operación en tiempo real, como interrupciones,

temporizadores, etc. [Daza].

Un software operativo en tiempo real, debe ser multitarea, con características de:

programación de eventos, priorización de tareas, sincronización y comunicación entre tareas,

temporizadores y manejo de interrupciones. Estas características permiten de algún modo

garantizar que las tareas sean realizadas en el intervalo de tiempo requerido por la aplicación

en tiempo real.

1.2.2 Sistemas concurrentes.

Un sistema multitarea o concurrente consiste de un grupo de programas que permiten

que múltiples procesos o tareas de software independientes coexistan activos y les permite a 1

todos los procesos operar simultáneamente. La alta velocidad de un procesador relativa a las :

operaciones fisicos que controla, permite compartir el procesador sobre varios procesos

lentos. El procesador salta de un proceso a otro y ejecuta una parte de cada uno en un

intervalo de tiempo dado [Porat]. El siguiente proceso que se ejecuta es seleccionado 'j

mediante una planeación a la que responde el sistema operativo. Entre cada conmutación de I j

tareas se realiza un cambio de contexto que incluye el almacenamiento del estado del proceso '

que sale de ejecución y la restauración del contexto del estado que entra.

':

11

1.2

1;

Conceptos básicos de sistemas Operativos.

Capítulo 1

i

i

En el procesamiento concurrente los procesos o tareas deben ser escritos como una secuencia

de actividades e incluir puntos en los cuales el procesador pueda dejar y regresar al proceso,

y/o incluir una política que permita la salida y entrada de los procesos en cualquier punto de

su estructura. Cada proceso o actividad inicia o reinicia su operación en un punto de entrada

determinado por el sistema operativo, y es disparado por un evento externo o por otra

actividad y puede a su vez iniciar a otras actividades o tareas.

I1

1

I,

í

I!

'I

1.3 Núcleo del sistema operativo.

I!

El sistema operativo tiene como principal función controlar la ejecución de cada uno

de las tareas o procesos que se desea realice el sistema. El primer nivel de software de un

sistema operativo está constituido por un conjunto de rutinas y herramientas que permiten el

manejo de todos los componentes de hardware y software del sistema.

/I

11

I!

i

'I

El núcleo de un sistema operativo es el primer nivel de software que trabaja sobre el

hardware del sistema, configura y maneja los componentes del hardware. El núcleo realiza las

funciones primarias del sistema operativo, como la gestión de procesos, el manejo básico de

entradasísalidas, el manejo de interrupciones, la configuración e inicialización del sistema, la

comunicación y sincronización entre procesos y el manejo de errores y excepciones.

/j

,I'

I

1;

1.3.1 Elementos del sistema operativo.

1;

I

Para trabajar en un sistema multitarea, un proceso o una tarea de software requieren

de rutinas especiales, estructuras de datos que controlen el flujo de ejecución y herramientas

para la sincronización e intercambio de datos.

''

,,

1;

Dentro de las rutinas básicas que se requieren para el funcionamiento del núcleo del

sistema se tienen las siguientes:

i:

Una rutina que maneje el procesador y decida su asignación sobre un conjunto de

11

tareas o procesos activos.

1

Una rutina que inicialice, configure y maneje al hardware y al software del sistema. 'j

Rutinas y/o políticas que permitan responder a eventos como interrupciones,

errores y excepciones.

Con este conjunto básico de rutinas es posible controlar las tareas que se ejecutan y

responder a los eventos que se presentan en el sistema. Para el funcionamiento del sistema se

requiere también de un conjunto básico de estructuras de datos auxiliares en el control de las

tareas de software, dentro de este conjunto básico se incluyen las siguientes tres:

Una tabla de tareas o procesos en RAM, que contenga punteros a los puntos de

entrada de las actividades esperando a ser ejecutadas.

1.3

,I

II

Conceptos básicos de sistemas operativos.

Capítulo 1

Una tabla de procesos, de la cual se designará la siguiente tarea poseedora del

procesador basado en cierta política que permita tomar la decisión.

* Una estructura en memoria RAM que permite almacenar el estado de los registros

del procesador para cada uno de los procesos que se encuentren activos.

Dentro de las herramientas para la sincronización e intercambio de datos, que

permiten la administración del sistema digital, están:

Los semáforos que se usan para sincronizar, excluir y/o distribuir recursos de

hardware y software. Pueden constituirse por una variable booleana o por un

contador.

Los buzones son bloques de memoria usados para la transferencia de información y

coordinación entre procesos.

En la Figura 1.1 se ilustran los elementos básicos que conforman un sistema

operativo. Las rutinas básicas se auxilian de los buzones, de los semáforos y de las tablas del

sistema, para poder decidir sobre la asignación de los recursos de hardware sobre cada uno de

los procesos de usuario

..........................................................................

Pmcesos de usuario

.....................................

....................

...............,

-

4

Núcleo del

sistema operativo.

.......................

Tablasdel

!

..................

I Rutinas bhsicas

y de procesos

Tablas

descriptivas

.......................

j

........................

j

Herramientas

Hardware

I

..................................

.....................................

4

.........................

....................................

Hardware

...........................................................................

Figura 1.1 Estructura básica de un sistema operativo.

1.4

I

Conceptos básicos de sistemas operativos.

Capítulo 1

1.3.2 Procesos.

Se define como proceso de software a un conjunto de líneas de código que se

encuentran en ejecución en cierto momento [Milan] y tiene como objetivo hacer que el

sistema desempeñe cierta función al nivel de usuario. Un proceso se puede considerar como

la unidad funcional del software de aplicación. En algunos casos el término proceso y el

término tarea son manejados como sinónimos, sin embargo una tarea puede estar constituida

por uno o varios procesos, o sea un proceso puede integrar a una tarea o una actividad que

debe realizar el sistema o simplemente ser una parte de ella. Dentro del desarrollo de este

documento se utiliza la palabra proceso para referirnos a los programas de software que

conforman las tareas de aplicación del sistema.

1.3.2.1 Estado de los procesos.

Los procesos por su estado se pueden clasificar en activos o inactivos. Un proceso

activo se diferencia de uno inactivo en que el primero se encuentra compitiendo por el USO del

CPU. Un proceso activo puede estar en cualquiera de los tres estados de la Figura 1.2:

En ejecución, procesos poseedor del CPU.

Listo, es el proceso en la cola para tomar posesión del CPU.

Bloqueado, es un proceso que tiene que esperar a que ocurra cierto evento para ser

ejecutado[Tanembauml].

Activos

...............

E : Ejecución

. .

.: :. I n a c t i v o s

. .

................................................

I

.

L : Listo

B : Bloqueado

I:

Inactivo.

!I

I/

Figura 1.2 Estados de los procesos.

En un momento dado pueden presentarse cambios de un estado a otro, de acuerdo a

la ocurrencia o no de determinados eventos a los que debe responder cada proceso particular.

':

','

1.4 Gestión de procesos.

La gestión de procesos es uno de los componentes básicos de todo núcleo de sistema

operativo y es la parte encargada de administrar y controlar el comportamiento de los ,;

procesos de software de un sistema, esto es manejar los procesos inactivos o activos en sus ,,

diferentes estados: listos, en ejecución o bloqueados. La gestión de proceso se encargal,

también de manejar los procesos residentes en el sistema o creados por el usuario.

'!

j

1.5

'I

Capítulo 1

Conceptos básicos de sistemas operativos.

,

I1

El manejo de los procesos se realiza en base a cierta política que determina el orden en

que el CPU es entregado a cada uno de los procesos. El elemento encargado de realizar esta

función se llama planificador y tiene como objetivo optimizar el rendimiento del sistema de

acuerdo a los puntos que se consideran importantes dentro de las particularidades del sistema.

Ij

I

1;

1:

'i

Algunos criterios que permiten definir al planificador son: la relación de tiempo de

ejecución entre el software de aplicación y el software operativo, el número de procesos

ejecutados por unidad de tiempo, el tiempo promedio que un proceso debe esperar para que

se le asignen los recursos de hardware [Milan]. En general el criterio de selección del

planificador debe ser de acuerdo a las características consideradas más importantes por el

diseñador.

1:

Ji

,I

1;

'I

1,

1.5 Comunicación y sincronización entre procesos.

La comunicación y sincronización entre procesos es la parte de un sistema operativo

que permite que dos o más procesos se relacionen entre ellos, con los elementos del

hardware, o con algunos eventos externos a los mismos procesos.

Dos elementos básicos para el manejo de la comunicación y sincronización son los

semáforos y buzones. Los semáforos son elementos principalmente usados para la

sincronización entre procesos, se utilizan para determinar el estado de cierto evento que

permite a los procesos determinar el siguiente paso dentro de su ejecución. Los semáforos

pueden ser conformados por una variable booleana o por un contador cuyo estado es

modificado por la sucesión del evento que se pretende indicar.

I/

I/

!i

Los buzones por su parte se utilizan para el intercambio de conjuntos de datos, ' y

!I

además de permitir la sincronización entre procesos. Cada buzón está integrado por un ,;

segmento de memoria, dicho segmento se divide principalmente en dos bloques, uno para el I;

almacenamiento de la información y otro que permite determinar tanto el estado de la '1

información que almacena como el estado del mismo buzón.

I1

1;

El manejo de semáforos y buzones permite la cooperación entre diversos procesos

sobre una misma tarea común a ellos. El manejo de la sincronización y comunicación

pretende resolver problemas de intercambio de información y sincronización de procesos, y

de manejo de recursos del sistema hardware/software a través de la exclusión mutua.

1.6 Manejo de los elementos de hardware.

i

El manejo de hardware de un sistema pretende gestionar la asignación de estosii

recursos a los procesos de usuario. Una gestión eficiente del hardware se relaciona con una:

identificación de las características sobre el uso de cada recurso y sobre las funciones qu6

debe realizar. Debe realizarse un análisis que permita identificar si el uso de cada recurso es'

apropiativo por parte de los procesos o si el recurso puede ser compartido por ellos

[Tanembauml]. En ambos casos se establecen técnicas y/o políticas que permitan el manejo

/i

1;

:

!I

I<

1;

Capítulo 1

Conceptos básicos de sistemas operativos.

j

I!

'!

exclusivo o compartido de los recursos

!i

En el caso del uso exclusivo de un recurso, a través de elementos de sincronía se

puede lograr la exclusión mutua entre los distintos procesos que le requieren. Cuando un

recurso es compartido entonces es necesario controlar su compartición mediante una

planeación estática (fuera de línea) o dinámica (durante la operación).

',

I!

',

11

'!

El manejo de cada componente del hardware requiere de un programa que permita

controlarlo, a través de este elemento llamado controlador, a cada recurso se le dan ordenes,

se le establecen parámetros y en general, se coordina la operación del recurso. Estas rutinas

se encuentran disponibles para ser llamadas por los procesos de aplicación y tienen como

objetivo facilitar al usuario el manejo del hardware.

11

II

I

11

1;

I/

Ij

1.7 Manejo de interrupciones.

Otro de los aspectos importantes que deben considerarse en los sistemas operativos

son las interrupciones. Las interrupciones son eventos de hardware o software que cambian el

flujo normal de un programa que se encuentra en ejecución y permiten sincronkar la

operación de los dispositivos de hardware con el procesador [Tanembauml]. Las

interrupciones, ya sean de hardware o de software se generan como respuesta a algún evento

que requiere de atención inmediata del procesador, como intermpciones de E/S,

temporizadores o timers, etc. (en el caso del hardware) y detección de errores y excepciones

(como interrupciones de software).

ii'I

I!

li

I!

j

(

\

I!

'I

!i

Dentro del manejo de las interrupciones deben definirse características como niveles

de prioridad de las interrupciones, detectar segmentos de código que no deben interrumpirse, ,I

el tiempo de atención a las solicitudes de interrupción, etc. Con el fin de determinar las I!

políticas adecuadas que permitan manejar las interrupciones garantizando que las solicitudes

de interrupción son atendidas, manteniendo una operación correcta tanto en las rutinas de ,,I!

atención como en los progranias interrumpidos y que posteriormente retoman el uso del

I!

procesador.

1;

ii

1.8 Aplicaciones de control en tiempo real.

I!

Los sistemas de tiempo real se usan en aplicaciones donde es necesario aceptar y dar I

respuesta a sucesos, en su mayoría externos al sistema, con el menor retardo posible. En ' j

control industrial, comunicaciones, aplicaciones militares, etc. se requieren de sistemas que li

81

brinden procesamiento en tiempo real.

)

Cada aplicación específica de tiempo real presenta características especiales que

permiten al sistema establecer estrategias y técnicas adecuadas para que realice atención en

tiempo real En aplicaciones industriales se requiere regular el comportamiento de los

procesos a través de alguna técnica de control La tarea que permite controlar los procesos se

presenta como un programa cuya ejecución se sincroniza con una interrupción que determina

1.7

Conceptos básicos de sistemas operativos.

Capítulo 1

el periodo de muestreo del proceso a controlar.

La frecuencia de ejecución de una tarea de control se relaciona directamente con la

constante de tiempo de la planta a controlar. Por el teorema del muestreo se determina una

frecuencia de dos veces el inverso de la constante de tiempo de la planta, pero para obtener

mejores resultados el periodo debe ser entre 5 y 50 veces el inverso de dicha constante

[Hoang].

En las aplicaciones de control el funcionamiento del sistema debe sincronizarse con el

periodo de muestreo establecido por las plantas que interesa controlar. Esto permite definir:

El tiempo máximo de ejecución de las tareas de tiempo real

Políticas para el manejo de las tareas y de los recursos del sistema.

Tareas criticas que requieren procesamiento en tiempo real.

Con la definición del periodo de muestreo y con la identificación de los puntos

anteriores es posible definir la base de un sistema operativo que realice procesamiento en

tiempo real, para aplicarlo al control de procesos industriales.

'!

!

1.8

I.

Capítulo 2. Descripción del sistema.

2.1 Introducción.

En este capítulo se realiza una descripción general del sistema desarrollado, el cual se

encuentra integrado por tres bloques principales: el módulo de procesamiento concurrente, la

interfaz de comunicación serie y los procesos fisicos controlados. El módulo de

procesamiento concurrente es la parte más importante de este trabajo. Los otros dos

elementos presentan su importancia en la aplicación del módulo de procesamiento como

controlador de los procesos físicos. Se presenta también la descripción funcional y de

configuración tanto general como de cada uno de los componentes del sistema.

Dentro de la descripción de cada uno de los bloques del sistema se destaca el módulo

de procesamiento concurrente y se presentan sus tres componentes: hardware, software

operativo y software de aplicación. El hardware y el software operativo establecen la

plataforma para el procesamiento concurrente, mientras que el software de aplicación o de

usuario permite configurar al sistema para su operación como controlador.

‘i

1

(i

;I

‘i

‘i

2.2 Descripción del sistema.

8!

El sistema se encuentra integrado por tres bloques: el módulo de procesamiento

concurrente, la interfaz de comunicación serie y los procesos físicos controlados que integran !:

un sistema de multicontrol sobre tres plantas que operan simultáneamente, Figura 2.1. El !:

I/

módulo de procesamiento concurrente realiza las funciones de un controlador y opera ;

directamente sobre las plantas o procesos fisicos. Cada proceso fisico responde en función a ‘i

las señales generadas por el módulo de procesamiento o control y la respuesta obtenida en las

plantas es retroalimentada al módulo de procesamiento para generar los valores de control y ,;!

lograr una regulación adecuada sobre ellas. La señal de control para cada proceso físico es !i

1

obtenida mediante la ejecución de algoritmos PID.

1;

procesos

controlados

4-p

lnterfaz de

acceso remoto

I’

Modulo de

procesamiento

concurrente

Figura 2.1 Diagrama a bloques del sistema.

I:

El módulo de procesamiento concurrente se encuentra basado en una arquitectura’

monoprocesador, que permite ejecutar varias tareas en forma “simultánea”. Se encuentra

constituido por un microcontrolador que realiza varias funciones en forma concurrente, y

realiza el control de los procesos fisicos en tiempo real.

2.1

I/

Capítulo 2

Descripción del sistema.

Las plantas o procesos fisicos se implantaron en un simulador, mediante una PC con

un sistema de adquisición de datos. Cada proceso corresponde a un sistema andógico

modelado por una ecuación de transferencia lineal de primer orden. Las entradas y salidas de

cada proceso simulado corresponden a una entrada y una salida analógica del sistema de

adquisición de datos. Los procesos son simulados uno tras de otro en forma cíclica y el

tiempo de ejecución de cada proceso se mantiene dentro de los limites definidos por las

funciones matemáticas usadas en la simulación.

Por otra parte, la PC es usada en la Interfaz Hombre Máquina y tiene como objetivo

proveer de acceso remoto al módulo de control, manteniendo comunicación serie mediante el

estándar RS-232. Provee de una interfaz amigable que permite, entre otras cosas, cambios en

los parámetros de los algoritmos PID, habilitar o inhabilitar procesos, etc

2.3 Módulo de procesamiento concurrente.

El módulo de procesamiento concurrente es un sistema digital basado en procesador,

constituido por tres bloques básicos de acuerdo a la Figura 2.2:

El hardware del sistema,

El software operativo que permite el procesamiento concurrente y

El software de aplicación.

operativo

,I

.I

Figura 2.2 Conformación del módulo de control

El núcleo del módulo de procesamiento concurrente se encuentra conformado por el 'j

hardware, sus elementos se agrupan en tres bloques principales y su descripción se presenta

!

en el apartado 2.3.3. Estos submódulos son:

Procesamiento y memoria.

E/S analógicas y digitaies.

Interfaz al usuario.

22

'1

Descripción del sistema.

Capítulo 2

1,

El siguiente nivel se encuentra constituido por el software operativo, su principal

objetivo es permitir el control concurrente de los procesos fisicos además de controlar y

administrar los recursos de hardware y software del módulo de procesamiento.

El software de aplicación consiste en un conjunto de programas enfocados a que el

módulo de procesamiento regule adecuadamente el comportamiento de los procesos fisicos a

controlar.

Los sistemas digitales basados en elementos de procesamiento basan su operación en

la interacción de estas tres partes básicas mencionadas. La relación entre ellas permite a los

sistemas digitales estar capacitados para realizar una gran diversidad de tareas, realizando

cambios sólo a nivel del software de aplicación.

'1

2.3.1 Descripción funcional del módulo de procesamiento.

El módulo de procesamiento se encuentra constituido por un conjunto de elementos

de hardware y software que establecen características generales, básicas y típicas de algunos

sistemas de procesamiento. Lo que establece la particularidad en el sistema es el software de

aplicación el cual se encarga de realizar el control de los procesos fisicos.

Este conjunto de tareas de aplicación se encuentra residente en la memoria ROM del

módulo de procesamiento, al igual que el software operativo. El microcontrolador inicia su

operación a través del software operativo cuya primera función consiste en inicializar los

componentes del hardware, del software operativo y del software de aplicación,

Posteriormente el software operativo ejecuta una rutina que decide que proceso de sofiware

es el primero al que se le asigna el procesador, esta rutina es conocida como planificador.

La ejecución del planificador se encuentra sincronizada con una serie de

interrupciones de timer utilizadas para evitar que un sólo proceso acapare al CPU; estas

interrupciones además se encuentran programadas para que se presenten de acuerdo al

periodo de muestreo establecido por las plantas a controlar; de esta forma se sincroniza

finalmente la ejecución de las tareas de control con el periodo de muestreo requerido.

'i

'I

Dentro de las tareas que se realizan a nivel del software de aplicación, la principal ,I

consiste en mantener a cada planta en cierta condición de operación deseada mediante la

adquisición de datos, la ejecución de algoritmos PiD y la salida de datos. Las tareas de

aplicación dentro de sus funciones se encargan también de la comunicación con el usuario ',

mediante una interfaz local y mediante una interfaz con la PC a través del canal serie, estas I!

interfaces permiten al usuario visualizar e introducir información al sistema mediante un ,'

conjunto de menúes. El módulo de procesamiento realiza también funciones de diagnostico

sobre algunos de sus componentes de hardware, lo que permite detectar algunas fallas en el '

!!

sistema.

I,

,:

,,

2.3

Capítulo 2

Descripción del sistema.

I,

1.

I

'!

2.3.2 Consideraciones del módulo de procesamientopara lograr un funcionamiento adecuado del módulo de procesamiento es necesario

tener en cuenta importantes consideraciones. Dentro de estas consideraciones se cenceuntran

las siguientes:

!I

1:

I

Ij

''1

El software operativo garantiza que los programas de aplicación se ejecutan de

acuerdo a sus características.

Il

Las tareas de control, que tienen mayor relevancia que las interfaces, se les otorga

un tiempo mayor de procesador, para que sean ejecutadas en un lapso de tiempo

menor al establecido por el periodo de muestreo.

lj

lj

Ii

En un lapso de tiempo igual al periodo de muestreo debe también ejecutarse al

menos uno de los procesos de interfaz al usuario para garantizar que no sólo los

algoritmos de control sean poseedores del procesador.

l.

li

I1

La última consideración es que el tiempo de ejecución de las tareas de control debe

ser menor a una cuarta parte del periodo de muestreo, para garantizar la ejecución

de las tres tareas de control, la ejecución de al menos una de las interfaces al

usuario, además del tiempo requerido por el software operativo.

li

Ii

'1

':

!i

2.3.3 Descripción general del hardware.

'I

El hardware del módulo de control se encuentra conformado de acuerdo al diagrama

de bloques presentado en la Figura 2.3.

I;

I:

I

Módulo de Procesamiento Concurrente.

Procesamiento

I

Analógicas

ydigitales

y control

v

........

Fuente de

alimentación

lnterfaz al

........

usuario

Figura 2.3 Diagrama a bloques del módulo de procesamiento.

Procesamiento Y control. Es el submódulo encargado de la coordinación general de las

funciones del sistema; provee de capacidad de cálculo y procesamiento para ejecutar i

los algoritmos de control, coordina las señales de control necesarias para todo el 11

i

2.4

!j

'I

Descripción del sistema.

Capítulo 2

sistema e interpreta y ejecuta las ordenes provenientes de la interfaz bcal 0 de la

comunicación serie, Se constituye por el microcontrolador y la lógica necesaria Para la

decodificación y control. Consiste también de una memoria ROM en la Cual residen

software operativo y de aplicación para el microcontrolador Y de una memoria RAM

que almacena 10s datos que se requieren durante la operación. Se incluye además el

cristal oscilador y el reset del microcontrolador.

E/S halógicas y digitales. Este submódulo está conformado por tres grupos: una interfaz de

E/S analógicas que consiste de dos conjuntos de tres señales, uno de entrada y otro de

salida, con rangos de O a 5 V y una resolución de 12 bits. Una interfaz digital

consistente de 7 líneas de salida digital y de 7 líneas de entrada digital, el puerto de

entrada puede ser atendido por una interrupción en el microcontrolador. El tercer

componente lo integra un generador PWM, este submódulo es capaz de generar tres

grupos de señales de PWM tnfásicos de niveles TTL.

Interfaz al usuario. La interfaz ai usuario se encuentra constituida por una interfa local que

consta de una pantalla de cristal líquido de 2 renglones por 16 columnas, y un teclado

matricial de 16 teclas. La interfaz funciona a través de menúes para facilitar su manejo

por parte del usuario. También se incluye en este submódulo una interfaz serie que

permite establecer comunicación serie con una PC y permite una fácil interacción con

el módulo de procesamiento concurrente.

Fuente de alimentación. Este submódulo provee de las tensiones de CD adecuadas para el

fu~CiOnamient0de cada uno de los componentes del módulo de procesamiento,

Provee tensiones de 2 5 y ? 15 VcD.

2.3.4 Descripción general del software.

El soRware básicamente consta de dos partes: el software operativo y el software de

aplicación. En la Figura 2.4 se presenta un aspecto general del software del sistema.

Figura 2.4 Esquema general del software.

2.5

Capitulo 2

Descripción del sistema.

!1

I

El software operativo da soporte a los procesos de usuario y permite que estos

residan activos de forma simultánea en el hardware del sistema. Mientras que el software de

aplicación tienen como finalidad efectuar las tareas de control de los procesos fisicos y de

interfaz de usuario.

;

I

!

;i

2.3.4.1 Software operativo.

li

EI software operativo tiene como función administrar los recursos de hardware Y 10s

procesos de software, permitiendo la concurrencia de 10s programas de aplicación Y la

ejecución de los algoritmos de control en tiempo real. Algunas características y funciones del

software operativo son las siguientes:

,I

!i

'i

N

i

!;

a)

b)

c)

d)

e)

Capacidad de procesamiento concurrente

Orientado a procesamiento en tiempo real

Inicialización del sistema

Gestión de procesos.

Sincronización y comunicación entre procesos.

t) Manejo de interrupciones.

g) Administración de los recursos de hardware.

El'software operativo basa su capacidad de concurrencia en dos aspectos importantes

de la arquitectura del software: uno es el manejo de multiniveles de colas de procesos activos,

donde cada cola se maneja con una política de round robin, y otro la asignación a cada cola

de cuantos de tiempo finitos de procesador de acuerdo a la prioridad de la cola.

II

'1

I/

11

Con la asignación de tiempos finitos en función de la prioridad de la cola, se garantiza

la ejecución de los algoritmos de control en un tiempo finito que es función de dichos cuantos

de tiempo; y mediante un conjunto de variables que permiten la coordinación y sincronización

de los procesos con respecto a otros procesos y al tiempo, es posible tener las señales de

control en tiempos discretos.

I:

I

,I

,I

1,

2.3.4.2 Software de aplicación.

El software de aplicación es un conjunto de rutinas realizadas en lenguaje ,I

ensamblador, que tienen como objetivo realizar las tareas del controlador. Los programas I,:

para el funcionamiento del controlador son los siguientes:

1;

Aiaoritmos P i D Son tres rutinas encargadas de calcular las acciones de control de las plantas

que se desean controlar. Estas tareas tienen prioridad alta y deben ejecutarse

constantemente.

!

~

'I

,

Salida de datos Es el proceso de software encargado de mandar por medio de la interfaz de

E/S analógicas, los resultados de la ejecución de los algoritmos PID a cada planta

correspondiente

I,

li

2.6

'I

Capítulo 2

Descripción del sistema.

Menú del sistema. Esta tarea utiliza la pantalla LCD y el teclado para dar al usuario algunas

opciones que permiten manipular al sistema, como mostrar y cambiar parámetros, dar

de alta o de baja el proceso correspondiente a una planta, etc. Dentro de las opciones

del menú destaca el diagnóstico del sistema el cual permite obtener información de

algunas condiciones del hardware y del estado de operación del sistema para

identificar errores o alguna mala operación del sistema.

Comunicación Serie. Es la encargada de atender las requisiciones de envío y recepción de

información a través del canal serie. Corresponde a un proceso de prioridad baja que

se encuentra siempre activo e incluye básicamente las mismas opciones que en el menú

del sistema. Este proceso interactúa directamente con la PC a través de la cual se

seleccionan las acciones que debe realizar el módulo de procesamiento comunicar el

resultado de las acciones a la PC.

2.3.5 Características del módulo de procesamiento.

El módulo de procesamiento concurrente incluye un conjunto de elementos de

hardware y software que le permiten ser utilizado en un variado campo de aplicaciones.

Dentro de estas características se tienen:

Hardware:

Sistema monoprocesador.

3 canales E/S Analógicos.

7 canales E/S Digitales.

Interfaz local (Pantalla y teclado).

Interfaz de comunicación serie.

Fuente de alimentación.

Facilidades de hardware para autodiagnóstico

Software:

Software operativo concurrente orientado a procesamiento en tiempo real.

Software de aplicación del módulo como controlador.

* Ejecución de algoritmos PID

Cambio de parámetros de los PID.

* Manejo de interfaz local.

Comunicación serial.

* Diagnostico del hardware.

Estas características permiten obtener un módulo de procesamiento concurrente

aplicado al control de procesos. El procesamiento concurrente permite atender varios

procesos fisicos independientes dentro de ciertas condiciones de operación deseada y el

tiempo de procesamiento se limita de acuerdo a las características de la aplicación. El

2.1

Capítulo 2

Descripción del sistema.

hardware debe poder realizar procesamiento en tiempo real para garantizar una regulación

adecuada sobre el funcionamiento de los procesos físicos.

2.4 Descripción de los procesos físicos controlados.

Las plantas utilizadas fueron implementadas en una computadora personal, mediante

un simulador. Cada planta fue representada por una función de transferencia lineal de primer

orden de acuerdo a la ecuación:

F( S) =

1

100 x 10-)s+ 1

Dicha función fue programada en la computadora en lenguaje C, obteniéndose un

sistema de tipo una entrada una salida, con sus niveles escalados donde la amplitud del 100%

iorresponde a un valor de voltaje de 5 V. La constante de ~ O O X ~ Ose. tomó

~

de una función

de transferencia correspondiente a la identificación práctica de un motor de inducción

trifásico [Solís].

2.4.1 Periodo de muestreo.

La respuesta a un escalón de la función anterior se presenta en la Figura 2.5; en ella

se identifica la constante de tiempo de los procesos a un valor de 1 O0 ms, la cual se relaciona

con el 63.2% de la amplitud total del sistema. Mediante el valor obtenido para la constante

de tiempo se determinó el periodo de muestreo del sistema considerando un periodo de un

décimo del valor de dicha constante, lo que determina un periodo de muestreo de 10 ms.

r

O

,,e

Pendiente

IO0

l/r

200

300

400

500

rns

Figura 2.5 Respuesta al escalón de los procesos controlados.

Este periodo de muestreo establece las restricciones de tiempo tanto en el módulo de

procesamiento como en la simulación de los procesos a controlar. Con el periodo de

2.8

Capítulo 2

Descripción del sistema.

muestre0 en 10 ms se determinó el límite de tiempo por debajo del cual se deben ubicar los

tiempos máximos de ejecución de los algoritmos de control PiD. Si se considera que se tienen

tres algoritmos PID además de las interfaces al sistema entonces se puede plantear una

repartición inicial del tiempo de procesador sobre cuatro tareas. Considerando una repartición

equitativa se obtiene un tiempo de ejecución máximo de 2.5 ms por cada tarea y tomando en

cuenta que el software operativo toma O. 15 ms en realizar su operación, se establece un límite

2.35 ms para la ejecución completa de cada tarea de contiol. Con esto es posible establecer

un criterio para determinar el límite máximo en la ejecución de los algoritmos de control, de

tal forma que sea posible que se ejecuten otras tareas como las interfaces al sistema dentro del

periodo base de 10 ms.

2.4.2 Simulación de los procesos.

La simulación de los procesos en PC se basó en el algoritmo de Runge-Kutta [Zill] de

segundo orden. Para la simulación de los procesos se requiere de un sistema de adquisición de

datos para mantener las características analógicas requeridas por cada planta e interaccionar

con el módulo controlador, Figura 2.6.

I

:I

Módulo de

procesamiento

concurrente

\

j

i

Tarjeta de adquisición

.........................................................................................................................

:

Figura 2.6 Diagrama de los procesos físicos controlados.

El módulo de procesamiento entrega a la PC las señales de control analógicas para

cada planta; cada señal se convierte de analógica a digital por el sistema de adquisición de

datos de la PC y esta calcula los valores de salida de cada planta. El sistema de adquisición de

datos incluye 3 canales analógicos de salida, por medio de los cuales se retroalimentan al

controlador las variables monitoreadas de las plantas controladas, haciéndose esto

cíclicamente para obtener el comportamiento de la planta. El diagrama de flujo

correspondiente a la operación de las plantas o procesos controlados se representa en la

Figura 2.7.

2.9

Descripción del sistema.

Capítulo 2

9

Iniciar

adquisición

-

Leer CAüi

Inicio

I

Inicio conv.

CADi

Simular

Proc (i-1)

CAü(i-I)

Figura 2.7 Algoritmo de simulación de los procesos.

A través de la simulación de los procesos fisicos controlados se probó el

funcionamiento del módulo de procesamiento como controlador; manteniendo una regulación

independiente sobre cada planta mediante la ejecución concurrente de cada tarea de control.

2.10

Capítulo 3. Desarrollo del hardware.

3.1 Introducción.

I

'i

En este capítulo se presenta el desarrollo del hardware del sistema como una

secuencia lógica con respecto al capítulo anterior. Se detalla el diseño de cada bloque

integrante del módulo de procesamiento concurrente así como su asignación de direcciones

en el mapa de memoria. En la Figura 3.1 se presenta el diagrama a bloques del módulo de

procesamiento concurrente para facilitar la descripción del capítulo.

'I

'j

'!

,

Módulo de Procesamiento

-*

Memoria

Interfaz

Serie

Procesamiento

y Control

PWM

Interfaz EIS

Analógicas

Interfaz EIS

I ...................................................................................................

- 1

Fuente de alimentación

..................................................................................................

Figura 3.1 Hardware del módulo de procesamiento.

3.2 Diseño del módulo de procesamiento.

El módulo de procesamiento fue diseñado, implementado y probada por etapas

partiendo del núcleo básico de procesamiento y control, sobre el cual se le adicionaron el

resto de los bloques funcionales presentados en la Figura 3 . 1 .

3.2.1 Submódulo de procesamiento.

El principal componente de este submódulo es un microcontrolador 80C3 10 fabricado

por Dallas Semiconductors, el cual es compatible 100% con los microcontroladores de Intel

de la familia 8051, pero este microcontrolador mantiene un desempeño mucho mayor. Un

mismo programa puede ser ejecutado hasta tres veces más rápido en el 80C310 para una

misma frecuencia de reloj, que en los microcontroladores de Intel de dicha familia.

3.1

j

I

Capítulo 3

Desarrollo del hardware.

I

En este submódulo se incluyen todos los elementos TTL utilizados para la

decodificación, sincronización y multiplexión de todas las líneas necesarias en la operación del

módulo de control, así como un cristal el cual es necesario para la generación de la señal de

reloj del sistema de control.

I

,j

Oscilador

I'

direcciones

Figura 3.2 Submódulo de procesamiento y control.

',

Funcionalmente este módulo se encarga de coordinar y sincronizar el funcionamknto !

de todos los componentes del sistema (hardware del módulo de control, comunicación con la I!

PC y control de los procesos fisicos). Para mantener un funcionamiento correcto en el j

sistema, el submódulo de procesamiento hace uso del software operativo y de los programas j

de aplicación. (Figura 3.2).

3.2.2 Submódulo de memoria.

'I

1;

El submódulo de memoria externa se encuentra integrado por una memoria ROM y I:

una memoria RAM,de acuerdo a la Figura 3.3. Todas las tareas y funciones que realiza el 'I

módulo controlador corresponden a programas de software alojados en memoria ROM y son

ejecutadas por el submódulo de procesamiento. Algunos de estos programas corresponden al

software operativo del módulo de control el cual permite coordinar y controlar las tareas que

debe realizar el módulo controlador. Los programas que realizan las tareas del usuarioli

corresponden al software de aplicación y su principal característica es que estas tareas se';

ejecutan en el ambiente que suministra el hardware y el software operativo. Tanto el software:

operativo como de usuario requieren de la memoria RAM para poder realizar sus funciones. '

1

3.2

Capítulo 3

Desarrollo del hardware.

c

Procesamiento

y control

Memoria

I

Memoria

de direcciones

Figura 3.3 Submódulo de memoria.

I

I'

3.2.3 lnterfaz de entradadsalidas analógicas.

Este submódulo da las capacidades al sistema de procesamiento para interconectarse

con sistemas analógicos, en concreto esta jnterfaz permite realizar el monitoreo del estado de

los procesos controlados y permiten que sean entregadas las señales de control analógicas

para cada proceso. Este bloque está integrado de acuerdo a la Figura 3.4. El canal D o 3 de

ambos convertidores es interconectado con fines de poder realizar el diagnóstico de esta

intetfaz.

1;

';

':

'I

,;

1;

;I

I,

Figura 3.4 Interfaz de E/S analógicas.

Este submódulo permite al módulo de control intercambiar información con los

procesos controlados a través de un par de convertidores fabricados por Maxim, cuyas

principales características se muestran en la Tabla 3 . 1 .

3.3

Capítulo 3

Desarrollo del hardware.

Resolución

12 bits

12 bits

No. parte Conversión

A/D

MAX 182

DIA

MAX 527

Canales

4

4

R.V.E.

0-5 Volts

0-5Volts

Tiempos

tconvcrjián

12011s

tsstablccimicnto.

611s

Tabla 3.1 Características de los convertidores usados.

Ambos convertidores se aislan de los procesos controlados mediante circuitos

operacionales. Las señales de entrada al convertidor analógico a digital (CAD) se filtran

previo a su adquisición. El buffer digital tiene como finalidad aislar al bus de datos del

módulo de procesamiento del CAD, para evitar la generación de errores en el resultado final

de la conversión, por efecto de la ocupación continua del bus. El submódulo de

procesamiento __

atiende al CAD como respuesta a una solicitud de atención realizada mediante

la intermpción INTO,Por su parte el convertidor digital a analógico es aislado de los procesos

fisicos mediante circuitos operacionales conectados en una configuración de seguidores.

Procesamiento

...........

'PuertoI PI

qJ

-

Exhibidor

4

Decodificador

deteclado

...........

Teclado

Figura 3.5 Interfaz local.

La pantalla de cristal líquido es mapeada en memoria y es conectado a los buses que

entrega el submódulo de procesamiento y control. La pantalla de cristal líquido corresponde

al módulo AND491

I

El teclado por su parte es conectado a un decodiñcador de teclado matricial 74C922,

este decodificador tiene como entradas ocho líneas que corresponden a las 4 líneas de

columnas y a las 4 líneas de renglones del teclado; cuando una tecla es pulsada el

decodificador entrega un valor hexadecimal correspondiente a dicha tecla y activa una señal

3.4

'I

Capítulo 3

Desarrollo del hardware.

decodificador entrega un valor hexadecimal correspondiente a dicha tecla y activa una señal

que indica que hay un valor disponible en el decodificador. El teclado es conectado

directamente al puerto P1 del microcontrolador y puede ser atendido por verificación

constante o por interrupción. Figura 3.6.

FControlador

4

PI

1

I

,Decoder 4

14C922

disponible

Figura 3.6 Conexión de teclado.

3.2.5 Interfaz serie.

El módulo de control tiene la capacidad de comunicarse con una PC mediante el

canal serie propio del microcontrolador a través de los terminales RXD y TXD. Estos

terminales son conectados a una interfaz serie MAX232 fabricado por Maxim, para adecuar

'I

los niveles entre l T L y el estándar RS-232. Figura 3.7.

...................................................................

.

Figura 3.7 Diagrama de la interfaz serie.

3.2.6 Interfaz E/S digitales.

El módulo controlador cuenta con 7 canales de entrada y 7 canales de salida digitales

(canales O a 6, opcionales) implementados por un buffer 74HC244 y un latch 74HC373,

respectivamente. El octavo canal de ambos circuitos, es interconectado igual que en el caso

de la interfaz analógica, para el diagnóstico del submódulo. La interfaz de entrada puede

activar la interrupción NT1 para solicitar atención del microcontrolador. Tanto los canales

de entrada como los de salida se encuentran mapeados en memoria, Figura 3.8.

~

3.5

4

,

Capítulo 3

r--- 1

L

Desarrollo del hardware.

Buffer d e

entrada

Procesamiento

n

y control

I

Figura 3.8 Interfaz de E/S digitales.

3.2.7 Generadores de PWM.

El módulo de control también cuenta con tres generadores de PWM trifásicos

opcionales que son incluidos para que el módulo pueda ser fácilmente aplicable al control de

sistemas con inversores como en el caso del control de motores eléctricos. El diagrama a

bloques de los generadores de PWM se presenta en la Figura 3.9. El submódulo generador de

PWM, consta principalmente de un circuito HEF4752 (fabricado por Philips) que genera una

señal PWM trifásica, este circuito utiliza principalmente como entradas dos señales

cuadradas que representan la frecuencia y el voltaje de la señal modulada generada. Los

valores de voltaje y frecuencia de la señal generada varían de acuerdo a las frecuencias de las

señales aplicadas al circuito.