library ieee

Anuncio

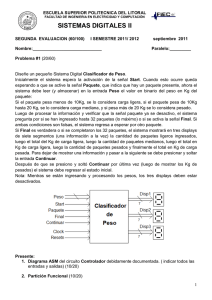

CODIGO VHDL library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY secuencia IS Port ( reloj : reset : habent : habsal : cuentamax: selec: anodos: Display7 : in std_logic; in std_logic; in std_logic; out std_logic; in std_logic_vector (2 downto 0); in std_logic_vector (2 downto 0); out std_logic_vector (2 downto 0); out std_logic_vector (6 downto 0)); END secuencia; ARCHITECTURE Comportamiento OF secuencia IS SIGNAL clock: std_logic; SIGNAL MiSecuencia: std_logic_vector (2 downto 0); BEGIN PROCESS(reloj) variable cuenta_pasos : integer range 0 to 9 :=0; BEGIN if reloj = '1' and reloj'event then if cuenta_pasos = 9 then cuenta_pasos :=0; clock <='1'; else cuenta_pasos:=cuenta_pasos+1; clock<='0'; end if; end if; END PROCESS; PROCESS (cuentamax,clock, reset) variable cuenta: std_logic_vector (2 downto 0):="000"; BEGIN IF reset = '1' then MiSecuencia<="000"; ELSIF clock='1' and clock'event then if habent='0' then if MiSecuencia = cuentamax then MiSecuencia<="000"; else if MiSecuencia = "000" then MiSecuencia<="001"; elsif MiSecuencia = "001" then MiSecuencia<="011"; elsif MiSecuencia = "011" then MiSecuencia<="101"; elsif MiSecuencia = "101" then MiSecuencia<="111"; elsif MiSecuencia = "111" then MiSecuencia<="010"; elsif MiSecuencia = "010" then MiSecuencia<="100"; elsif MiSecuencia = "100" then MiSecuencia<="110"; end if; end if; end if; END IF; IF MiSecuencia=cuentamax AND habent = '0' AND clock = '1' THEN habsal<='0'; ELSE habsal<='1'; END IF; END PROCESS; WITH MiSecuencia SELECT Display7<="0000000" WHEN "000", "1111001" WHEN "001", "0110000" WHEN "011", "0010010" WHEN "101", "1111000" WHEN "111", "0100100" WHEN "010", "0011001" WHEN "100", "1111101" WHEN "110", "1000000" when others; anodos<=selec; END Comportamiento; CODIGO VHDL (Por mapeo) library ieee; use ieee.std_logic_1164.all; ENTITY Secuencia IS END Secuencia; ARCHITECTURE Prueba OF Secuencia IS COMPONENT UNAD_Secuencia PORT( q0, q1,q2: OUT STD_LOGIC ); END COMPONENT; SIGNAL q0, q1, q2: std_logic := '0'; BEGIN UUT: UNAD_Secuencia port map(q0, q1, q2); q0 <= '0', '0' after 1 ns, '1' after 2 ns, '1' after 3 ns, '1' after 4 ns, '1' after 5 ns, '0' after 6 ns, '1' after 7 ns, '1' after 8 ns, '0' after 9 ns; q1 <= '0', '0' after 1 ns, '0' after 2 ns, '1' after 3 ns, '0' after 4 ns, '1' after 5 ns, '1' after 6 ns, '0' after 7 ns, '1' after 8 ns, '0' after 9 ns; q2 <= '0', '0' after 1 ns, '0' after 2 ns, '0' after 3 ns, '1' after 4 ns, '1' after 5 ns, '0' after 6 ns, '0' after 7 ns, '0' after 8 ns, '0' after 9 ns; END Prueba; Se puede observar la señal de salida que crea el binario necesario para crear la secuencia: Mapear en 1, 2, 3, 4, 5, 6, 7, 8 ns Como Segundos, con un bucle for o while no incluido para visualizar el mapeo en Simili: 1) 2) 3) 4) 5) 6) 7) 8) 0 0 0 1 1 0 1 1 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 0 CODIGO VHDL library ieee; use ieee.std_logic_1164.all; ENTITY Latch_SR IS END Latch_SR; ARCHITECTURE Prueba OF Latch_SR is COMPONENT UNAD_SR PORT( s, r: in std_logic; q: out std_logic ); END COMPONENT; signal s, r: std_logic; signal q: std_logic := '0'; BEGIN UUT: UNAD_SR port map(s, r, q); s <= '0', '1' after 8 ns, '0' after 18 ns, '1' after 26 ns, '0' after 36 ns; r <= '0', '1' after 18 ns, '0' after 24 ns, '1' after 40 ns, '0' after 47 ns; q <= '0', '1' after 8 ns, '0' after 18 ns, '1' after 26 ns, '0' after 40 ns; END Prueba; Inicio de la simulación Evidencia de carga y compilación del código Señal de salida Línea de tiempo según Requerimiento Formas de onda agregadas a las señales Evidencia de simulación