Examen de Arquitectura de Computadores (I. Telecomunicación)

Anuncio

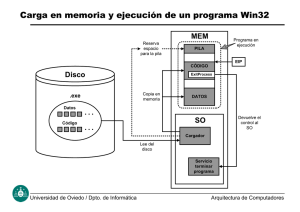

Examen de Arquitectura de Computadores (I. Telecomunicación) Convocatoria de febrero (19-2-2002) Escuela Politécnica. Universidad de Alcalá Duración aproximada: 2 horas. Problema 1 Se pretende diseñar el planificador de procesador para el nuevo sistema operativo VenanciOS. Para ello se ha pensado en un algoritmo expulsivo con prioridades dinámicas comprendidas entre 0 y 31 en las que los números bajos indican prioridad baja y los altos prioridad alta. Los procesos parten siempre de una prioridad fija de valor 15. Si el proceso agota su quantum, su prioridad disminuye en una unidad (como mínimo hasta el valor 0) y si el proceso no lo agota y es expulsado, se mantiene con la misma prioridad. Si el proceso se duerme a la espera de un recurso, al despertarse incrementa su prioridad (boost), dependiendo del tipo de recurso, acorde con la tabla siguiente: Recurso R1 R2 R3 R4 Incremento de prioridad 1 2 3 4 Notas: El incremento de prioridad se aplica a la prioridad con la que el proceso se durmió. Si dos o más procesos se bloquean en el mismo recurso, éstos serán atendidos en orden FIFO. El sistema utiliza un valor de quantum de 2 unidades de tiempo. Un proceso que pasa al estado de listo después de una espera, se encola al final de la cola correspondiente a su prioridad. Un proceso que es requisado por uno de mayor prioridad es encolado a la cabeza de la cola correspondiente a su prioridad. Un proceso que agota su quantum se encola al final de la cola correspondiente a su prioridad. Cuando un proceso requisado se reanuda, se le vuelve a asignar un quantum completo. La tabla siguiente muestra las ráfagas de CPU de los distintos trabajos así como el tiempo de acceso a cada dispositivo: Proceso P1 P2 P3 P4 CPU 5 1 6 1 E/S 4 R4 6 R2 7 R2 12 R1 CPU 3 7 5 3 E/S 5 R1 14 R2 10 R2 6 R1 CPU 1 1 1 3 Se debe suponer que todos los trabajos llegan en el instante 0, en el orden P 1 , P2 , P3 y P4 . Se pide: 1. Dibuje en la gráfica adjunta qué trabajo se ejecuta en cada momento así como su prioridad. 2. Muestre en la misma gráfica por qué recurso espera cada proceso en cada instante. 1 3. ¿Cuál es el primer instante de tiempo en que se desencadena por primera vez los siguientes escenarios? a) b) c) d) e) Finalización del quantum. Requisa después de una E/S. Boost. Decremento de prioridad. Espera después de una E/S. Problema 2 Suponga que dispone de un procesador similar al Pentium II en cuanto a sus mecanismos de gestión de memoria se refiere. En él la imagen del proceso en memoria desde el punto de vista de la segmentación es la que aparece en la siguiente figura: 00000000h 31 k CÓDIGO 34 k BDC 16 k PILA 63 k DATOS 40000000h 50000000h 70000000h C0000000h Los descriptores de segmento de código, datos y pila residen en la tabla de descriptores locales o LDT y ocupan las entradas 1, 2 y 3 respectivamente (la entrada 0 no se emplea y en caso de utilizarse debe generar un error). El descriptor de segmento de BDC reside en la tabla de descriptores globales o GDT y ocupa la entrada 1. La tabla LDT está cargada a partir de la posición 00007000h y la GDT a partir de la posición 00010000h. La diferenciación entre la LDT y la GDT la establece un bit del selector de segmento, el mismo que el empleado en el Pentium, de tal modo que si el bit vale 0 se utilizará la GDT y si vale 1 la LDT. El nivel de privilegio de los descriptores de código, datos y pila vale 11b y el de BDC 10b. En este sistema también se encuentra activado el mecanismo de paginación y las distintas páginas de cada segmento residen en los marcos indicados en la siguiente tabla: Tipo Código Datos Pila BDC Marcos 4000, 40A0, -, -, 17, 10A, 20B, 100C 1001, 1002, 1003, -, 1004, -, -, -, -, -, -, -, -, 1005, -, 1006 20F0, -, -, 3000, 3001, -, -, 3002, 3003, 3004, 3005, - El directorio de páginas está en el marco 20h y las tablas de código, datos, pila y BDC residen en los marcos 30h, 40h, 50h y 60h respectivamente. Los guiones “-” indican que la página no se encuentra presente en memoria principal. 2 1. Con los datos aportados rellene en la hoja adjunta todas las tablas indicadas así como el valor de los diferentes selectores. 2. ¿A qué direcciones físicas corresponden las siguientes direcciones virtuales? a) 000F - 00001ABC b) 0017 - 00003A00 c) 0017 - 00013B80 d) 00FF - 0000FFFF e) 001F - 0000A010 f ) 000A - 00004B58 g) 000B - 00001000 h) 0007 - 12344321 NOTA: todas las direcciones, mientras no se indique lo contrario, están expresadas en hexadecimal. 3 4 Examen de Arquitectura de Computadores (I. Telecomunicación) Convocatoria de febrero (19-2-2002) Escuela Politécnica. Universidad de Alcalá APELLIDOS................................................................................................................................. NOMBRE......................................................................................DNI......................................... 5 R4 R3 R2 R1 11 12 13 14 15 16 17 18 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 Problema 1 6 Examen de Arquitectura de Computadores (I. Telecomunicación) Convocatoria de febrero (19-2-2002) Escuela Politécnica. Universidad de Alcalá APELLIDOS................................................................................................................................. NOMBRE......................................................................................DNI......................................... Problema 2 LDT GDT Directorio de páginas Selector de código Selector de datos Selector de pila Selector de BD TDP código TDP datos 7 TDP pila Dirección virtual Segmento LDT/GDT TDP BD Privilegio selector 8 Página Marco Dirección física