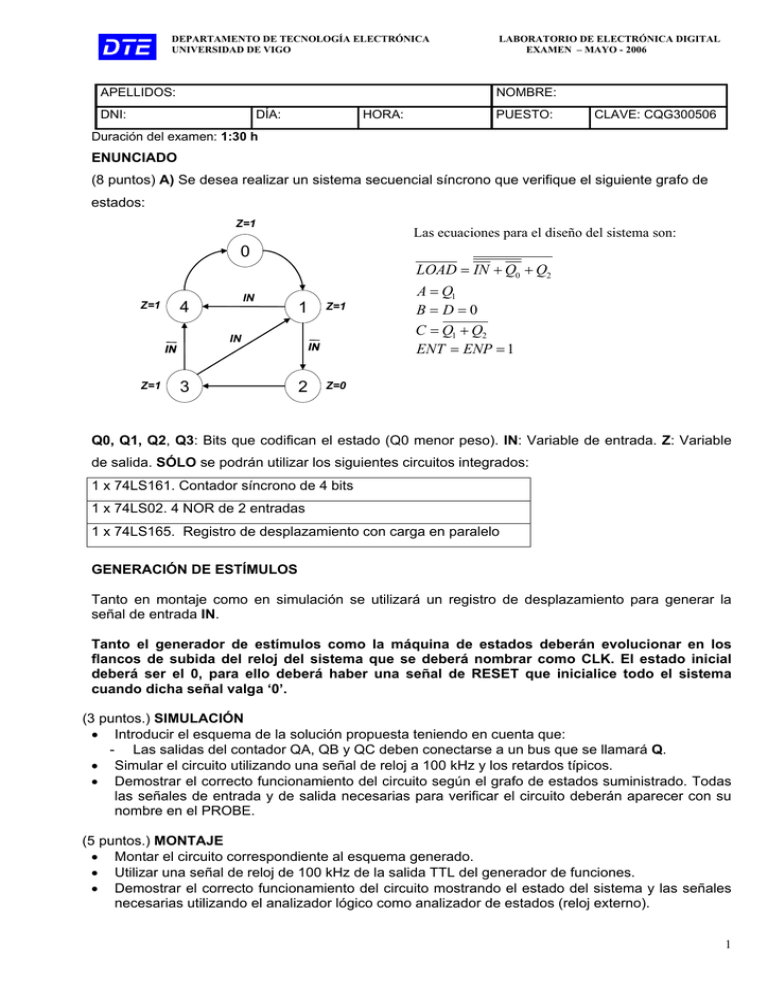

Q Q IN LOAD + + = QQC + =

Anuncio

DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA UNIVERSIDAD DE VIGO APELLIDOS: LABORATORIO DE ELECTRÓNICA DIGITAL EXAMEN – MAYO - 2006 NOMBRE: DNI: DÍA: HORA: PUESTO: CLAVE: CQG300506 Duración del examen: 1:30 h ENUNCIADO (8 puntos) A) Se desea realizar un sistema secuencial síncrono que verifique el siguiente grafo de estados: Z=1 Las ecuaciones para el diseño del sistema son: 0 IN 4 Z=1 1 IN IN IN Z=1 3 Z=1 2 LOAD = IN + Q0 + Q2 A = Q1 B=D=0 C = Q1 + Q2 ENT = ENP = 1 Z=0 Q0, Q1, Q2, Q3: Bits que codifican el estado (Q0 menor peso). IN: Variable de entrada. Z: Variable de salida. SÓLO se podrán utilizar los siguientes circuitos integrados: 1 x 74LS161. Contador síncrono de 4 bits 1 x 74LS02. 4 NOR de 2 entradas 1 x 74LS165. Registro de desplazamiento con carga en paralelo GENERACIÓN DE ESTÍMULOS Tanto en montaje como en simulación se utilizará un registro de desplazamiento para generar la señal de entrada IN. Tanto el generador de estímulos como la máquina de estados deberán evolucionar en los flancos de subida del reloj del sistema que se deberá nombrar como CLK. El estado inicial deberá ser el 0, para ello deberá haber una señal de RESET que inicialice todo el sistema cuando dicha señal valga ‘0’. (3 puntos.) SIMULACIÓN • Introducir el esquema de la solución propuesta teniendo en cuenta que: - Las salidas del contador QA, QB y QC deben conectarse a un bus que se llamará Q. • Simular el circuito utilizando una señal de reloj a 100 kHz y los retardos típicos. • Demostrar el correcto funcionamiento del circuito según el grafo de estados suministrado. Todas las señales de entrada y de salida necesarias para verificar el circuito deberán aparecer con su nombre en el PROBE. (5 puntos.) MONTAJE • Montar el circuito correspondiente al esquema generado. • Utilizar una señal de reloj de 100 kHz de la salida TTL del generador de funciones. • Demostrar el correcto funcionamiento del circuito mostrando el estado del sistema y las señales necesarias utilizando el analizador lógico como analizador de estados (reloj externo). 1 DEPARTAMENTO DE TECNOLOGÍA ELECTRÓNICA UNIVERSIDAD DE VIGO LABORATORIO DE ELECTRÓNICA DIGITAL EXAMEN – MAYO - 2006 (2 puntos.) B) Generar una salida digital de 1 bit denominada Z. La salida Z debe tomar el valor ‘1’ en todos los estados exceptuando el estado 2. Para generar esta salida se deben utilizar las puertas NAND del CI 74LS00. (1 puntos.) SIMULACIÓN: • Introducir en el esquema del apartado A) la generación de la señal de salida Z. • Simular el circuito utilizando una señal de reloj a 100 kHz y los retardos típicos. • Demostrar el correcto funcionamiento del circuito y la correcta generación de la señal de salida. (1 puntos.) MONTAJE: • Añadir al montaje del apartado A) la parte correspondiente a la generación de la señal de salida Z. • Utilizar una señal de reloj de 100 kHz de la salida TTL del generador de funciones. • Demostrar el correcto funcionamiento del circuito (mostrando el estado del sistema y las señales necesarias) utilizando el analizador lógico como analizador de estados (reloj externo). RESULTADOS QUE SE DEBEN ENTREGAR JUNTO CON ESTA HOJA DE ENUNCIADO • Hoja(s) impresa(s) del esquema. • Hoja(s) impresa(s) con los resultados de la simulación. • Hoja(s) impresa(s) con los resultados del analizador lógico. EN GRÁFICAS DE SIMULACIÓN Y DEL ANALIZADOR SE DEBEN MOSTRAR EL CONJUNTO DE SEÑALES MÁS IDÓNEO Y DE LA FORMA MÁS APROPIADA PARA COMPROBAR EL CORRECTO FUNCIONAMIENTO DEL SISTEMA. 2