Guía Trabajo Práctico Número 6

Anuncio

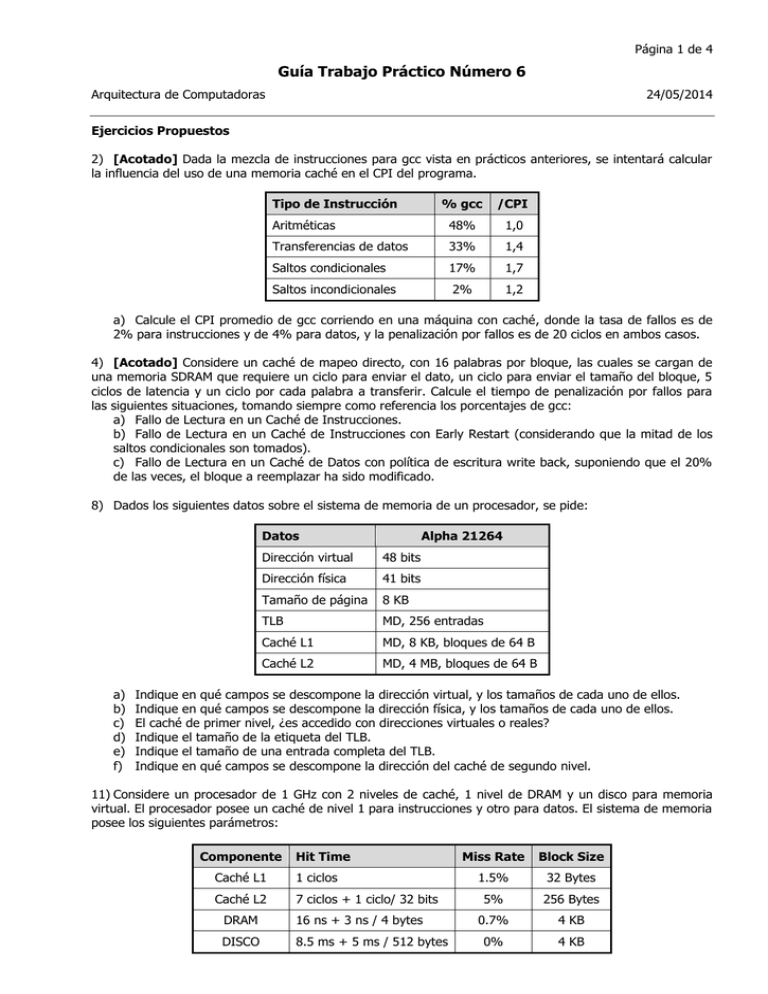

Página 1 de 4 Guía Trabajo Práctico Número 6 Arquitectura de Computadoras 24/05/2014 Ejercicios Propuestos 2) [Acotado] Dada la mezcla de instrucciones para gcc vista en prácticos anteriores, se intentará calcular la influencia del uso de una memoria caché en el CPI del programa. Tipo de Instrucción % gcc /CPI Aritméticas 48% 1,0 Transferencias de datos 33% 1,4 Saltos condicionales 17% 1,7 Saltos incondicionales 2% 1,2 a) Calcule el CPI promedio de gcc corriendo en una máquina con caché, donde la tasa de fallos es de 2% para instrucciones y de 4% para datos, y la penalización por fallos es de 20 ciclos en ambos casos. 4) [Acotado] Considere un caché de mapeo directo, con 16 palabras por bloque, las cuales se cargan de una memoria SDRAM que requiere un ciclo para enviar el dato, un ciclo para enviar el tamaño del bloque, 5 ciclos de latencia y un ciclo por cada palabra a transferir. Calcule el tiempo de penalización por fallos para las siguientes situaciones, tomando siempre como referencia los porcentajes de gcc: a) Fallo de Lectura en un Caché de Instrucciones. b) Fallo de Lectura en un Caché de Instrucciones con Early Restart (considerando que la mitad de los saltos condicionales son tomados). c) Fallo de Lectura en un Caché de Datos con política de escritura write back, suponiendo que el 20% de las veces, el bloque a reemplazar ha sido modificado. 8) Dados los siguientes datos sobre el sistema de memoria de un procesador, se pide: Datos a) b) c) d) e) f) Alpha 21264 Dirección virtual 48 bits Dirección física 41 bits Tamaño de página 8 KB TLB MD, 256 entradas Caché L1 MD, 8 KB, bloques de 64 B Caché L2 MD, 4 MB, bloques de 64 B Indique en qué campos se descompone la dirección virtual, y los tamaños de cada uno de ellos. Indique en qué campos se descompone la dirección física, y los tamaños de cada uno de ellos. El caché de primer nivel, ¿es accedido con direcciones virtuales o reales? Indique el tamaño de la etiqueta del TLB. Indique el tamaño de una entrada completa del TLB. Indique en qué campos se descompone la dirección del caché de segundo nivel. 11) Considere un procesador de 1 GHz con 2 niveles de caché, 1 nivel de DRAM y un disco para memoria virtual. El procesador posee un caché de nivel 1 para instrucciones y otro para datos. El sistema de memoria posee los siguientes parámetros: Componente Hit Time Caché L1 1 ciclos Caché L2 7 ciclos + 1 ciclo/ 32 bits DRAM 16 ns + 3 ns / 4 bytes DISCO 8.5 ms + 5 ms / 512 bytes Miss Rate Block Size 1.5% 32 Bytes 5% 256 Bytes 0.7% 4 KB 0% 4 KB Guía Trabajo Práctico Número 6 Página 2 de 4 Por último considere que el caché de nivel L1 trabaja con direcciones reales, es decir que primero se accede a un TLB que tiene un tiempo de acceso de 1 ciclo, que falla 0,1% de las veces y que requiere una lectura de 4 bytes de la DRAM para actualizarse (estos accesos no pueden fallar). a) ¿Cuál es el tiempo medio de acceso a memoria para instrucciones y para datos? b) Suponiendo que todos los accesos a datos son lecturas, ¿cuánto es el CPI promedio de gcc? Soluciones Propuestas 2) La idea de este ejercicio es mostrar la influencia de los fallos en el cálculo del CPI. Hasta ahora habíamos supuesto siempre una memoria ideal, y habíamos obtenido en el mejor de los casos un CPI de 1.255 en el procesador segmentado. Pero cuando las memorias dejan de ser ideales, y se convierten en cachés, su tiempo de acceso sigue siendo de un ciclo, pero sólo cuando hay un acierto. Cuando ocurre un fallo de caché, el procesador no puede continuar realizando ninguna tarea, y se detiene completamente hasta que el fallo es resuelto. Por este motivo es que la cantidad de ciclos que el procesador pierde a causa de los fallos de caché debe sumarse al CPI. CPI = CPIideal + Paradas por fallos Las paradas por fallos se calculan como la cantidad de ciclos que pierdo cada vez que tengo un fallo (penalidad) multiplicado por la cantidad de veces que este evento ocurre (tasa de fallos). Paradas por fallos = m * Pf Además, no debemos olvidar que el procesador segmentado posee dos cachés separados, uno para instrucciones y uno para datos, y que cada uno de ellos puede influir de diferente manera, según la cantidad de veces que es accedido, pero ambos provocarán paradas. Paradas por fallos = %refInstr * mInstr * PfInstr + %refDatos * mDatos * PfDatos Con estas ecuaciones, simplemente reemplazamos las variables con los datos proporcionados por el enunciado: Paradas por fallos = 100% * 2% * 20 + 33% * 4% * 20 = 0.4 + 0.264 = 0.664 CPI = 1.255 + 0.664 = 1.919 Es muy importante destacar que este resultado implica que los fallos de caché incrementan en más de un 50% el CPI promedio de un procesador, y esto es considerando penalidades que no son tan reales. 4) Este ejercicio es similar al anterior, pero ahora vamos a tener que calcular la penalidad en caso de fallo. a) En el caso de producirse un fallo en la caché de instrucciones, voy a tener que traer todo un bloque, por lo que la penalización será la suma de los ciclos para enviar el dato (1 ciclo), más los ciclos para enviar el tamaño del bloque (1 ciclo), más los ciclos de latencia (5 ciclos), más la cantidad para transferir todo el bloque (16 ciclos, 1 por cada palabra). El tiempo total es: T = 1 + 1 + 5 + 16 * 1 = 23 ciclos b) Early restart es una técnica que se utiliza para disminuir la penalización por fallos en cachés que tienen bloques de más de una palabra. Básicamente, consiste en que se empieza a llenar el bloque por la primera palabra y se devuelve el control al procesador apenas llega la palabra solicitada, no cuando termine de llenarse todo el bloque, como es usual. De esta manera, suponiendo accesos secuenciales (normales en las instrucciones), cuando pida la primera palabra de un bloque será un fallo, pero cuando pida la segunda tendré un acierto. Si extendemos este supuesto, vemos que sólo se fallará al solicitar la primera palabra de un bloque, por lo tanto la penalidad sería la de traer solamente la primera palabra. Pero no todas las instrucciones son secuenciales. Las secuenciales son las aritméticas (48%) y las de transferencia de datos (33%). Los saltos incondicionales no son secuenciales, y suponemos que la mitad de los saltos condicionales sí lo son. Esto nos da que el 89.5% de las instrucciones son secuenciales, por Guía Trabajo Práctico Número 6 Página 3 de 4 lo que les corresponde la penalidad de traer la primera palabra de un bloque. Esta sería de 1+1+5+1, o sea de 8 ciclos. Para el resto de instrucciones (10.5%), les puede tocar cualquier palabra dentro del bloque (incluida la primera), por lo que tomamos un promedio: (8+9+10+…+23) / 16, que se puede reducir algebraicamente a (8 + 23) / 2 = 15.5 ciclos. Finalmente, T = 0.895 * 8 + 0.105 * 15.5 = 8.7875 ciclos c) En un caché de tipo write-back, los bloques que son modificados no se escriben en memoria hasta que les llega el momento de ser reemplazados. Entonces, en el caso de que se produzca un fallo de caché la penalidad puede verse incrementada si es que el bloque que va a ser reemplazado ha sido modificado previamente. En este caso, podría decirse que la penalidad es doble: se paga una vez para escribir en memoria el bloque modificado, y luego otra vez para traer el bloque solicitado. Entonces, el 80% de las veces la penalidad es la de traer todo un bloque: 23 ciclos. Y el 20% restante la penalidad es doble, por lo que el tiempo total sería: T = 0.8 * 23 + 0.2 * 2 * 23 = 27.6 ciclos La ecuación anterior puede reducirse algebraicamente, y expresarse como T = (1 + 0.2) * 23, lo cual es una manera más sencilla de calcular el tiempo. 8) a) La dirección virtual se descompone en dos campos: el número de página virtual y el Offset de página. Como las páginas son de 8 KB son necesarios 13 bits para el Offset, y el resto (35 bits) se usan para el número de página. b) La dirección física se descompone en dos campos: el número de marco y el Offset de página. El Offset es el mismo que el de la dirección virtual, por lo que también es de 13 bits, quedando 28 bits para el número de marco. c) Para saber si el caché L1 puede ser accedido con direcciones virtuales, tengo que encontrar cómo se descompone su dirección, y controlar que la cantidad de bits necesarios para identificar un bloque (o sea el índice más el desplazamiento) sea menor o igual que la cantidad de bits del Offset de página. Si no se cumple esta condición el caché L1 sólo podrá ser accedido con direcciones reales. Como el caché tiene bloques de 64 bytes, son necesarios 6 bits para indicar el desplazamiento. Como es de mapeo directo, tendrá en total (8 KB / 64 B) = 128 bloques, por lo que se necesitan 7 bits para indicar el índice. O sea que en total son necesarios 7 + 6 = 13 bits para indexar un bloque de caché, y como dijimos anteriormente el Offset de página es de 13 bits, por lo que puede accederse al caché con direcciones virtuales. d) Teniendo en cuenta los resultados obtenidos en el apartado a, el número de página de la dirección virtual tiene 35 bits. Además como el TLB es de mapeo directo, y tiene 256 entradas, son necesarios 8 bits para su índice y el resto de los bits se usan para la etiqueta, por lo que la misma es de 35 – 8 = 27 bits. e) Una entrada completa de TLB posee tres campos: bits de estado, la etiqueta a comparar y el número de marco a devolver en caso de acierto. Por lo tanto considerando los resultados obtenidos en los apartados anteriores, y que usamos 4 bits de estado, su tamaño total es de 4 + 27 + 28 = 59 bits. f) Al caché L2 se accede con direcciones reales (de 41 bits), y a esta dirección se la divide en tres campos: etiqueta, índice y desplazamiento. Como los bloques son de 64 bytes, se necesitan 6 bits para el desplazamiento. Como el tamaño es de 4 MB, y es de mapeo directo, tiene en total (4 MB / 64 B) = 64K bloques, por lo que se necesitan 16 bits de índice. El resto de los 41 bits se utiliza como etiqueta, o sea 41 – 16 – 6 = 19 bits. Por lo tanto podemos descomponer la dirección del caché L2 como etiqueta (19 bits), índice (16 bits) y desplazamiento (6 bits). 11) Teniendo en cuenta que el procesador es de 1 GHz podemos calcular el período que será T = 1 ns. a) Para poder calcular el tiempo medio de acceso al sistema de memoria completo debemos comenzar por el último nivel, en este caso el disco. Esto se debe a que los tiempos de acceso de los niveles inferiores se van agrupando y formando la penalización de los niveles superiores. Guía Trabajo Práctico Número 6 Página 4 de 4 Para calcular los tiempos de acceso generalmente debemos considerar en primer lugar el tiempo de hit, el mismo esta compuesto por un tiempo fijo y un tiempo de transferencia de datos. Este último es el tiempo necesario para que la unidad que se esta analizando envíe los datos al nivel superior y se calcula teniendo en cuenta la tasa de transferencia del nivel actual y el tamaño de bloque de la unidad del nivel anterior. Además para las unidades que tienen un nivel por debajo, y por lo tanto tienen una tasa de fallos distinta de cero, debemos adicionar la tasa de fallos por la penalidad, la misma será igual al tiempo de acceso del nivel que está por debajo del nivel analizado. De este modo para calcular el tiempo de acceso del disco debemos tener en cuenta los 8.5 ms que serían el tiempo de acceso fijo, y además, sabiendo que debemos transferir un bloque completo a la DRAM, y que los bloques de la DRAM tienen 4 KB, adicionamos el tiempo de transferencia del disco para enviar esta información teniendo en cuenta que la tasa de transferencia es 512 bytes cada 5 ms. Dado que el disco no tiene un nivel por debajo, la tasa de fallos es cero por lo que no se adiciona ninguna penalidad. AMAT(Disco) = 8.5 ms + 5 ms x (4 KB / 512 bytes) = 8.5 ms + 5 ms x 8 = 48.5 ms Una vez calculado el tiempo de acceso del disco, subimos un nivel para calcular el tiempo de acceso de la DRAM. En este caso, debemos tener en cuenta los 16 ns de acceso, más el tiempo de transferencia de un bloque de caché L2 a una tasa de transferencia de 4 bytes cada 3 ns. Como la DRAM posee un nivel por debajo (el disco) la misma tiene una tasa de fallos distinta de cero, por lo que deberemos adicionar la tasa de fallos por la penalidad de fallo, teniendo en cuenta que esta penalidad será igual al tiempo de acceso del nivel inferior, es decir, del disco. AMAT(DRAM) = 16 ns + 3 ns * (256 bytes / 4 bytes) + 0.007 * 48.5 ms AMAT(DRAM) = 208 ns + 339500 ns = 339708 ns = 339708 T Al analizar el tiempo de acceso del cache L2 contamos los 7 ciclos de acceso más las transferencia de 32 bytes al caché L1 con una tasa de transferencia de 32 bits (4 bytes) cada ciclo. También adicionamos la penalidad (tiempo de acceso de la DRAM) por la tasa de fallos del cache L2. AMAT(L2) = 7T + 1T * (32 bytes/4 bytes) + 0.05 * 339708 ns AMAT(L2) = 15T + 16985T = 17000 T El último nivel de memoria es la caché L1 y el tiempo de acceso a la misma será igual el tiempo de acceso (1T) más la tasa de fallos por la penalidad de fallos (tiempo de acceso a caché L2). Para este caso en particular en el cual se accede primero al TLB para la traducción de las direcciones, debemos adicionar el retardo provocado tanto por el acceso al TLB como por la falla del mismo, el cual será igual al tiempo requerido por la DRAM para transferir 4 bytes, teniendo en cuenta que la misma no puede fallar. AMAT(L1) = 1T + 0.015 * 17000T+ 1 + 0.001 * (16 ns +3 ns) AMAT(L1) = 1T + 255T+ 1 + 0.001 * 19T = 257 T Por lo tanto el tiempo medio de acceso a memoria tanto para instrucciones como para datos en el sistema de memoria completo será igual a 257 T. b) Para calcular el CPI promedio de gcc, tomamos como base el CPI ideal calculado en prácticos anteriores 1,255 y al mismo le adicionamos los ciclos medios requeridos para acceder a memoria. Si tenemos en cuenta que todas las instrucciones acceden a memoria de instrucciones y que el 33% de las instrucciones (instrucciones de transferencia) acceden a memoria de datos (en este caso con la simplificación de que todos estos accesos son lecturas), y considerando el tiempo medio de acceso calculado en el apartado anterior podemos calcular el nuevo CPI promedio. CPI = CPI ideal + ref * (AMAT(L1) – Hit Time(L1)) CPI = 1,255 + 1,33 x (257 - 1) CPI = 1,255 + 340,48 = 341,735 Por lo tanto el CPI promedio para gcc considerando los accesos a memoria será 341,735. Como se puede observar, este nuevo CPI es casi 300 veces mayor que el ideal, así que pueden darse cuenta del tremendo impacto en la performance que agrega la jerarquía de memoria, y cuánta importancia toma la multiprogramación para poder realizar otras tareas mientras se resuelven los fallos de página.