Memoria Externa

Anuncio

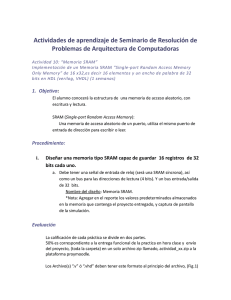

Memoria Externa Diseño de Sistemas con FPGA Patricia Borensztejn 1er cuatrimestre 2009 Esto es para que tengan una pequeña idea de cómo hacer un controlador para la memoria externa. Los que necesiten mas profundidad, consultar el libro, y/o a Maxi! Memoria Asíncrona • La placa S3 trae incorporados dos bloques de memoria estática SRAM asíncrona. Cada uno de los bloques es de 256K por 16. O sea que, en total hay 1M byte de almacenamiento externo en la placa de desarrollo. • El hecho de que la memoria sea asíncrona, significa que el chip no posee una señal de reloj, por lo tanto no puede sincronizarse con un sistema síncrono trivialmente. Será necesario entonces, construir un “envoltorio” (wrapper) para que la memoria pueda verse y accederse como un sistema síncrono. FPGA --- SRAM Descripción de las señales y funcionamiento del Módulo • • Además de especificar el funcionamiento de las señales de control, el módulo de memoria especifica los tiempos necesarios para poder realizar exitosamente las operaciones de lectura y escritura. El controlador debe generar las señales correspondientes respetando los tiempos del módulo de memoria. Lectura • Diagrama de tiempo para el caso: – el chip está siempre seleccionado, es decir, las señales CE,OE están activas, y también alguno o los dos buses de 8 bits (UB,LB) • El ciclo de memoria está guiado por las señales de dirección únicamente. • Tiempos involucrados: – tRC: (read cycle time) : tiempo entre dos lecturas – tAA: (address access time) : tiempo requerido para obtener una salida estable después de un cambio en las señales de dirección. – tOHA: (output hold time) tiempo durante el cual la salida se mantiene válida luego de un cambio en las señales de dirección. Lectura Lectura, caso general • Otros tiempos involucrados: – tDOE: (output enable access time) tiempo requerido para obtener datos válidos después de que se activa la señal OE_N – tHZOE: (output enable to high Z time) tiempo necesario para que el buffer tri estado entre en alta impedancia después de que OE_N se desactiva. – tLZOE: (output enable to low Z time) tiempo necesario para que el buffer tri estado deje el estado de alta impedancia después de que OE_N se activa. Escritura • Tiempos involucrados: – tWC: (write cycle time) mínimo tiempo que puede transcurrir entre dos operaciones de escritura – tSA: (address setup time) mínimo tiempo durante el cual deben estar estables las señales de dirección antes de activar la señal WE_N – tHA: (address hold time) mínimo tiempo durante el cual deben estar estables las señales de dirección despues que se desativa la señal WE_N – tPWE1: (WE_N pulse width) tiempo mínimo del pulso – tSD: (Data Setup Time) mínimo tiempo durante el cual hay que mantener las señales de datos antes de que WE_N pase de 0 a 1 – tSD: (Data Hold Time) mínimo tiempo durante el cual hay que mantener las señales de datos despues que WE_N pase de 0 a 1 Escritura Controlador Básico • Señales al Main System: – – – – mem: se activa al iniciarse una operación de memoria rw: especifica rd(1) o write(0) addr: dirección de 18 bits data_f2s: dato de 16 bits a ser escrito en la SRAM (FPGA to SRAM) – data_s2fr: dato de 16 bits registrado recibido de la SRAM – data_s2f: dato de 16 bits recibido de la SRAM – Ready: controlador puede iniciar nuevo comando Data Path del Controlador • El DP contiene: – Un registro para la direccion – Dos registros para los datos • El Control (FSM) genera las señales: – – – – we_n oe_n ready en (uno para cada uno de los tres registros) – tri_n : controla la dirección de los datos Ciclo de Memoria para leer • Colocar la dirección en el bus y activar OE_N Esperar al menos tAA Obtener el dato del bus de Datos y desactivar OE_N • • • • iddle • rd1 El estado rd1 pondrá la señal OE_N activa, y la dirección en el bus de direcciones. Estas dos señales se cargan al pasar de iddle a rd1. Las señales estan activas durante 20nseg, al final del estado leemos la entrada en el registro data_s2f_r Volvemos a Iddle. La señal OE_N se desactiva. Ciclo de Memoria para escribir 1. Colocar la dirección en el bus addr, colocar los datos en el registro data_f2s, activar we_n y tri_n. Bajar la señal we_n (porque la memoria usa el flanco de subida de la señal we_n para leer los datos) pero mantener la señal tri_n para garantizar que lleguen los datos Volver a Iddle, donde se pone tri_n a cero 2. 3. iddle wr1 1. 2. wr2 Escribimos en 40 nseg! Leemos en 20 nseg! Recomendaciones • Seguir muy atentamente las indicaciones del libro, que ofrece varias soluciones para acceder los módulos de memoria con diversos grados de eficiencia. • Consultar: – Hoja de datos de las memorias: documento 61LV25616AL.PDF (está en la página) – Libro – Maxi