Tema: MEMORIAS 1. Esquematice claramente, la

Anuncio

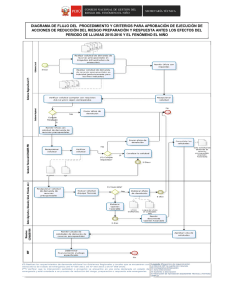

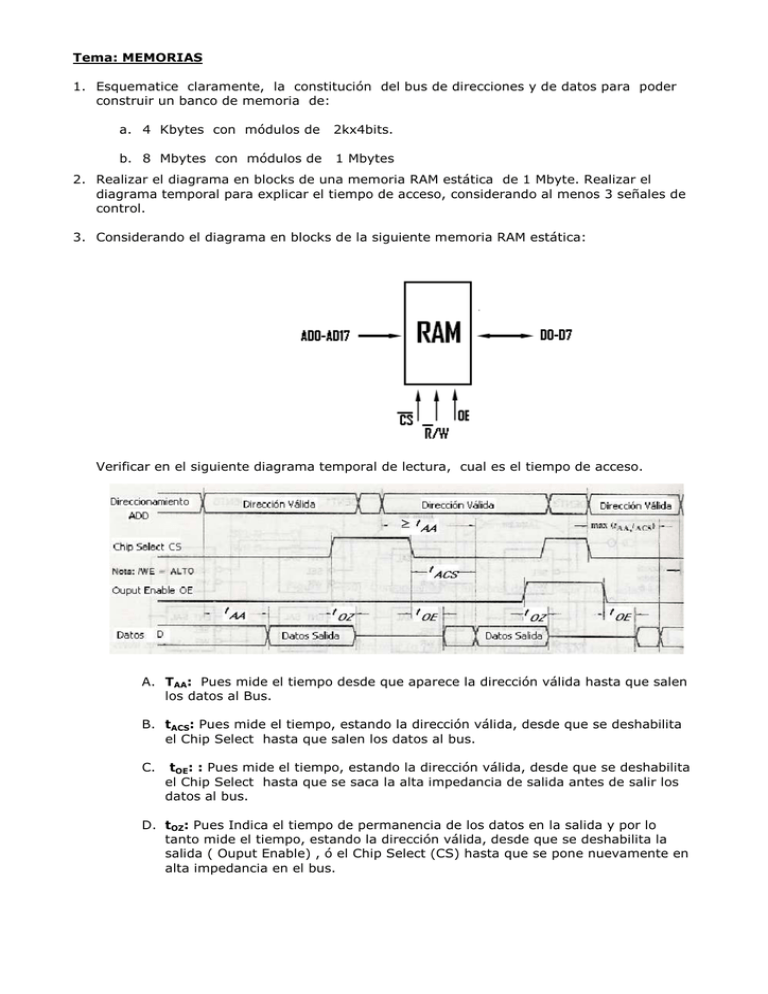

Tema: MEMORIAS 1. Esquematice claramente, la constitución del bus de direcciones y de datos para poder construir un banco de memoria de: a. 4 Kbytes con módulos de 2kx4bits. b. 8 Mbytes con módulos de 1 Mbytes 2. Realizar el diagrama en blocks de una memoria RAM estática de 1 Mbyte. Realizar el diagrama temporal para explicar el tiempo de acceso, considerando al menos 3 señales de control. 3. Considerando el diagrama en blocks de la siguiente memoria RAM estática: Verificar en el siguiente diagrama temporal de lectura, cual es el tiempo de acceso. A. TAA: Pues mide el tiempo desde que aparece la dirección válida hasta que salen los datos al Bus. B. tACS: Pues mide el tiempo, estando la dirección válida, desde que se deshabilita el Chip Select hasta que salen los datos al bus. C. tOE: : Pues mide el tiempo, estando la dirección válida, desde que se deshabilita el Chip Select hasta que se saca la alta impedancia de salida antes de salir los datos al bus. D. tOZ: Pues Indica el tiempo de permanencia de los datos en la salida y por lo tanto mide el tiempo, estando la dirección válida, desde que se deshabilita la salida ( Ouput Enable) , ó el Chip Select (CS) hasta que se pone nuevamente en alta impedancia en el bus. 4. Explique los siguientes conceptos: A : Memoria Interna B : Memoria central o principal. C : Memoria Secundaria. 5. Explique los siguientes parámetros de las memorias electrónicas. A: Unidad y capacidad de almacenamiento B: Tiempo de acceso. C: Estabilidad 6. Defina una memoria de acceso aleatorio. Indique cuales son sus siglas y los parámetros generales que la caracterizan. Realizar el diagrama en blocks. Indique cuantas lineas de cada tipo tiene una memoria de 128 Mbyte. 7. Defina una memoria de acceso secuencial. Indique cuales son sus siglas y los parámetros generales que la caracterizan. Realizar el diagrama en blocks. Indique cuantas líneas de cada tipo tiene una memoria de 128 Mbyte, organizada palabra a palabra. 8. Realizar un diagrama de flujo para indicar como se lee/escribe en una memoria de acceso secuencial. 9. Dibuje el esquema temporal de una memoria como la indicada en la figura. 10. Construir una memoria de 128 KBytes, con C.I de 32 Knibbles c/u. 11. Dibujar el esquema de una memoria LIFO cuya capacidad es de 12 bytes y se encuentra organizada palabra a palabra. Indicar el esquema funcional. 12. Que tipo de organización interna conoce de una memoria de acceso aleatorio; indiquelas brevemente. 13. Dibuje el elemento básico de una memoria de acceso aleatorio estática que se encuentra en una organización 3D. 14. Considerando la memoria RAM de la figura, dónde la primera y última dirección tienen grabada la información indicadas en el gráfico misma DCh y 83h. Indicar capacidad de la memoria, nombre y cantidad de líneas de n, m, p, q y r. 15. Construir una memoria de 256 Kpalabras de 2 Bytes c/u, con C.I de 64 Kbytes c/u. 16. Dibujar el esquema de una memoria FIFO cuya capacidad es de 8 bytes y se encuentra organizada bit a bit. Indicar el esquema funcional.