Modelo computacional de un modulador ∑

Anuncio

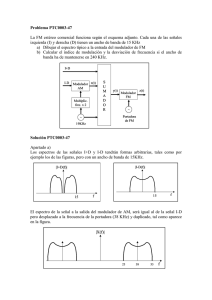

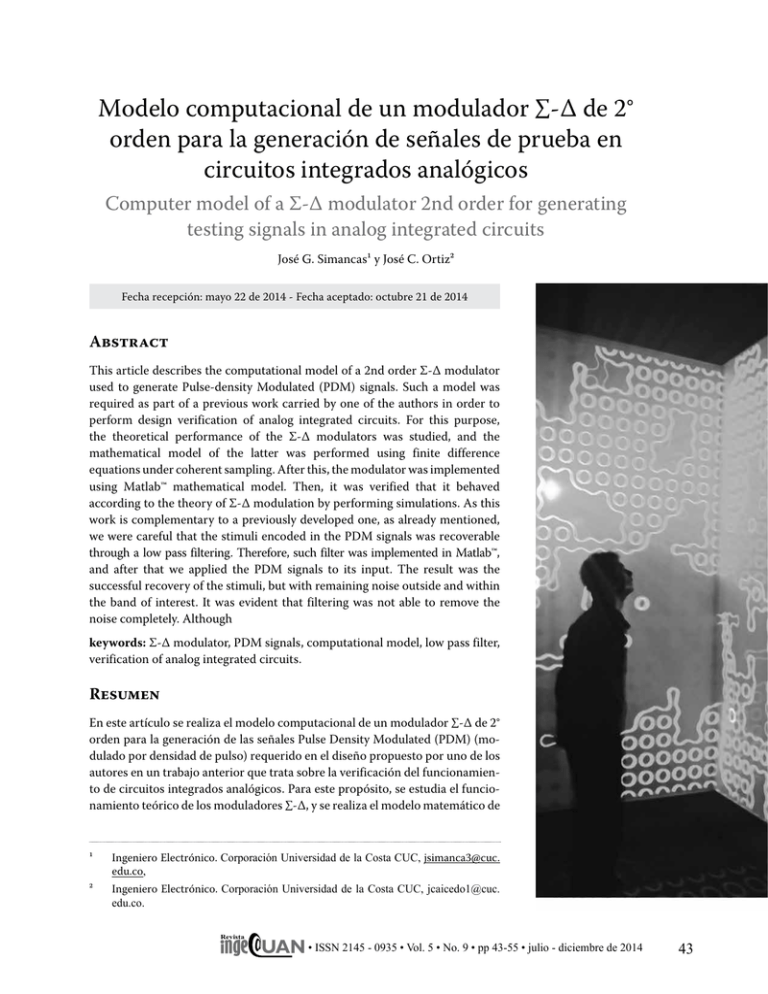

• José G. Simancas y José C. Ortiz • Modelocomputacionaldeunmodulador∑-∆de2° ordenparalageneracióndeseñalesdepruebaen circuitosintegradosanalógicos ComputermodelofaΣ-Δmodulator2ndorderforgenerating testing signals in analog integrated circuits JoséG.Simancas¹yJoséC.Ortiz² Fecharecepción:mayo22de2014-Fechaaceptado:octubre21de2014 Abstract Thisarticledescribesthecomputationalmodelofa2ndorderΣ-Δmodulator used to generate Pulse-density Modulated (PDM) signals. Such a model was requiredaspartofapreviousworkcarriedbyoneoftheauthorsinorderto perform design verification of analog integrated circuits. For this purpose, the theoretical performance of the Σ-Δ modulators was studied, and the mathematical model of the latter was performed using finite difference equationsundercoherentsampling.Afterthis,themodulatorwasimplemented using Matlab™ mathematical model. Then, it was verified that it behaved accordingtothetheoryofΣ-Δmodulationbyperformingsimulations.Asthis workiscomplementarytoapreviouslydevelopedone,asalreadymentioned, wewerecarefulthatthestimuliencodedinthePDMsignalswasrecoverable throughalowpassfiltering.Therefore,suchfilterwasimplementedinMatlab™, and after that we applied the PDM signals to its input. The result was the successfulrecoveryofthestimuli,butwithremainingnoiseoutsideandwithin the band of interest. It was evident that filtering was not able to remove the noisecompletely.Although keywords:Σ-Δmodulator,PDMsignals,computationalmodel,lowpassfilter, verification of analog integrated circuits. Resumen Enesteartículoserealizaelmodelocomputacionaldeunmodulador∑-∆de2° ordenparalageneracióndelasseñalesPulseDensityModulated(PDM)(moduladopordensidaddepulso)requeridoeneldiseñopropuestoporunodelos autoresenuntrabajoanteriorquetratasobrelaverificacióndelfuncionamientodecircuitosintegradosanalógicos.Paraestepropósito,seestudiaelfuncionamientoteóricodelosmoduladores∑-∆,yserealizaelmodelomatemáticode ¹ ² IngenieroElectrónico.Corporación Universidad de la Costa CUC, jsimanca3@cuc. edu.co, IngenieroElectrónico.Corporación Universidad de la Costa CUC, jcaicedo1@cuc. edu.co. Revista UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 43 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • esteúltimousandolasecuacionesendiferenciasfinitasenelmarcodelmuestreocoherente.Luegodeesto,secodificaenMatlab™elmodelomatemáticoy severificaquetalmodelosecomportaconformealateoríadelamodulación ∑-∆ mediante simulaciones. Debido a que este trabajo es complementario a uno desarrollado con anterioridad, como ya se mencionó, se debe verificar quelosestímulosqueestáncodificadosenlasseñalesPDMseanrecuperables medianteunfiltropasa-bajas,portanto,seimplementóelfiltroenMatlab™y seleaplicóalasseñalesPDM.Elresultadofuelacorrectarecuperacióndelos estímulosperoconunruidoremanente(fueraydentrodelabandadeinterés) noeliminablemediantefiltradoque Palabras clave:Modulador∑-∆,señalesPDM,modelocomputacional,filtro pasa-bajas,verificacióndecircuitosintegradosanalógicos. Introducción Hasta hace poco tiempo, muchos sistemas electrónicos estaban compuestos de una o más tarjetasdecircuitoimpresoycadaunadeestas seencontrabaformadapormuchoscircuitosintegrados. Recientes avances en métodos de diseñoytecnologíasdemanufacturahanpermitido integrar todos estos sistemas completos en un solochip[1].Lacombinacióndelacrecientedemandaporlaelectrónicadeconsumoyelconstante crecimiento en la densidad de empaquetamiento de los dispositivos semiconductores, están conduciendo hacia la integración de más y más sistemas funcionales en un solo circuito integrado. El resultado, entre otras cosas, es una incrementada necesidad por la integración de componentes analógicos y en modo mixto, por ejemplo, analógico-digital, RF-analógico-digital ymecánico-analógico-digital, en el mismo chip opaquete.Estos,tambiénllamadosSoC(Systems on Chip, Sistemas en un Chip),ofrecenventajas tales como alto rendimiento, bajo consumo de potencia y poco volumen y peso cuando son comparados con sus equivalentes tradicionales queposeíanmúltipleschips.Talessistemasson muy heterogéneos en el sentido de que contienentecnologíasmixtas,talescomológicadigital y analógica. También es posible diseñar estos sistemas por medio de la integración de varios bloques de construcción re-utilizables denominados bloques funcionales o Cores [1]. Diseñar tales SoCesindudablementeundesaf ío,yaque éstevinculaelmanejodeabstracciónanivelde 44 Universidad Antonio Nariño - Revista Facultades de Ingeniería sistemas mientras simultáneamente trata con los efectosf ísicosdelostransistoresylosfenómenoseléctricosparásitosindeseables,talescomo capacitancias de acoplamiento entre pistas, entre otros, asociados al circuito, que se intensificanconelaumentodelacomplejidaddelos sistemas.Delamismamanera,lapróximageneracióndepruebasdeSoCrepresentaunretoreal, especialmentecuandoelcostoyeltiempodesalida al mercado son usualmente requerimientos claves.Talescircuitosintegradosdeseñalmixta contienentrayectoriasdeseñalesyespecificacionesfuncionalesmuycomplejas,ylosprogramas de pruebas desarrollados podrían no ser muy viables, ya que estos serían significativamente lentosenlacaracterizaciónydepuradodeldispositivo, lo cual incrementaría enormemente el tiempo de salida al mercado (TTM, Time to Martket) [2]”page”:”1561-1571”,”volume”:”19”,”is sue”:”12”,”source”:”IEEE Xplore”,”abstract”:”The electronics industry is increasingly focused on theconsumermarketplace,whichrequireslowcosthigh-volumeproductstobedevelopedvery rapidly. This, combined with advances in deep submicrometertechnologyhaveresultedinthe ability and the need to put entire systems on a singlechip.Asmoreofthesystemisincludedon asinglechip,itisincreasinglylikelythatthechip willcontainbothanaloganddigitalsections.Developing these mixed-signal (MS. La dificultad esacentuadaporotroaspectodelaintegracióna niveldesistemasllamadaintegracióndebloques funcionales de terceros. A fin de competir con la complejidad del diseño, los fabricantes del • José G. Simancas y José C. Ortiz • sistemafinalestánforzadosaconfiarenbloques pre-diseñados por otras empresas, y llevar a cabo la integración de éstos como parte de un sistema más grande y complejo. Estos bloques funcionales son obtenidos de librerías virtuales quedescribenmediantesoftwareelbloquecomo partedelsistema[3]exceptforasimplereconstructionfilterandacomparator.Itiscapableof both generating arbitrary band-limited waveforms (for excitation purposes. Recientemente, tales módulos re-utilizables han capturado la atención de los diseñadores, quienes entienden el potencial de incrustarlos para construir los sistemas completos en un solo chip. Hacer lo anterior es similar a usar circuitos integrados en unatarjetadecircuitoimpreso,ylosdiseñadores estánformandoampliaslibreríasdebloquesde construcción pre-diseñados y pre-verificados. Estos, también llamados Embedded Cores, han facilitadolaimportacióndetecnologíaanuevos sistemasydiferenciarloscorrespondientesproductosatravésdelasventajasquebrindalapropiedad intelectual. Más importante aún, el uso deéstosmódulosre-utilizablesacortaeltiempo desalidaalmercadoparanuevossistemasdebidoalareutilizacióndelosdiseños[3]exceptfor asimplereconstructionfilterandacomparator. It is capable of both generating arbitrary bandlimitedwaveforms(forexcitationpurposes. Porelotroextremodelasogaestánlaspruebas, las cuales para la próxima generación de sistemas completos en un solo chip representarán unretorealparalosdiseñadores.Talescircuitos integrados de tecnología mixta tienen unas trayectorias de señal así como unas especificacionesmuycomplejas.Pararealizarpruebasaestos sistemas,sedebenutilizarATE (Automatic Test Equipement, Equipos de Prueba Automático), que son unos dispositivos externos que ayudan a realizar pruebas a los bloques internos del circuito integrado. Estos recursos ATEtambién utilizan unos algoritmos ad-hoc, que no son más que unos programas que llevan a cabo el manejo de tales recursos, es decir, controlan la operación de los ATE. Como estas pruebas se realizanenlafasedeproducción,seincrementa el TTM de los nuevos sistemas, y esto es un riesgo que los diseñadores no están dispuestos a correr [2]”page”:”1561-1571”,”volume”:”19”,”is Revista sue”:”12”,”source”:”IEEE Xplore”,”abstract”:”The electronics industry is increasingly focused on theconsumermarketplace,whichrequireslowcosthigh-volumeproductstobedevelopedvery rapidly. This, combined with advances in deep submicrometertechnologyhaveresultedinthe ability and the need to put entire systems on a singlechip.Asmoreofthesystemisincludedon asinglechip,itisincreasinglylikelythatthechip willcontainbothanaloganddigitalsections.Developingthesemixed-signal(MS.Eneldominio digital,losmecanismosytécnicasdepruebaestánencapacidaddeprobarlamayoríadelosdispositivosexistentes,ylainformacióndeprueba puedesertransportadasinperdidasalolargodel SoC y llevada al interior para ser aplicada a los bloquesquesedeseanprobar.Tambiénlasrespuestasdelosbloquespuedenserextraídasdela mismaformaparasuestudioyanálisis.Poresta razón,pareceposiblederivarunprocedimiento sistemáticoporelcual,elintegradordelsistema finalpuedeaccederalosbloquesfuncionalesvirtualesquecomponenelchip.Elproblemaenel dominioanalógico,eslocomplicadaqueresulta lainsercióndelasseñalesdepruebasobrelargas líneasdeinterconexiónenelinteriordeunchip ylaposteriorextraccióndelasrespuestasdelos bloques.Esaltamenteprobablequeocurrauna rápidadegradacióndelasseñalesdebidoalruido yladistorsiónintroducidaporelcomportamientoparasitodeloselementosdeinterconexiónen elinteriordelcircuitointegrado[3]exceptfora simple reconstruction filter and a comparator. It is capable of both generating arbitrary bandlimited waveforms (for excitation purposes. Esta distorsión es tolerable en el plano digital debido a la naturaleza discreta de sus señales y al margen de ruido de las tecnologías utilizadas en la actualidad (CMOS), pero no es tolerable enelplanoanalógico,dondeladistorsiónenlas señalesdepruebayderespuestapuedeconducir a una caracterización errónea de los bloques bajo prueba. Los mecanismos de acceso para pruebas, como por ejemplo scan, la utilización de los puertos para pruebas como JTAG y las técnicasparapruebasdediseñosonmuyeficientes.Estosedebeaquelainformacióndeprueba estáenformatodigital.Porestarazón,esposible derivarunprocedimientosistemáticopormedio UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 45 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • del cual el integrador final del sistema pueda accederalosbloquesfuncionalesquecomponen el diseño analógico usando señales digitales y posteriormente en el interior del chip realizar su conversión a señales analógicas a través de convertidores A/D embebidos en el diseño [3] except for a simple reconstruction filter and a comparator.Itiscapableofbothgeneratingarbitrary band-limited waveforms (for excitation purposes.Paraunarevisiónmásdetalladadelas técnicasdepruebadesistemasintegradosanalógicossepuederevisarelartículo[4]. Lo anterior, motivó al autor de este artículo a realizar un proyecto [5] en el año 2006 en el quesedesarrollaunametodologíadepruebade bloquesfuncionalesanalógicos,queutilizabloquesfuncionalesdepruebaqueseinstalanenel interiordelchippararealizarlacaracterización del comportamiento de los circuitos a nivel de bloques funcionales, y a nivel del sistema en general. Específicamente, estas estructuras de prueba deben rodear los bloques analógicos y de señal mixta, para proporcionar por medio deseñalesdigitalesdepruebaycaracterización, una estimación comportamental, es decir, una aplicacióntipoBISTcomoladesarrolladaen[6], sin la utilización de accesos directos externos, debidoaqueéstosaccesosrepresentanunpuerto dedicado para pruebas con líneas de prueba analógicasentodoelchip.Paratalfinsellevóa cabo el diseño VLSI (Very Large Scale Integration,muyaltaescaladeintegración)deunsencillo hardwaremixto,capazdeextraerlosestimulo sinusoidalescodificadosenseñalesPDM(Pulse Density Modulated, modulada por densidad de pulso),paralaexcitacióndeCUT(Circuit Under Test, circuito bajo prueba) en circuitos integrados mixtos, eliminando la necesidad de usar convertidores A/D y D/A,locualesventajosoyaque éstosbloquessonaltosconsumidoresdeáreaen loscircuitosintegrados.LasseñalesPDMdeben sergeneradaspreviamenteyalmacenadasenel interior del circuito integrado en algún tipo de memoria como se sugiere en [7]. Éste tipo de señalessepuedengenerarconmoduladoresΣ-Δ (Sigma-Delta),yéstatareaquedópendientedurantelarealizacióndeaquelproyecto.Larazón porlaqueseescogelaconversiónΣ-Δ es que la señal resultante es monobit (un tren de bit en 46 Universidad Antonio Nariño - Revista Facultades de Ingeniería cuyadensidadestacodificadalaseñalanalógica) en lugar de las señales multibit propias de los convertidores A/D convencionales, requiriendo éstasúltimasunacantidaddelíneasdeinterconexiónproporcionalalacalidaddelasseñalesde pruebaqueseingresenalcircuitointegrado.Por ejemplo,siserequierenresolucionesde16bits, se necesitarían mínimo 16 líneas para ingresar los datos al interior del circuito integrado, sin mencionarlasnecesariaspararealizarlasincronización.ResolucionessemejantessonfácilmentealcanzablesconmodulaciónΣ-Δ,sinnecesitar másdeunalíneaparalosdatos. Por todo lo anterior, en el presente artículo se propone el desarrollo en Matlab™ del modelo computacionaldeunmoduladorΣ-Δ quepuede serutilizadoenlageneracióndelasseñalesPDM que codificarán los estímulos sinusoidales utilizadosenlaaplicacióndesarrolladaen[5]. Éstetrabajoestáorganizadodelasiguientemanera:enlasecciónIIsedaunaexplicaciónteóricadelamodulaciónSigma-Delta.Enlasección III se realizan algunos cálculos sobre las característicasdelmoduladorqueseráimplementado usandoparatalfin,lasecuacionesmatemáticas establecidasporlaliteratura.EnlasecciónIVse desarrollaelmodelooestructuracomputacional del modulador Sigma-Delta de 2° orden. En la sección V se presentan las pruebas al modelo computacional y se analizan los resultados con elobjetodeverificarqueelfuncionamientodel modeloseajustaalateoríasobrelamodulación Sigma-Delta mediante simulaciones en Matlab™. Finalmente,enlasecciónVIsedanlasconclusiones. II. modulación sigma-delta El trabajo en modulación Σ-Δ fue desarrollado como una extensión a la bien establecida modulación Delta. Se considerará la estructura modulación/demodulación para el proceso de conversión A/D. La Fig.1 muestra el diagrama debloquesdelmoduladorDelta, y demodulador DeltasemuestraenlaFig.2.LamodulaciónDeltaestábasadaenlacuantizacióndelcambioen laseñaldemuestraamuestraenlugardelvalor absolutodelaseñalencadamuestra[8]. • José G. Simancas y José C. Ortiz • Cuantizadordeunbit fs Entrada analógica x(f ) + Salida y(f ) _ x(f )-x(f ) Cuantizadordeunbit Señal analógica + _ _ x(f ) Filtro Pasa Bajas _ DemodulaciónDelta ModulaciónDelta Cuantizadordeunbit Señal analógica + Filtro Pasa Bajas _ Figura 1.DiagramadebloquesdelmoduladorDelta[8] Entrada FiltroPasaBajas y(t) Salida analógica Figura 3. Diagramasdebloquesdelmoduladorydemodulador Delta[8]. Seña analógica + Filtro Pasa Bajas _ x(t) Demodulación X(t) N(S) + + Figura 2.DiagramadebloquesdelmoduladorΣ-Δ[8]. YaquelasalidadelintegradorenellazoderealimentacióndelaFig.1tratadepredecirelvalorde laentrada,sedicequeelintegradortrabajacomo unpredictor.Eltérminodeerrordepredicción, escuantizadoyutilizadoparahacerlapróxima predicción. El error de predicción cuantizado, esto es, la salida de la modulación Delta es integrada en el demodulador de la misma forma como se hace en el lazo de realimentación. En otras palabras, el demodulador predice el valor delaseñaldeentradaapartirdelerrordeprediccióncuantizado,talycomolomuestralaFig.2. Laseñalpredichaesluegosuavizadaconunfiltropasabajas.LosmoduladoresDelta,además, exhiben una pendiente de sobrecarga para las señalesdeentradaqueseelevanrápidamente,y debidoaestosurendimientodependedelafrecuenciadelaseñaldeentrada[8]. La modulación Delta requiere dos integradores para realizar los procesos de modulación y demodulación, tal y como se muestra en la Fig.3. Yaquelaintegraciónesunaoperaciónlineal,el segundointegradorpuedeserubicadoantesdel moduladorsinalterarlascaracterísticasentrada/ Revista _ I/S + Y(S) Filtro Pasa Bajas Figura 4.DiagramadebloquesdelmoduladorydemoduladorΣ-Δ. salida generales. Además, los dos integradores enlaFig.3puedensercombinadosenunosolo integradorporlapropiedaddelinealidad[8]. El arreglo mostrado en la Fig.4 es llamado un moduladorΣ-Δ.Éstaestructura,ademásdeser muy simple, puede ser considerada como una versión suavizada del modulador Delta de un bit.ElnombredemoduladorΣ-Δvienedecolocar el integrador, denominado Sigma, frente al modulador Delta. La característica del ruido de cuantizacióndetalcodificadoresindependientedelafrecuencia,encontrastealamodulación Delta [8]. Así como el modulador Delta, los moduladores Σ-Δ usan un simple cuantizador ordinario, en ocasiones referido como comparador.Sinembargo,adiferenciadelmodulador Delta, éstos sistemas codifican la integral de la señalyportalrazón,surendimientoesinsensiblealatasadecambiodelaseñal[8]. UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 47 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • Parademostrarlapropiedaddeeliminaciónde ruido,seutilizarácomobaseelmodelosimplificadoeneldominiodeLaplacedelaFig.4.Cabe agregar que el sumador a la derecha del integradorrepresentauncomparador,yesaquídonde ocurre el muestreo y el ruido de cuantización es añadido al modelo. Ahora se determina la funcióndetransferenciadeseñal,Hx(s),ycomo hipótesissedebedecirqueN(s)=0,yseobtiene la siguiente relación a partir del modelo de la Fig.4. 1 1 Y(s) s = H x(s) = = X(s) 1 1+ s 1 + s HastaéstepuntoelanálisisdelmoduladorΣ-Δ serealizóeneldominiodeLaplaceodeS,enlo quesigueseharáelmismoanálisisperoparael dominiodiscretoodeZ.Seconsideraellazode primerordenmostradoenlaFig.5,lafunciónde transferenciaeneldominiodeZdeunintegrador esdenotadaporI(z)yelcuantizadordeunbites modelado como una fuente de ruido aditivo. Elanálisisdeseñalestándarentiempodiscreto sobre el sistema mostrado en la Fig.5 produce lasalidadellazoSigma-deltadeprimerorden [10].. Y ( z ) = X ( z ) + (1 − z −1 )Q( z ) (1) Respuesta que equivale a un filtro pasa bajas. Ahorasedeterminalafuncióndetransferencia de ruido, He(s),ysedebeestablecerlahipótesis queX(s)=0yobtenerlassiguientesrelaciones. 1 s Y ( s) = H e ( s) = = N (s) 1 1+ s 1 + s (2) + Apartirdeaquí,sepuedevisualizarclaramente el funcionamiento fundamental del modulador Σ-Δ.PrimeroelmoduladorΣ-Δrealizaunfiltradopasabajasenlaseñaldeinterés,estoes,deja pasarlaseñalsinningunamodificación.Luego, realiza un filtrado pasa altas en la componente de ruido, lo cual disminuye el ruido de cuantizaciónenlabandadeseñal,yportanto,ayudaa mejorarlaresolucióndeconversión.Ladesventajaesqueelruidofueradelabandadeseñales amplificado,peroestosepuedemejorarconuna etapadefiltradoposterior[9]. Integrador X(z) _ (3) Yaqueelruidodecuantizaciónesasumidopara ser aleatorio, el diferenciador (1-z-1) mostrado enlaecuación(3)duplicalapotenciadelruido cuantizado. Sin embargo, el error ha sido empujado hacia las altas frecuencias debido a este factor diferenciador [8]. Hasta el momento, se ha obtenido el modelo tanto en tiempo continuocomoentiempodiscretodeunmodulador Sigma-deltadeprimerorden.EnlaFig.6puede observarse el espectro resultante de la señal de salida del modulador Σ-Δ. Se puede visualizar la potencia de la señal de interés, que tiene un color gris, y la potencia del ruido fuera de la banda de señal en rayas. Se observa como éste tipodemodulaciónarrojaelruidohacialasaltas frecuencias. H(f ) Q(z) Y(z) + _ I(z) Fs/2 Z-1 Potenciadelaseñaldeinterés Potenciadelruidofueradebanda Figura 5. Diagrama de bloques del modulador Σ-Δ en tiempodiscreto[8]. 48 Universidad Antonio Nariño - Revista Facultades de Ingeniería Figura 6. Espectrodepotenciadelaseñaldesalidadel moduladorΣ-Δ[8]. • José G. Simancas y José C. Ortiz • iii. modelo matemático del modulador ∑-∆ de 2° orden Paralacodificacióndelasseñalesdeexcitación, se consideró la idea de realizar una conversión A/D convencional multi-bit de las señales o estímulosquesedebíangenerar,paraluegoser decodificadasenelhardwareinterno.Estopresentabadiversosinconvenientes[7].Primero,las señalesresultantesserianmulti-bit,loqueharía máscomplejoelpuertodeconexiónconelexterior,ytambiénexigiríalainclusióndehardware adicionalparaelcontroldelascomunicaciones. Porotraparte,hayimplementacionesdelamodulación Σ-Δ que generan señales de un solo bit, y alcanzando resoluciones del orden de los 16 bits sin mayores inconvenientes [9]. Otra característicaimportanteessuformaespectral, permitiendo la recuperación de las señales de excitaciónsoloconunfiltropasabajas,yalgún hardware digital adicional. El esquema de modulación Σ-Δ, ha permitido la realización de convertidores de datos de alta precisiónconresolucionesdeentre16y20bits. Enocasioneslaseñalesmuestreada,cuantizada y codificada para ser tratada por mecanismos digitales.Entalcaso,esnecesarialautilización deconvertidoresD/Aparalarecuperacióndela señaloriginal.Laconversióndeseñalserealiza por la codificación de una señal de entrada digital multi-bit en un solo tren de bits, con una amplitud pico a pico de Δ, requiriendo el uso de procesamiento de señal digital y técnicas de sobre-muestreo. codificaciónΣ-Δaseguraquelaseñaldeentrada y el error de cuantización, ocupen regiones del espectrodefrecuenciadiferentes. Para transformar la señal de entrada digital en una forma analógica, simplemente se filtra el tren de bits en la salida del modulador con un filtroanalógicopasa-bajasdepreferenciaactivo con un ancho de W. Es importante anotar que laoperacióndefiltradoeliminarálamayorparte delruidodecuantización,peronoloeliminará ensutotalidad.Quedaráalgúnruidoresidualen labandadeinterés,yéstenopuedeserseparado delaseñalpormediodefiltrado.Portanto,para el modulador de segundo orden utilizado en este proyecto,algodelruidodecuantizaciónaparece enlasalidajuntoconlaseñaldeinterés,ysuSNR estarádadapor[7]. Σ-Δ Figura 7. ProcesodemodulaciónΣ-Δ. FECHA ACEPTADO: OCTUBRE 21 DE 2014 FECHA RECIBIDO: MAYO 22 DE 2014 Para asegurar que un nœ mer ⎛ A ⎞ SNR = 15 log 2 (OSR ) + 6 log 2 ⎜ ⎟ − 8(dB ) (4) se– al de prueba est‡ n en el tre se– al de prueba, ft, de ⎝⎛ Δ Para un nœ mero entero de los ciclos de la (4)asegurardeque la A ⎞ ⎠ FECHA RECIBIDO: MAYO 22 DE 2014 FECHA ACEPTADO: OCTUBRE 21 DE 2014 5 SNR = 15 log 2 (OSR ) + 6 log 2 ⎜ ⎟ − 8(dB ) ⎝ Δ ⎠ (4) submœ ltiplo de la frecuencia de la reglas del muestreo coherent se– al de prueba est‡ n en el tren de bits PDM, la frecuencia de la se– al de prueba, ft, debe ser escogida como un submœ ltiplo de la frecuencia de muestreo, fs, de acuerdo a la reglas del muestreo coherente, tal y como se muestra en la siguiente expresi— n [7]. Donde OSR Rate) es la tasaesdelasobreDonde OSR(OverSampling (OverSampling tasa dela siguiente expresi— n [7]. Donde OSR (OverSampling Rate) Rate) es la tasa de sobrefs fs M M 2 ft = fs , y W es el ancho de banda del ,yWeselanchodebanda sobre-muestreo 2 muestreo ft = N muestreo , y WW es el ancho de banda del (6) modulador. La ecuaci— n (4) sugiere que un valor muy alto Donde M y N son enteros. Con M = 1, 2, 3, etc., la W N OSR, acercar’ a ecuación la conversi— n a la ideal. Quiz‡ la gran del modulador. La (4) sugiere que ftun ser‡ un mœ ltiplo entero de la frecuencia modulador. La ecuaci— n la(4)codificaci— sugiere unsolo valor muyfrecuencia altofs/N. ventaja de n PDMque es que un filtro primitiva En otras palabras,M la frecuencia de la se– al Donde y N son enteros. anal— gico con ancho de banda fijo es requerido para de prueba debe estar arm— nicamente relacionada con la valor muya alto OSR, la conversión a Esto tambiŽ n sugiere OSR, acercar’ la conversi— nacercaría a Esto la es, ideal. Quiz‡ gran primitiva. recuperar la se– al anal— gica. se puede colocar unala frecuencia frecuencia ft ser‡ un mœ ltiplo que la frecuencia se– al cualquiera la banda es de paso del modulador, y ventaja de la codificaci— n en PDM que solo un filtrolimita laprimitiva primitiva resoluci— n en frecuencia del esquema de fs/N. En otras palabra obtenerla nuevamente con un filtro sintonizado a dicha laideal.Quizálagranventajadelacodificación generaci— n de se– al. Para una frecuencia de muestreo fija, anal— gico con ancho banda [7]. de banda fijo es requerido lapara resoluci— n solo ser mejorada por el incremento de depuede prueba debe estar arm— nic La figura 8, muestra el diagrama de bloques del la una longitud de la secuencia. Finalmente, para codificar la recuperar la se– almodulador anal— gica. es, se puede colocar PDMesquesolounfiltroanalógicoconancho Σ-Δ pasaEsto bajas de segundo orden utilizado en se– al de pruebafrecuencia en un tren PDM, primitiva. es esencial queEsto la se– al tambi ste proyecto. Se escogi—de as’ por ser el del implementado en se– al cualquiera Ž en la banda paso modulador, estŽ en y el anchoprimitiva de banda del modulador Sigma - delta. limita la resoluci— n en [10]. Tal sistema es descrito por el siguiente conjunto de debandafijoesrequeridopararecuperarlaseñal obtenerla nuevamente un finitas filtro sintonizado a dicha ecuaciones con en diferencias generaci— n de se– al. Para una ft ≤ W La Fig. 7 ilustra éste proceso, cuando se ha banda [7]. (7) y(n) = sgn[x (n �1)] resoluci— n solo puede analógica. Esto es, se puede colocar una De señal acuerdolacon los desarrollos previos para unser me x (n)el = x (n �1) + u(n) � y(n) (5) modulador La figura 8, muestra diagrama de bloques del de segundo orden, la SNR en el ancho de banda la longitud de la secuencia. F aplicado al modulador una señal sinusoidal de del modulador, y teniendo adem‡ s una se– al de amplitud A, cualquieraenlabandadepasodelmodulador,y modulador Σ-Δ pasa bajas segundo utilizado en x (n)de = x (n) + x (n �1) �orden y(n) la cual esta codificada un tren de bits conen una un amplitud se– alende prueba tren PD Donde u(n) es as’ la se– al digitalser de entrada multi-bit, y(n) es pico en a pico de Δ, viene dada por la ecuaci— n (4). Ahora entradaenformatodigital,conunaamplitudA Ž ste proyecto. Sela escogi— por el implementado en el ancho banda salida de un solo bit, y sgn(x) representa la funci— n signo bien, para unaestŽ SNR deseada, el ancho de de banda del del m obtenerlanuevamenteconunfiltrosintonizado [10]. Tal sistema deesx. Para descrito porparticular el siguiente conjunto de W puede ser expresado como [7] una secuencia de entrada u(n) y un modulador yunafrecuenciaft,lacualhasidosobre-mues- ecuaciones en diferencias conjunto particular de condiciones iniciales x (0) y x (0) se finitas W = fs ⋅ 2 adichabanda[7]. puede generar la se– al PDM equivalente a la entrada. La (8) ft ≤ W se obtiene por medio de la iteraci— n del conjunto de treada,estoesfs>>ft.Sisesuperponelasalida y(n) salida = sgn[x ecuaciones en diferencias (5) y su almacenamiento de y(n). 2 (n �1)] Si ahora se sustituye (6) y (8) en (7) da Como es de esperarse de la teor’ a, el ruido de cuantizaci— n De acuerdo con los des muestra el diagrama de bloques Mdel deunmoduladorSigma-deltaconsuentrada, La Fig. 8, la banda de interŽ s y puesto en las altas ≤ fs ⋅ 2 x1 (n)esfrecuencias. =eliminado x1 (nen�1) + u(n) � y(n) (5) N fsmodulador de segundo orden, la (9) Σ-Δ pasa bajas de segundoO orden y teniendo adem eliminandodel fs se modulador, puede escribir podemos fácilmente ver que la salida conmuta modulador Un x modulador en y(n) un sistema con x2 (n)respuesta = +Σ-Δx2est‡(nbasado �1) � Mla cual esta codificada en un tr 1 (n) impulsiva infinita cuya salida realiza una utilizadoenésteproyecto.Seescogióasíporser ≤ 2 entre los niveles alto y bajo de tal manera que transformaci— n de la se– al de entrada en una secuencia Donde u(n) es la se– al digital de entrada multi-bit, y(n) es Npico a pico de Δ, viene (10) dada infinitamente larga de bits (un tren de bits) o una se– al La ecuaci— n (10) proporciona la relaci— n b‡ sica entre la multibit. propiedad tiene como consecuencia que con n signo salida de un solo bit,ƒ sta y sgn(x) representa la funci— bien, N,para SNR deseada longitud de la secuencia el ’ ndiceuna de frecuencia del tono la entrada quede codificada en la densidad de la laelimplementadoen[10].Talsistemaesdescrito una entrada peri— dica tal como una se– al sinusoidal, el de prueba, la calidad de la se– al generada la cual est‡ de x. Para una secuencia particular de Esto entrada y un modulador W puede ser expresa patr— n de salida de los bits no se repita. implica queu(n) no denotada por la SNR sobre el ancho de banda del porelsiguienteconjuntodeecuacionesendifeexiste una secuencia finita en la salida del modulador que forma de onda de salida. Tal señal es conocida conjunto particularrepresente de condiciones iniciales x1(0) y x2(0) se la amplitud de la se– al de prueba codificada−A,(1 / 15)( S modulador, a la se– al peri— dica de entrada. Sin embargo, se y los niveles de salida del modulador W denotado = fs ⋅por2 su tenerPDM aproximaciones a la se– al original de generar la pueden se– al equivalente a laa partir entrada. La rencias finitas diferencia Δ. comounaseñalPDM.Esinteresanteanotarque puede un tren de bits finito. Si se asegura que la se– al de entrada salida se obtiene completa por medio de la deiteraci— delde conjunto de un nœ mero entero ciclos en n el tren bits de IV. E y repitiendo Ž ystesu infinitamente, obtendr’ a unade y(n). (5)( n almacenamiento laseñaldeentradaesmultibit.Éstaseñalpuede ecuacionesyen (ndiferencias ) =salida, sgn[ ]al PDM seoriginal. Si ahora ∑-∆. se sustituye (6) y (8) aproximaci— nx cercana a− la 1 se–) Esto es 2 Como es de esperarse deel laseguimiento teor’ a,deellasruido cuantizaci— n logrado por reglas de de muestreo La estructura computacional del modulador estudiado en ser recuperada completamente por el filtrado es eliminado M en un algoritmo en − (1 / 15 coherente descritas m‡ s adelante. Para la mejor la secci— n anterior se implementa altas N+1 x (enn)laaproximaci— =banda x1 (n,ndeseNde −debe 1interŽ )tambiŽ + unsasegurar (ny)puesto −queyel(bitnen ) delas Matlabª fs ≤ defsestado ⋅2 . El algoritmo sintetiza al espacio bits que est‡ n siendo extra’ dos, sea igual descrito en (5), con Ž ste se puedenN calcular la secuencia de (5) digital del tren de bits en la salida del modula- frecuencias. 1 laal secuencia primero del patr— n, para de Ž sta manera evadir la salida, el espectro de la secuencia de salida y realizar la discontinuidad m‡) s+ obvia. x ( n ) = x ( n x ( n − 1 ) − y ( n ) recuperaci— n de la se– al de entrada al modulador a travŽ s O eliminando fs se puede esc 2 1 2 dor.Estoesposiblegraciasaqueelprocesode filtrado pasa-bajas. Tomando en cuenta la literatura, se Un modulador Σ-Δ est‡ basado en un sistemadel con 2 1 1 2 1 2 1 2 − (1 / 15)( SNR + 23− 6 log2 ( A / Δ )) − (1 / 15)( SNR + 23− 6 log2 ( A / Δ )) − (1 / 15)( SNR + 23−6 log2 ( A / Δ )) STRUCTURA COMPUTACIONAL DEL MODULADOR (1 / 15)( SNR M sinusoides respuesta impulsiva infinita cuya salida realiza objetivos una que se plantaron en [5] se generaran ≤ 2 −de 1 de hasta 1 voltio pico a pico, y hasta la frecuencia transformaci— n de la se– al de entrada en una secuencia MHz. TambiŽ n se tiene que la amplitud pico N a pico del tren infinitamente larga de bits (un tren de bits) o una de se–bitsalen la salida del modulador es de 2 voltios. En otras palabras, A= 0.5, SNR=70 dB, Δ=2 y Nnes(10) igual a proporciona 512 bits, La ecuaci— -multibit. 0935 • Vol. • No. 9 •tiene pp 43-55 julio - diciembre de 2014 ƒ sta 5propiedad como• consecuencia quelos con necesarios para codificar las se– ales de prueba en una longitud detodo lalosecuencia se– al PDM de longitud finita. Por anterior, y segœ n laN, el ’ n una entrada peri— dica tal como una se– al sinusoidal, el ecuaci— n (10) se tiene que M = 4. de prueba, la calidad de la s de muestreo fs=64 MHz, entonces la patr— n de salida de los bits no sederepita. Esto implica queComo nola frecuencia Fig. 8: Diagrama bloques del modulador Σ-Δ. frecuencia primitiva es fs/N = 64 MHz/512 = 125000 Hz, es sobre denotada por la SNR existe una secuencia finita en la salida del moduladordecir que que la m‡ xima frecuencia que se puede generar modulador, la amplitud de la se estableci— que una SNR aceptable es de 70 dB, y segœ n los Revista UAN • ISSN 2145 49 FECHA RECIBIDO: MAYO 22 DE 2014 FECHA ACEPTADO: OCTUBRE 21 DE 2014 5 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • Para asegurar que un nœ mero entero de los ciclos de la ⎛ A ⎞ se– al serescogidacomounsubmúltiplodelafrecuende prueba est‡ n en el tren de bits PDM, la frecuencia SNR =Dondeu(n)eslaseñaldigitaldeentradamulti15 log 2 (OSR ) + 6 log 2 ⎜ ⎟ − 8(dB ) de lacia se– de al muestreo de prueba, ser con escogida como fs,ft,dedebe acuerdo la reglas delun bit,y(n)eslasalidadeunsolobit,ysgn(x)repre⎝ Δ ⎠ (4) submœmuestreo ltiplo de lacoherente, frecuencia tal de ymuestreo, de acuerdo como se fs, muestra en la a sentalafunciónsignodex.Paraunasecuencia reglas del muestreo coherente, tal y como se muestra en5 siguienteexpresión[7] siguiente expresi— n [7]. fs lar de condiciones iniciales x1(0)yx2(0)sepuede M entero de los ciclos de la Para asegurar que unftnœ=mero fs 2 PDM equivalente a la entrada. muestreo generar ,layseñal W es el ancho del A ⎞de banda ⎛ se– al de prueba est‡ n en el tren bits PDM, la frecuencia N de (6) SNR =Lasalidaseobtienepormediodelaiteracióndel 15W log ) + 6 log 2 ⎜ ⎟ − 8(dB ) (6)5 FECHA RECIBIDO: MAYO 22 DE 2014 2 (OSR FECHA MAYO DE212014 5 deDonde la se– M al ydeN prueba, ft, debe ser modulador. La ecuaci— n22(4) sugiere un⎠valor muy alto Δ FECHA RECIBIDO: ACEPTADO: OCTUBRE DE 2014 que ⎝ son enteros. Con M escogida = 1, 2, 3,como etc., un la (4)y su FECHA ACEPTADO: OCTUBRE 21 DE 2014 conjunto de ecuaciones en diferencias (5) FECHA RECIBIDO: 22 DE 2014 5a OSR, acercar’ a MAYO la conversi— n a la ideal. Quiz‡ la gran submœ ltiplo de la frecuencia de muestreo, fs, de acuerdo Donde M y N son enteros. Con M = 1, 2, 3, frecuencia ft ser‡ un mœ ltiplo entero de la frecuencia FECHA ACEPTADO: OCTUBRE n 21 DE 2014y(n). de es de ventaja de almacenamiento la codificaci— PDM es Como que solo un esperarse filtro la reglas del muestreo coherente, tal frecuencia y como se de muestra etc.,lafrecuenciaftseráunmúltiploenterode Para asegurar nœ mero la entero de los ciclos deen la primitiva fs/N. En que otrasun palabras, la se– al Donde OSR (OverSampling Rate) es⎛ la tasa de sobreA Para asegurar que un nœ mero entero de los ciclos de la ⎞⎞ anal— gico con ancho de banda fijo ⎛esA requerido para la siguiente expresi— nn[7]. delateoría,elruidodecuantizacióneseliminase– al de prueba est‡ en el tren de bits PDM, la frecuencia de prueba debe estar arm— nicamente relacionada con la SNR = 15 log ( OSR ) + 6 log − 8 ( dB ) ⎟⎟ − colocar frecuencia fs/N. EnPDM, otras palabras, 2 (OSR 2 ⎜ se– alla de prueba que est‡ primitiva n elmero tren de bits frecuencia SNRla=fs + 6es, logse 8(dB ) una frecuencia asegurar unennœ ft, entero los la ciclos de la recuperar se–15allog gica. )Esto puede 2⎛⎜ dePara la se– al de prueba, debe ser de escogida como un primitiva. Esto tambiŽ sugiere que la frecuencia Mnde Δ ⎞puesto ⎝⎝A ⎠⎠−modulador, do enanal— la2banda de interés y en las altas (4) de la se– al de prueba, ft, debe ser escogida como Δ la frecuencia de la señal de prueba debe estarun se– al de prueba est‡ n en el tren bits PDM, la frecuencia 2 SNR = 15 log ( OSR ) + 6 log 8 ( dB ) se– al cualquiera en la banda de paso del y ft n=en fs ⎟ de banda del (4) primitiva muestreo 2, y W es el ancho 2 ⎜ submœ ltiplo de la frecuencia de muestreo, fs, de acuerdo limita la resoluci— frecuencia del esquema dea frecuencias. submœ ltiplo de la frecuencia de muestreo, fs, de acuerdo se– al de prueba,relacionada ft, debe escogida como un W N sercon obtenerla nuevamente con un filtro sintonizado a dicha de la armónicamente la frecuencia ⎝ Δ ⎠ (6)a FECHA RECIBIDO: MAYO 22 DE 2014 la Donde OSR (OverSampling particulardeentradau(n)yunconjuntoparticuFECHA ACEPTADO: OCTUBRE 21 DERate) 2014 es la tasa de sobrela la reglas n deldemuestreo coherente, tal y como muestrafija, en (4) generaci— se– al. Para una frecuencia de se muestreo la reglas muestreo coherente, tal y como de se muestra en Donde (OverSampling Rate)que es un la tasa sobreltiplodel muestreo, ala modulador. La ecuaci— n (4) sugiere valorde muy alto submœ banda [7]. OSR Donde Mnde y laNfrecuencia son enteros. Con Mpor= fs, 2, acuerdo 3, etc., de Donde OSR (OverSampling Rate) esbasado la tasa de sobrela resoluci— siguiente expresi— n [7]. primitiva.Estotambiénsugierequelafrecuencia la solo puede ser de mejorada el1,incremento Un modulador Σ-Δ está en un sistema lareglas siguiente expresi— n coherente, [7]. la del muestreo tal y como se muestra en OSR, acercar’ a la conversi— ndiagrama a la ideal. Quiz‡ la gran La figura 8, muestra el de bloques del fs frecuencia ft ser‡ un lamœresolución ltiplo entero de frecuencia la longitud de lalimita secuencia. Finalmente, parala codificar Donde OSR Rate) es la tasa de sobrefsla (OverSampling primitiva en frecuencia della M con respuesta infinita cuya salida la siguiente expresi— nun [7].tren ventaja deΣ-Δ codificaci— PDM es que solo un filtro modulador bajasndeimpulsiva segundo orden utilizado en M fs primitiva fs/N. Enenotras palabras, la de la la se– se– al al 22pasa se– al de prueba PDM, esfrecuencia esencial que ft = muestreo , y W es el ancho de banda del fs ft del =M esquema generación defsseñal. Para-una fre- la gico con ancho banda fijo requerido muestreo , yde Was’ esporelser ancho delabanda del enŽ anal— ste proyecto. Se escogi— elesimplementado en realiza una transformación de señalpara de W de prueba debede estar arm— nicamente relacionada con N estŽ en el ancho de banda modulador Sigma delta. (6) 2 ecuaci— recuperar latrada se– alW anal— Esto se puede colocar una (6) ft = N nCon fssugiere [10]. Tal sistema es poreles, elancho siguiente conjunto de defrecuencia muestreo yuna W es banda del cuenciademuestreofija,laresoluciónsolopuemodulador. La ngica. (4)secuencia sugiere que undevalor muylarga alto primitiva. Esto tambiŽ la frecuencia en, descrito infinitamente Donde M y N son enteros. M = que 1, 2, 3, etc., la modulador. La ecuaci— n (4) sugiere que un valor muy alto W N se– al cualquiera en la banda de paso del modulador, y Donde M y N son enteros. Con M = 1, 2, 3, etc., la ecuaciones en diferencias finitas (6) OSR, acercar’ a la conversi— n a la ideal. Quiz‡ la gran primitiva limita la resoluci— n en frecuencia del esquema de desermejoradaporelincrementodelalongitud frecuencia ft ser‡ un mœft ltiplo entero de la frecuencia bits tren de bits) o una señal OSR, acercar’ a (un la conversi— n afiltro la ideal. Quiz‡multibit. la dicha granÉsta ≤ W modulador. La ecuaci— n (4) sugiere que un valor muy alto obtenerla nuevamente con un sintonizado a frecuencia ft ser‡ un mœ ltiplo entero de la frecuencia Donde M y N son enteros. Con M = 1, 2, 3, etc., la (7) ventaja de y(n) la codificaci— es que solo un filtro generaci— n de se– otras al. Para una frecuencia decodificar muestreo fija, = sgn[x2nn(nnPDM �1)] primitiva fs/N. En palabras, la frecuencia de la se– al de la secuencia. Finalmente, para la ventaja laa codificaci— PDM es queQuiz‡ solo la un gran filtro OSR, acercar’ la conversi— a lafijo ideal. propiedadtienecomoconsecuenciaqueconuna banda [7].decon primitiva fs/N. Encon otras palabras, la frecuencia de la se– al ftndebe ser‡ un los mœ ltiplo entero deel la frecuencia De acuerdo desarrollos previos para un anal— gico ancho de banda es requerido para frecuencia la resoluci— solo puede ser mejorada por incremento de de prueba estar arm— nicamente relacionada con la anal— gico con ancho de banda fijo es requerido para ventaja de entradaperiódicatalcomounaseñalsinusoidal, la (n) n es que un filtro señaldepruebaenuntrenPDM,esesencialque La figura 8,codificaci— elPDM desolo bloques del primitiva de longitud prueba debe estar arm— nicamente relacionada con la =anal— x1 (ngica. �1) +diagrama u(n) fs/N. En otras palabras, la frecuencia de la banda se– alla (5) modulador de segundo orden, la SNR en el ancho de recuperar laxse– almuestra Esto es, � sey(n) puede colocar una la de la secuencia. Finalmente, para codificar 1 frecuencia primitiva. Esto tambiŽ n sugiere que la frecuencia recuperar la se– al anal— gica. Esto es, se puede colocar una anal— gico con ancho de banda fijo es requerido para modulador Σ-Δ pasa bajas de segundo orden utilizado eny de frecuencia primitiva. Esto tambiŽ n sugiere que la frecuencia prueba debe estar arm— nicamente relacionada con la laseñalestéenelanchodebandadelmodulador del modulador, y teniendo adem‡ s una se– al de amplitud A, se– al cualquiera en la banda de paso del modulador, se– al de prueba en un tren PDM, es esencial que la se– al elpatróndesalidadelosbitsnoserepita.Esto primitiva limita la resoluci— n en frecuencia del esquema de cualquiera en banda de paso del modulador, recuperar lanuevamente se– al anal— Esto es, sesintonizado colocar una x2 (n) =escogi— xla1gica. (n) xun2por (n �1) �puede y(n) Ž se– stealproyecto. Se as’ ser el implementado eny frecuencia primitiva la resoluci— n en frecuencia deluna esquema de Esto nfrecuencia sugiere que frecuencia la cual esta codificada entambiŽ un tren de bits Sigma con amplitud obtenerla con+ filtro a dicha estŽ en ellimita ancho banda del modulador - delta. Sigma-delta. generaci— nprimitiva. de se–deal. Para una de la muestreo fija, implicaquenoexisteunasecuenciafinitaenla obtenerla nuevamente con un filtro sintonizado a dicha se– al cualquiera en la banda de paso del modulador, y [10]. Tal sistema es descrito por el siguiente conjunto de generaci— n de se– al. Para una frecuencia de muestreo fija, primitiva limita la resoluci— n en frecuencia del esquema de Donde u(n) es la se– al digital de entrada multi-bit, y(n) es pico a pico de Δ, viene dada por la ecuaci— n (4). Ahora banda [7]. la resoluci— n solo puede ser mejorada por el incremento de banda [7].nuevamente obtenerla un diagrama filtroque sintonizado an dicha del represente a ladel señal ecuaciones en 8, diferencias finitas la resoluci— nuna solo al. puede ser porde elde incremento de generaci— n de Para unamejorada frecuencia muestreo fija, la salida de salida un solomuestra bit, modulador ycon sgn(x) representa la funci— signo bien, para deseada, el ancho banda del La figura el de bloques la longitud dese–laSNR secuencia. Finalmente, para codificar la ft ≤ W La figura 8, muestra el diagrama de bloques del banda [7]. la longitud de la secuencia. Finalmente, para codificar la (7) la resoluci— n solo puede ser mejorada por el incremento de periódicadeentrada.Sinembargo,sepuedentede x. Para una secuencia de entrada u(n) y un y(n)pasa = sgn[x (n W puede como [7] modulador Σ-Δ bajas2particular de�1)] segundo orden utilizado en modulador se– al de prueba en ser un expresado tren PDM, (7) es esencial que la se– al modulador Σ-Δ pasa bajaseldediagrama segundo orden utilizadodel en La figura 8, muestra de bloques se– al de prueba en un tren PDM, es esencial que la se– al De acuerdo con los desarrollos previos para un la longitud de la secuencia. Finalmente, para codificar la conjunto particular de condiciones iniciales x (0) y x (0) se ( 1 / 15 )( SNR + 23 − 6 log ( A / Δ )) Ž ste proyecto. Se escogi— as’ por ser el implementado en 1 2 neraproximacionesalaseñaloriginalapartirde − del modulador2 Sigma - delta. estŽ en el ancho de banda Ž ste proyecto. Se = escogi— as’ segundo ser�elorden implementado en modulador Σ-Δ pasa bajas de W segundo =en fsun ⋅ 2tren Deacuerdoconlosdesarrollospreviosparaun x1 (n) �1) +por u(n) y(n) estŽal en ancho de banda del modulador Sigma - delta. (5) modulador de orden, la SNR en el ancho de banda de el prueba PDM, es esencial que la se– al puede generar la se– al PDM equivalente a la utilizado entrada. La [10]. Tal sistema es x descrito por el siguiente conjuntoen de se– 1 (n (8) untrendebitsfinito.Siseaseguraquelaseñalde [10]. Tal sistema es descrito por ser el siguiente conjunto de Ž salida ste proyecto. escogi— as’depor el implementado del modulador, teniendo adem‡ s una se–Sigma al de- amplitud en el anchoyde banda del modulador delta. A, se obtiene por medio la iteraci— n del conjunto en de estŽ moduladordesegundoorden,laSNRenelanecuaciones enSe diferencias finitas ecuaciones en diferencias finitas x (n) = x (n) + x (n �1) � y(n) [10]. Tal sistema es descrito por el siguiente conjunto de ft ≤ W entradacompletaunnúmeroenterodeciclosen 2 diferencias 1 2su almacenamiento de y(n). la cual esta codificada en un tren de bits con una amplitud ecuaciones en (5) y (7) ft ≤ W chodebandadelmodulador,yteniendoademás Si ahora se sustituye (6) y (8) en (7) da y(n) = sgn[x (n �1)] (7) ecuaciones en diferencias y(n) = se– sgn[x �1)] Donde u(n) es la al finitas digital de y(n) es pico a pico de Δ,con viene dada por la ecuaci— n (4). Ahora Como es de esperarse de la22 (n teor’ a, entrada el ruido multi-bit, de cuantizaci— n eltrendebitsdesalida,yrepitiendoésteinfiniDeunaseñaldeamplitudA,lacualestácodificada acuerdo los desarrollos previos para un ft ≤ W ( 1 / 15 )( SNR + 23 − 6 log ( A / Δ )) M De acuerdo con los desarrollos previos para un (7) 2 − la salida dey(n) un solo bit, y sgn(x) representa la funci— n signo = =sgn[x (n �1)] bien, para de una SNR deseada, el ancho de banda del es eliminado la banda de interŽ s y�puesto en las altas xx1 (n + u(n) y(n) xxen (5) 2�1) modulador segundo orden, la SNR en el ancho de banda tamente,seobtendríaunaaproximacióncercana fs ≤ fs ⋅ 2 1 (n) (n) = (n �1) + u(n) � y(n) (5) modulador de segundo orden, la SNR en el ancho de banda De acuerdo con los desarrollos previos para un enuntrendebitsconunaamplitudpicoapico 1 1 de x. Para una secuencia particular de entrada u(n) y un modulador W puede ser expresado como [7] frecuencias. del modulador, y teniendo adem‡ s una se– al de amplitud(9) A, N segundo la señal PDM original. logradose por el del modulador, y teniendo adem‡ s+ 23 una se– al/ Δde amplitud ==de x1x(n �1) + � Esto y(n) xax1 (n) modulador decodificada orden, SNR el2 (con ancho deamplitud bandaA, + xx2u(n) (n �1) � y(n) conjunto particular condiciones iniciales xes 15)(la SNR −en 6bits log A ))una 1(0) y x2(0)(5) deΔ,vienedadaporlaecuación(4).Ahorabien, − (1 /un 2 (n) 1 (n) la cual esta en tren de x (n) = x (n) + (n �1) � y(n) O eliminando fs se puede escribir 2 la se– al 1 PDM 2reglas de muestreo =teniendo fs ⋅ 2enadem‡ la modulador, cual estaW codificada un tren de bits con amplitud seguimiento las coherente s una al deuna A, puede generar equivalente amulti-bit, lasistema entrada. La Un modulador est‡de en un con Donde u(n) es la se– al digital de�1) entrada y(n) es del a picouna dey SNR Δ, viene dada por la se– ecuaci— namplitud (4). Ahora para deseada, el ancho de banda del(8) x2 (n) =Σ-Δ x1medio (n) + de xbasado � y(n) Donde u(n) es la se– al digital deiteraci— entrada multi-bit, y(n) de es lapico pico aesta picocodificada de Δ, viene dada por la ecuaci— n (4). Ahora 2 (n ( 1 / 15 )( SNR + 23 − 6 log ( A / Δ )) cual en un tren de bits con una amplitud M salida se obtiene por la n del conjunto 2 − descritasmásadelante.Paralamejoraproximarespuesta salidala funci— realizan signo una la salida deimpulsiva un solo bit,infinita y sgn(x)cuya representa bien,moduladorWpuedeserexpresadocomo[7] para una SNR el ancho de banda del ≤viene 2 deseada, laDonde salida u(n) de en un solo bit,alydigital sgn(x) representa la funci— y(n) n signo bien,a para unaΔ, SNR deseada, ella ancho de banda del la se– entrada multi-bit, es pico se de dada por ecuaci— ecuaciones su almacenamiento de y(n). transformaci— nesdiferencias de la se– al(5) dey de entrada una secuencia de x. Para ción,sedebetambiénasegurarqueelbitN+1de una secuencia particular de en entrada u(n) y un pico Si ahora sustituye (6) y (8) en (7) da [7] n (4). Ahora modulador W puede ser expresado como N desalida x. Para una secuencia particular de entrada u(n) y un modulador W puede ser expresado como [7]de banda (10) la de un solo bit, y sgn(x) representa la funci— n signo bien, para una SNR deseada, el ancho del Como es de esperarse de la teor’ a, el ruido de cuantizaci— n infinitamente larga de condiciones bits (un treniniciales de bits)x1(0) o una se– se al conjunto particular y x2(0) / 15 + 23 log Δ ))Δ )) 2 ( A(/ A − ((1 1 / )( 15SNR )( SNR +− 236 6[7] log MW lasecuenciadeNbitsqueestánsiendoextraídos, conjunto particular de condiciones iniciales x1(0) y las x2(0) se modulador 1−/(15 )( SNR 23 − 6−log (A / Δ/)) 2 b‡ La ecuaci— n (10) proporciona la+como relaci— sica entre la de x. Para una secuencia particular de entrada u(n) y un W puede ser expresado 2n − es eliminado en la banda de interŽ s y puesto en altas = fs ⋅ 2 multibit. ƒ sta propiedad tiene como consecuencia que con puede generar la se– al PDM equivalente a la entrada. La fs= ≤fsfs⋅ 2⋅ 2(N, (8) puede generar la de se– al PDM equivalente a la entrada. La longitud de laWsecuencia (8)del tono ’ ndice conjunto iniciales xdel y x2(0) se )( SNR + 23− 6de logfrecuencia seaigualalprimerodelpatrón,paradeéstama(8) 1(0) frecuencias. 2 ( A / Δ )) − 1 / 15el una entrada peri— por dicacondiciones tal como se– nal sinusoidal, el salida separticular obtiene medio de launa iteraci— conjunto de N (9) W = fs ⋅ 2 salida se obtiene por medio de la iteraci— n del conjunto de de prueba, la calidad de la se– al generada la cual est‡ puede generar la se– al PDM equivalente a la entrada. La (8) neraevadirladiscontinuidadmásobvia. patr— n de salida de los bits (5) no se repita. Esto implica de quey(n). no Siahorasesustituye(6)y(8)en(7)da ecuaciones en diferencias y su almacenamiento O fs se puede Si eliminando ahora se sustituye (6) yescribir (8) en da de banda del ecuaciones en diferencias (5) ylasuiteraci— almacenamiento de y(n). la SNR sobre el (7) ancho salida obtiene por medio de n un del conjunto den denotada Si ahorapor se sustituye (6) y (8) en (7) da Un se modulador Σ-Δ est‡la basado endel con existe una secuencia finita en la salida modulador que Como es de esperarse de teor’ a, el ruido desistema cuantizaci— Como es de esperarse de la teor’ a, el ruido de cuantizaci— n ( 1 / 15 )( SNR + 23 − 6 log A / Δ())Acodificada modulador, la amplitud de la se– al de prueba A, M ecuaciones en diferencias (5) y su almacenamiento de y(n). ( 1 / 15 )( SNR + 23 −26( log / Δ )) M − respuesta impulsiva infinita cuya salida realiza una − Si ahora se sustituye (6) y (8) en (7) da represente aPara laen se–la al peri— dica de entrada. Sin embargo, se es eliminado banda de interŽ s y puesto en las altas ( 1 / 15 )( SNR + 23 − 6 log22 ( A / Δ )) M asegurar que un entero los ≤salida 2fs − modulador fs ≤ ⋅⋅ 2 es eliminado endela banda y puesto ensecuencia lasde altas y los niveles de del denotado por su Como estener de esperarse de la teor’ a, se– elsnúmero ruido cuantizaci— n cifs ≤ fs 2 transformaci— naproximaciones la se– alde deainterŽ entrada endeuna pueden la al original a partir de frecuencias. (1 / 15)( SNR + 23− 6 log2 ( A / Δ )) MN N (10) frecuencias. (9) closdelaseñaldepruebaestáneneltrendebits es eliminado en la banda interŽ sque ydepuesto las altas infinitamente larga de bitsde (un tren o de una se– al diferencia Δ.N fs ≤ fs ⋅ 2 − (9) un tren de bits finito. Si se asegura labits) se– alen entrada (9) La ecuaci— n (10) proporciona la relaci— n b‡ sica entre la O eliminando fs se puede escribir frecuencias. PDM,lafrecuenciadelaseñaldeprueba,ft,debe multibit. ƒ sta propiedad tiene como consecuencia que con N completa un nœ mero entero ciclos en de bits con de O eliminando fs se puede escribir (9) Un modulador Σ-Δ est‡ debasado en eluntren sistema longitud de la secuencia N, el ’ ndice de frecuencia del tono Oeliminandofssepuedeescribir Un modulador Σ-Δ est‡ basado en un sistema con IV. ESTRUCTURA (1 / 15escribir )( SNR + 23−6 log2 (DEL A / Δ ))MODULADOR M una entrada peri— dica talinfinitamente, comocuya una salida se–sealobtendr’ sinusoidal, el salida, y repitiendo Ž ste −COMPUTACIONAL eliminando fs se puede respuesta impulsiva infinita realizaa una una (1 / 15la )( SNR log2 ( A / Δ )) la cual est‡ deO prueba, la M calidad se–+ 23 al−6generada − de ≤ 2 respuesta realiza una Un nmodulador est‡ basado ensalida un sistema con patr— de salida deΣ-Δ los bits Esto implica que no ∑-∆. aproximaci— nimpulsiva ainfinita la se–secuya alrepita. PDM original. Esto es ≤ 2 transformaci— ncercana de la se– alnode entrada en una secuencia )( SNR + 23el −6 log denotada porMNla SNR ancho del 2 ( A / Δ ))de banda (10) transformaci— n de la finita se– alen de entrada enXmodulador una secuencia − (1 / 15sobre respuesta cuya salida realiza una existe una secuencia la salida del que U(n) Ncomputacional logrado porimpulsiva el seguimiento de las de reglas muestreo X (n)(un (10) infinitamente larga deinfinita bits tren bits)(n)de o una se– al y(n) modulador, ≤ 2proporciona La estructura del modulador estudiado en la amplitud de la se– al de prueba codificada A, infinitamente larga de bits (un tren de bits) o una se– al Z La ecuaci— n (10) la relaci— n b‡ sica entre la transformaci— n de la se– al de entrada en una secuencia represente adescritas lapropiedad se– al peri— dica de entrada. Sin embargo, se coherente m‡tiene s adelante. Para la que mejor N multibit. ƒ sta como consecuencia con La ecuaci— nde (10) proporciona la relaci— n b‡algoritmo sica entre la (10) la secci— n anterior se implementa en un en (10) y los niveles salida del modulador denotado por su multibit. ƒ sta propiedad tiene como consecuencia que con longitud de la secuencia N, el ’ ndice de frecuencia del tono infinitamente larga de bits (un tren de bits) o una se– al pueden tener aproximaciones a la se– al original a partir de aproximaci— n, se debe tambiŽ n asegurar que el bit N+1 de una entrada peri— dica tal como una se– al sinusoidal, el Matlabª longitud de la secuencia N, el ’ ndice de frecuencia del tono La ecuaci— n (10) proporciona la relaci— n b‡ sica entre la . El algoritmo sintetiza al espacio de estado Δ. la calidad de la se– al generada la cual est‡ una entrada peri— dica talest‡ como una se– al dos, sinusoidal, el diferencia de prueba, multibit. ƒ desta propiedad tiene como consecuencia que con un tren bits finito. Sique se asegura que la se– al desea entrada Laecuación(10)proporcionalarelaciónbásica la secuencia de Ndebits n siendo extra’ igual Z se patr— n de salida los bits no repita. Esto implica que no longitud de prueba, la con calidad la ’ ndice se– alcalcular generada la cual est‡ de N, el frecuencia del tono descrito en la (5), ste de sesobre pueden ladesecuencia de patr— n de salida de los bits no se repita. Esto implica que no denotada porsecuencia la Ž SNR el de ancho banda del una entrada peri— dica tal como una se– al sinusoidal, el completa un nœ mero entero de ciclos en el tren de bits de al primero del patr— n,finita para Ž sta manera evadir que la de existe una secuencia en de la salida del modulador denotada por la de SNR sobre el generada ancho delay banda del entrelalongituddelasecuenciaN,elíndicede prueba, la calidad de la se– al cual est‡ salida, el espectro la secuencia de salida realizar la existe una secuencia finita en la salida del modulador que IV. E STRUCTURA COMPUTACIONAL DEL MODULADOR modulador, la amplitud de la se– al de prueba codificada A, patr— n de salida de los bits no se repita. Esto implica que no salida, y repitiendo Ž ste infinitamente, se obtendr’ a una discontinuidad m‡ s obvia. represente a la se– al peri— dica de entrada. Sin embargo, se denotada modulador, la amplitud de la se– al de prueba codificada A, por la SNR sobre el ancho de banda del recuperaci— n de la se– al de entrada al modulador a travŽ s frecuencia del tono de prueba, la calidad de la represente a la se– al peri— dica de entrada. Sin embargo, se y los niveles de salida del modulador denotado por su existe una secuencia finita en la salida del modulador que ∑-∆. aproximaci— n aproximaciones cercana a la se–a la al se– PDM original.a Esto pueden tener al original partir es de modulador, y los niveles de salida del modulador denotado por su la amplitud de la se– al de prueba codificada A, del filtrado pasa-bajas. Tomando en cuenta la literatura, se pueden tener aproximaciones a la se– al original a partir de señalgeneradalacualestádenotadaporlaSNR diferencia Δ. represente a laelse–seguimiento al peri— dica de entrada. Sin embargo, se logrado por muestreo un tren de bits finito. Si se aseguralas quereglas la se– de al de entrada yestableci— diferencia Δ. de La niveles estructura computacional del es modulador en los salida del modulador denotado porn su que una SNR aceptable de 70 dB,estudiado y segœ los un tren tener de bits finito. Si m‡ se sasegura la Para se– al de entrada pueden aproximaciones aadelante. laciclos se–que alenoriginal de coherente lapartir mejor sobreelanchodebandadelmodulador,laamcompleta undescritas nœ mero entero de el trena de bits de diferencia la secci— n anterior se implementa en un algoritmo en Δ. objetivos que se plantaron en [5] se generaran sinusoides completa unn,nœfinito. de ciclos el tren deentrada bits de de un tren de SiŽ entero se asegura que en la se se– alelde aproximaci— semero debe tambiŽ n asegurar que bit N+1 IV. MODULADOR Figura 8.DiagramadebloquesdelmoduladorΣ-Δ. salida, y bits repitiendo ste infinitamente, obtendr’ a una de plituddelaseñaldepruebacodificadaA,ylos Matlabª .E El algoritmo sintetiza al espacio de estado hasta voltio pico COMPUTACIONAL a pico, y hasta laDEL frecuencia de 1 IV. E1STRUCTURA STRUCTURA COMPUTACIONAL DEL MODULADOR salida, yunrepitiendo Ž que ste est‡ infinitamente, setren obtendr’ a igual una completa nœ mero entero de ciclos en el de bits de la secuencia de N bits n siendo extra’ dos, sea ∑-∆. aproximaci— n cercana a la se– al PDM original. Esto es MHz. descrito en (5), con Ž ste se pueden calcular la secuencia de TambiŽ n se tiene que la amplitud pico a pico del tren ∑-∆. IV. ESTRUCTURA COMPUTACIONAL DEL MODULADOR aproximaci— ndelcercana la se–deal Ž PDM original. Esto es salida, y por repitiendo Ž ste infinitamente, se obtendr’ a una al primero n, a para manera la logrado el patr— seguimiento de lasstareglas de evadir muestreo salida, el espectro de la secuencia de salida y realizar la de bits en la salida del modulador es de 2 voltios. En otras La estructura computacional del modulador estudiado en logrado por el seguimiento de las reglas de muestreo ∑-∆. aproximaci— cercana am‡las se–adelante. al PDM original. es discontinuidad m‡ s obvia. La estructura computacional del modulador estudiado en coherente n descritas Para laEstomejor recuperaci— n de la se– al de entrada al modulador a travŽ s palabras, A= 0.5, SNR=70 dB, Δ=2 y N es igual a 512 bits, la secci— n anterior se implementa en un algoritmo en coherente descritas m‡ s Nariño adelante. Para la mejor Antonio Revista Facultades de Ingeniería logrado el se seguimiento las -reglas muestreo 50 por Universidad laLanecesarios secci— n pasa-bajas. anterior seTomando implementa en de unprueba algoritmo en estructura computacional delse– modulador estudiado en aproximaci— n, debe tambiŽ de n asegurar quede el bit N+1 de los del filtrado en cuenta la literatura, se para codificar las ales en una Matlabª . El algoritmo sintetiza al espacio de estado aproximaci— descritas n, se debe m‡ tambiŽ n asegurar Para que el la bit N+1 de coherente s adelante. mejor Matlabª El algoritmo sintetiza alen estado secci— n. que anterior implementa un la algoritmo la secuencia de N bits que est‡ n siendo extra’ dos, sea igual la estableci— una aceptable es deespacio 70 dB, yde nnen los se– al PDM de finita. Por todo lo anterior, ysegœ segœ la descrito en (5),longitud conSNR Ž se ste se pueden calcular secuencia de la secuencia bits tambiŽ que est‡n nasegurar siendo extra’ dos, aproximaci— n, de se Ndebe que el bit sea N+1igual de descrito en (5), con Ž ste se pueden calcular la secuencia de Matlabª . El algoritmo sintetiza al espacio de estado al primero del patr— n, para de Ž sta manera evadir la ecuaci— objetivos que se plantaron en [5] se generaran sinusoides n (10) se tiene que M = 4. salida, el espectro de la secuencia de salida y realizar la primero de delN patr— n, para Ž staextra’ manera evadir laalsecuencia bits que est‡ n de siendo dos, sea igualla 2 1 - - • José G. Simancas y José C. Ortiz • nivelesdesalidadelmoduladordenotadoporsu diferenciaΔ. iv. estructura comPutacional del modulador ∑-∆ Laestructuracomputacionaldelmoduladorestudiadoenlasecciónanteriorseimplementaen unalgoritmoenMatlab™.Elalgoritmosintetiza alespaciodeestadodescritoen(5),conéstese puedencalcularlasecuenciadesalida,elespectro de la secuencia de salida y realizar la recuperación de la señal de entrada al modulador, a través del filtrado pasa-bajas. Tomando en cuentalaliteratura,seestablecióqueunaSNR aceptableesde70dB,ysegúnlosobjetivosque seplantaronen[5]segeneraransinusoidesde hasta1voltiopicoapico,yhastalafrecuencia de 1 MHz. También se tiene que la amplitud picoapicodeltrendebitsenlasalidadelmodulador es de 2 voltios. En otras palabras, A= 0.5,SNR=70dB,Δ=2yNesiguala512bits,los necesariosparacodificarlasseñalesdeprueba enunaseñalPDMdelongitudfinita.Portodo loanterior,ysegúnlaecuación(10)setieneque M=4. Como la frecuencia de muestreo fs=64 MHz, entonces la frecuencia primitiva es fs/N = 64 MHz/512=125000Hz,esdecir,quelamáxima frecuenciaquesepuedegenerarsegúnlaecuación(6)esM(fs/N)=4x125000Hz=500kHz. Laúnicaformapodergenerarseñalesconmás frecuenciaesconladisminucióndesucalidad, estoes,ladisminucióndelaSNR.ParaunaSNR = 50 dB se tiene que M = 16, y para la misma frecuenciaprimitivaseobtienequelamáxima frecuenciagenerableesde2MHz.Ycon60dB sepuedegenerarhasta1MHz,perosecorreel riesgodedegradarlaseñaldeformasignificativa. Paralarecuperacióndelaseñalenelinteriordel CIcuyofuncionamientosepretendeverificaren el proyecto desarrollado en [5], se usa un filtro analógicopasa-bajas.Éstefiltrotambiénesmodelado computacionalmente para corroborar el principiodefuncionamientodelaestrategia.El filtroobtenidoenaquelproyectoesde6°ordeny tienebandadetransiciónde750kHzhasta1500 kHzygananciaunitariaenlabandadepaso. Revista Todoelmodelomatemáticohastaahoratratado, dio origen al siguiente algoritmo, el cual se codificaenMatlab™.Laimplementacióndelespacio de estado se basó en los modelos computacionalespresentadosen[11],yenelusodealgunas funcionesdelDelta-SigmaToolboxV7.1. Las secuencias de interés se generan a partir del sistema de ecuaciones en diferencias finitas presentado en (5). La salida queda almacenada en un vector. Se implementa el filtro analógico pasa bajas. Como se trata de una implementación computacional, y la señal proveniente del modulador Sigma-Deltaesunasecuencianumérica,cuandoseimplementaunfiltroenformatoanalógico enMatlab™ocurrenproblemasdeconvergencia, portanto,seimplementóunfiltrorecursivoIIR, que se basa en la transformación de un filtro analógicoenunaversióndigital,queesloquese necesitaba.Lafrecuenciademuestreoescogida delfiltrofuelosuficientementegrandeparadar característicascontinuasaunprocesodiscreto,y eslacuartapartedelafrecuenciademuestreodel modulador, fn=16MHz.Paralaimplementación delfiltroseusaronlasfuncionesqueproporciona el DSP Toolbox V7.1, garantizando de esta manera la convergencia del filtro. El filtro digital escogidofuedeltipoButterworth,portenerun comportamiento monótono en ambas bandas, queseajustaalarespuestadelfiltroSallen-Key utilizadoen[5]. Enlasalidaseobtuvieronlasseñalesanalógicas generadas para la excitación de los bloques internos de los circuitos integrados. Se calculan los espectrosdepotenciaencadapartedelproceso decodificación-decodificacióndeseñalesPDM. Unavezconstruidoslosbloquescomputacionales necesarios, se procede a realizar pruebas al modeloantesdescritoparaverificarquecumple lasfuncionesparalasquefueelaborado.Vermaterialcomplementario. v. Pruebas y resultados. Para verificar el correcto funcionamiento del modelo procedemos a realizar simulaciones en Matlab™.Elprocedimientoaseguireselsiguiente: UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 51 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • 1. Generar los estímulos sinusoidales a 3 frecuenciasyamplitudesdistintasqueseingresaránalmoduladorconMatlab™.Los3estímulosgeneradosserán:1Vp-p@500kHz,0.5 Vp-p@300kHz,yunaseñaldeDCde0.45V. 2. IngresarlosestímulosalmodelocomputacionaldelmoduladorSigma-DeltaimplementadoenMatlab™. 3. Generar gráfica de la señal PDM obtenida conelmodelocomputacional. 4. Generar el espectro de potencia de la señal PDMyverificarqueseajustaalaformateóricaesperadadelmismo. 5. LuegosehaceelfiltradodelaseñalPDMpara recuperar el estímulo analógico y verificar que es posible realizar su extracción en el interiorusandounhardwaresimple(unfiltro activo)parapoderexcitarlosCUT. 6. Generar el espectro de potencia de la señal recuperada. Éste espectro se visualizará con la frecuencia normalizada f/fs, como se hace en [3] y en [12] en lugar de una escala logarítmicadelafrecuenciaf,debidoalano existencia de armónicos adicionales al tono de interés. Elcriterioparaestediseñoexperimentalquesirvedevalidaciónalmodelofuelageneraciónde lasseñalesrequeridasenelsistemaparatesting de circuitos integrados analógicos desarrollado en[5],esdecir,queelmodeloexhibierasucapacidaddegeneraresetipodeseñales.Serequería que el modulador generara tonos sinusoidales confrecuenciashasta500kHz,yconamplitudes hasta1Vp-p. Enlasfiguras9,10y11semuestranlasseñales PDMenlasalidadelmoduladoryelespectrode potenciadelasseñalesadiferentesfrecuenciasy amplitudes,comosehabíapropuesto.Seobserva queesposiblecodificarenuntrendepulsosuna señalanalógica.Elespectroseajustaalesperado teóricamente con un tono a la frecuencia de la señal de entrada en la banda de interés, y ruido de cuantización fuera de banda que ha sido puestoallíporelmodulador.Conestosepuede verificarqueelmodelocomputacionalfunciona conforme a la teoría y que tendrá utilidad en la aplicacióndesarrollada[5]. 52 Universidad Antonio Nariño - Revista Facultades de Ingeniería Comolaideadelproyecto[5]esutilizarunsencillohardwareanalógicoparalarecuperaciónde lasseñalesdepruebaenelinteriordelCIcuyos bloquesseestánverificando.Loanteriorobliga a verificar que desde las señales PDM generadas con el modelo computacional se pueden recuperarlosestímuloscodificados.Paratalfin se aplica el filtro diseñado e implementado en Matlab™alaseñalPDM. En la Fig.12 se muestra la salida del filtro para cada una de las señales de prueba. Como se puedeobservarenlaFig.12,síesposiblerecuperar las señales de prueba mediante un filtro, aunque éstas contienen una cantidad de ruido queperturbalasformasdeonda.Setratadeun ruidoresidualenlabandadeinterésquenose puedeeliminarmedianteelusodeunfiltro.Lo anterior se puede considerar una de las debilidadesdelaaproximaciónaquípropuesta.Enla Fig.13semuestraelespectrodepotenciadela señaldesalidadelfiltroysepuedeobservarel efectodelfiltroenlaseñalPDM.Paraelprimer tono,1Vp-p@500kHz,laSFDRresultantees40 dB.Paraelsegundotono,0.5Vp-p@300kHz,la SFDR resultante es 38 dB. Para el tercer tono, 0.45VDC,laSFDRresultantees42dB.ElSFDR es básicamente la relación señal a ruido en la bandadeinterésluegodelfiltrado.Esclaroque el filtro pasa-bajas elimina el ruido fuera de la banda de interés, pero se mantiene un residuo enlabanda,queseconsideratolerable,debidoa que la SFDR en la misma se mantiene alrededor delos40dBenpromedio,queesaceptablepara en un modulador ∑-∆ de segundo orden, si se comparaconotrosmoduladoresdeordensuperiorqueconsiguenSFDRde60dB[3]. La razón de tal situación es que el ruido en la bandadeinterésnoeseliminablepormediode filtrado.Sibienseeliminagranpartedelruido fueradelabandadeinterés,noselogrademaneratotaldebidoa1)losnivelesdeatenuación enlabandaeliminadadelfiltropasa-bajasy2)la ampliabandadetransición(750kHz)requerida para mantener el filtro analógico en un orden aceptable (6° orden). Para mejorar la relación señalaruidobastaríaconincrementarelorden del filtro, hasta donde el diseño hardware lo permita. • José G. Simancas y José C. Ortiz • Figura 9. a) Señal PDM obtenida en la salida de la implementación software del modulador Σ-Δ. b) Espectro de potenciaparaondasinusoidalcon1Vp-p@500kHz. Figura 10. a) Señal PDM obtenida en la salida de la implementación software del modulador Σ-Δ b) Espectro de potenciaparaondasinusoidalcon0.5Vp-p@300kHz. Figura 11. a) Señal PDM obtenida en la salida de la implementación software del modulador Σ-Δ b) Espectro de potenciaparaunvoltajeDCde0.45V. Revista UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 53 • Modelo computacional de un modulador ∑-∆ de 2° orden para la generación de señales de prueba • Tiempo(Númerodemuestra) Tiempo(Númerodemuestra) c) b) a) Tiempo(Númerodemuestra) Figura 12.Estímulosrecuperadosmediantefiltropasa-baja. FrecuenciaNormalizada(F/Fs) FrecuenciaNormalizada(F/Fs) a) b) FrecuenciaNormalizada(F/Fs) c) Figura 13. Espectrosdepotenciadelosestímulosrecuperadosmediantefiltropasa-bajas. vi. conclusiones Alcomienzodeéstetrabajoseplanteólanecesidad de desarrollar un modelo computacional de un modulador ∑-∆ para la obtención de las señalesPDMrequeridaenelproyectoelaborado en[5]paralaverificacióndecircuitosintegrados analógicos. Para tal fin se estudió el funcionamientoteóricodelosmoduladores∑-∆comose describeenlaliteraturasobreestetema.Comoel objetivo era llegar al modelo computacional, se desarrolló previamente un modelo matemático basadoenunadescripcióndeecuacionesendiferencias finitas, así como algunas relaciones matemáticasadicionalesquepermitenespecificarlas condiciones de sobre-muestreo para conseguir unmuestreocoherente.Sellevóacaboeldesarrollo de un modelo computacional codificado enMatlab™,yquehaceusodealgunasfunciones del Delta-Sigma Toolbox V 7.1. Luego de esto sellevaronacabosimulacionesdelmodeloque verificaban que su comportamiento se ajustaba al descrito en la teoría. Para ello se obtuvieron 54 Universidad Antonio Nariño - Revista Facultades de Ingeniería las formas de onda en la salida del modulador, así como sus espectros de potencia. Se verificó que es posible codificar señales analógicas de diferentes parámetros (amplitud y frecuencia) enseñalesPDM,porlaventajaqueéstasúltimas presentanalserdetipomonobit.Losespectros depotenciamostraronlasseñalescodificadasen la banda de interés, así como el ruido fuera de bandaqueesllevadoalasaltasfrecuenciaspor accióndelmodulador.UnacaracterísticaimportanteparaverificareslarecuperacióndelosestímuloscodificadosenlasseñalesPDMapartir deunfiltropasa-bajas,puesdeestamanerafue sugeridoen[5].Sellevóacaboéstaverificación implementandounfiltrodeestetipoenMatlab™ e ingresando las señales PDM, y se observaron lasformasdeondadelosestímulosrecuperados, enlascualesaparecenlasperturbacionesdebido aunruidoremanenteenlabandadeinterésno eliminable por filtrado, y una parte también de ruidoresidualfueradebandadebidoalosniveles de atenuación en banda suprimida del filtro, lo queseconsideraunadesventajadelaestrategia • José G. Simancas y José C. Ortiz • presentadaen[5]ycomplementadaconestetrabajo,peroqueestolerable.Enresumen,selogró conseguir el modelo computacional para el fin propuesto de generar las señales PDM adecuadasparacodificarlosestímulos,ytalmodelose ajusta al comportamiento esperado de un modulador∑-∆.Deéstamanerasecomplementala propuestarealizadaen[5]. Agradecimientos Deseamos agradecer a Dios la oportunidad de culminar con éxito este trabajo. También agradecemos la colaboración de la Ing. Zhoe Comas en el desarrollo de este artículo. Referencias [1] Y.Zorian,E.J.Marinissen,yS.Dey,“Testing embedded-corebasedsystemchips,”enTest Conference, 1998. Proceedings International, pp. 130-143, 1998. [2] K. Kundert, H. Chang, D. Jefferies, G. Lamant, E. Malavasi, y F. Sendig, “Design of mixed-signal systems-on-a-chip,” IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.,vol.19,n.o12,pp.1561-1571,dic.2000. [3] M.M.Hafed,N.Abaskharoun,yG.W.Roberts, “A 4-GHz effective sample rate integratedtestcoreforanalogandmixed-signal circuits,”IEEE J. Solid-State Circuits,vol.37, n.o4,pp.499-514,abr.2002. [4] J.L.Simancas-García,“DiagnósticodeCircuitosIntegradosAnalógicosydeComunicaciones”,Inge@Uan,vol.1fasc.1,pp.7-19, 2011. Revista [5] J. L. Simancas-García, “Bloque funcional parapruebasdecircuitosintegradosanalógicosydeseñalmezclada”,Finaldecarrera., Universidad del Norte., Barranquilla-Colombia,2006. [6] M.M.HafedyG.W.Roberts,“Astand-alone integrated excitation/extraction system for analog BIST applications,” en Custom Integrated Circuits Conference, 2000. CICC. Proceedings of the IEEE 2000, pp. 83-86, 2000. [7] E. M. Hawrysh y G. W. Roberts, «An integration of memory-based analog signal generationintocurrentDFTarchitectures», en Test Conference, 1996. Proceedings., International,1996,pp.528-537. [8] S. Park, Principles of sigma-delta modulation for analog-to-digital converters. [En línea].Disponibleen:http://www.numerixdsp.com/appsnotes/APR8-sigma-delta.pdf. [9] J. G. Proakis y D. K. Manolakis, “Digital Signal Processing”, 4 edition. Upper Saddle River,N.J:PrenticeHall,2006. [10]P. Aziz, H. Sorensen, y J. V. der Spiegel, «An Overview of Sigma-Delta Converters: Howa1-bitADCachievesmorethan16-bit resolution»,Dep. Pap. ESE,pp.61-84,ene. 1996. [11]E.Soria-Olivas,M.Martinez-Sober,J.Francés-Villora.,yG.Camps-Valls,“Tratamiento digital de señales: problemas y ejercicios resueltos.”PearsonEducación,España2003. [12]R.SchreierandG.C.Temes,Understanding Delta-SigmaDataConverters,JohnWiley& Sons,NewYork,2004. UAN • ISSN 2145 - 0935 • Vol. 5 • No. 9 • pp 43-55 • julio - diciembre de 2014 55