LABORATORIO # 1

Anuncio

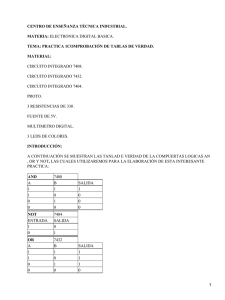

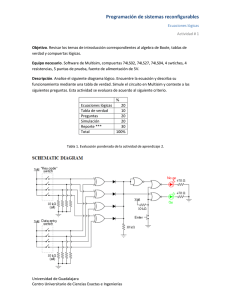

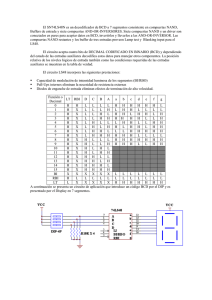

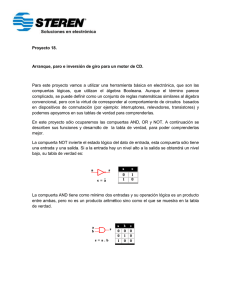

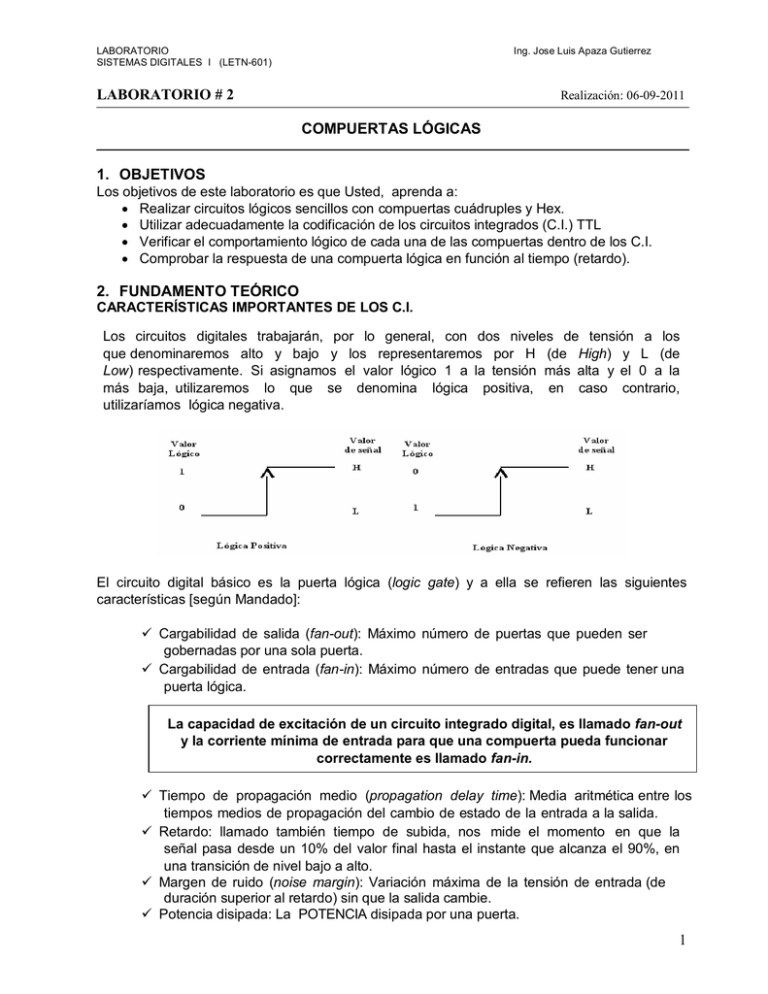

LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez LABORATORIO # 2 Realización: 06-09-2011 COMPUERTAS LÓGICAS 1. OBJETIVOS Los objetivos de este laboratorio es que Usted, aprenda a: Realizar circuitos lógicos sencillos con compuertas cuádruples y Hex. Utilizar adecuadamente la codificación de los circuitos integrados (C.I.) TTL Verificar el comportamiento lógico de cada una de las compuertas dentro de los C.I. Comprobar la respuesta de una compuerta lógica en función al tiempo (retardo). 2. FUNDAMENTO TEÓRICO CARACTERÍSTICAS IMPORTANTES DE LOS C.I. Los circuitos digitales trabajarán, por lo general, con dos niveles de tensión a los que denominaremos alto y bajo y los representaremos por H (de High) y L (de Low) respectivamente. Si asignamos el valor lógico 1 a la tensión más alta y el 0 a la más baja, utilizaremos lo que se denomina lógica positiva, en caso contrario, utilizaríamos lógica negativa. El circuito digital básico es la puerta lógica (logic gate) y a ella se refieren las siguientes características [según Mandado]: Cargabilidad de salida (fan-out): Máximo número de puertas que pueden ser gobernadas por una sola puerta. Cargabilidad de entrada (fan-in): Máximo número de entradas que puede tener una puerta lógica. La capacidad de excitación de un circuito integrado digital, es llamado fan-out y la corriente mínima de entrada para que una compuerta pueda funcionar correctamente es llamado fan-in. Tiempo de propagación medio (propagation delay time): Media aritmética entre los tiempos medios de propagación del cambio de estado de la entrada a la salida. Retardo: llamado también tiempo de subida, nos mide el momento en que la señal pasa desde un 10% del valor final hasta el instante que alcanza el 90%, en una transición de nivel bajo a alto. Margen de ruido (noise margin): Variación máxima de la tensión de entrada (de duración superior al retardo) sin que la salida cambie. Potencia disipada: La POTENCIA disipada por una puerta. 1 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez CLASIFICACIÓN A continuación se da una de las posibles listas de clasificación [Mandado]. Según su fabricación de Silicio Según el tipo de dispositivo Bipolar: - RTL: Lógica resistencia transistor - DTL: Lógica diodo transistor - TTL: Lógica transistor transistor - I2L: Lógica de inyección integrada MOS: - PMOS: Transistores MOS de canal P - NMOS: Transistores MOS de canal N - CMOS: Transistores MOS complementarios Según el nivel de integración SSI: Escala de integración baja (10 a 100 componentes) MSI: Escala de integración media (100 a 1000 componentes) LSI : Gran escala de integración (1000 a 10.000 componentes) VLSI: Escala de integración muy grande (10.000 a 100.000 componentes) ULSI: Escala de integración supergrande ( más de 100.000 componentes) Circuitos TTL El componente básico en los circuitos TTL es el transistor bipolar. La familia TTL se subdivide en distintas subfamilias cuyas características comunes son las siguientes: a) Alimentación: Vcc = + 5 V, ± 10% b) Niveles lógicos de entrada: entre 0,2 V y 0,8 V para el estado L y entre los 2,4 V y Vcc para el estado H. c) Identificador: 54XXX para la serie militar y 74XXX para la comercial d) Temperatura de trabajo: de – 55º a 125º C para la 54 y de 0º a 70º C para la 74. e) Margen de ruido: 0,4 V. El resto de características de esta familia depende de la subfamilia utilizada. En la siguiente tabla se muestran las características de las subfamilias más conocidas. Características Estándar Bajo consumo Alta velocidad Schottky Retraso (ns) Consumo por puerta (mW) Velocidad (MHz) Abanico de salida Identificador 10 33 6 3 Schottky de bajo consumo 10 10 1 22 19 2 35 3 50 125 35 10 20 10 20 20 L H S LS Como puede observarse, la velocidad de transmisión entre los estados lógicos es su mejor característica, pero en contra tiene su gran consumo. 2 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez COMPUERTAS AND, OR, NAND, NOR Y EXOR La breve descripción que se detalla a continuación define de forma simplificada el funcionamiento de cada una de estas puertas así como la ecuación lógica a la que responden y su correspondiente tabla de verdad: AND: La salida es “1” cuando todas las entradas valen también “1”; Y=A●B OR: La salida es “0” cuando todas las entradas valen “0”; Y=A+B NAND: La salida es “1” cuando cualquier entrada vale nivel logico “0”; Y= A●B NOR: La salida es “1” cuando todas las entradas valen “0”; Y= A+B EXOR: La salida es “1” cuando el numero de entradas de entradas que esten a “1” sea impar; Y=A●B + A●B; Y=AB 3 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez Identificación de las compuertas digitales Debido a la falta de normalización, existe una gran diversidad de códigos de identificación, por lo que cada fabricante utiliza códigos particulares. A continuación veremos algunas de las normas más comúnmente aceptadas. 1 7 5 2 9 4 3 8 6 1. Anagrama del fabricante: Indica quien es el fabricante 2. Lugar de fabricación: Indica el país donde se ha fabricado 3. Fecha de fabricación: Las dos primeras cifras indican el año y las dos siguientes la semana. 4. Tipo de encapsulado: Cada fabricante suele tener un código de una o varias letras para indicar si el encapsulado es de plástico, metal o cerámico. 5. Tipo de componente: Es la información más importante del IC ya que nos indica qué tipo de circuitos lleva integrados. Este código suele estar bastante generalizado entre los fabricantes que facilitan catálogos (databooks) con las características de funcionamiento. 6. Subfamilia: Es el identificador de la subfamila a la que pertenece el IC. 7. Margen de temperatura: Se corresponden con los identificadores 54 y 74 para TTL o con 40 y 45 para CMOS. 8. Nomenclatura del fabricante: Es un identificador propio del fabricante para identificar a toda una serie de sus productos. 9. Identificación de la patilla (pin) número 1: Cada patilla de un IC tiene una función exclusiva y, por lo general, no puede intercambiar con otras. Identificada la patilla número 1, los números del resto de patillas se obtienen contándolos en sentido anti horario. No respetar el patillaje puede resultar fatal a la hora de conectar un IC. Tomemos como ejemplo el circuito 7408 que tiene integradas cuatro puertas AND de dos entradas. A partir de la hoja de características en el manual correspondiente y una vez identificados sus pines, podemos saber la distribución de dichas puertas dentro del IC. 4 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez A continuación se muestra una los símbolos, capsula y distribución de pines de algunas compuestas. 74LS00 74LS04 74LS08 74LS32 74LS86 74LS14 74LS10 74LS11 5 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez 3.- PRE-INFORME 3.1.- Investigue las características de las compuertas con tecnología TTL y CMOS. 3.2.- Realizar el esquema eléctrico para probar el funcionamiento y verificar la tabla de verdad de los circuitos integrados 74LS04 (6 compuertas NOT), 74LS14(6 compuertas NOT smith triger), 74LS08 (4 compuertas AND), 74LS32 (4 compuertas AND), 74LS00 (4 compuertas AND,.74LS86 (4 compuertas AND). Indicar los niveles de las fuente de alimentación a utilizar. 3.3.- Para el circuito de la figura 3.1 graficar la forma de onda de la salida “S” si en el interruptor “SW” se introducen los niveles logicos que se muestran a continuación: SW Fig. 3.1 3.4.- Para el circuito de la figura 3.2 obtener la tabla de verdad para las salidas “S1” y “S2” en función de A, B, y C. Fig. 3.2 3.5.- Para el circuito de la figura 3.3 obtener la tabla de verdad para las salidas “S1” y “S2” en función de A, B, y C. 6 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez Fig. 3.3 3.6.- Para el circuito de la figura 3.4 obtener la tabla de verdad para la salida “S1” en función de A y B. Indicar a que compuerta conocida corresponde la tabla de verdad de este circuito. Fig. 3.4 7 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez 4. LABORATORIO 4.1.- Compruebe el funcionamiento de las compuertas lógicas NOT, OR, AND verificar y llenar las tablas de verdad correspondiente. In 1 0 Dibuja el Lay-Out del 7404 y verifica las compuertas Out Dibuja el Lay-Out del 7432 y verifica las compuertas A 0 0 1 1 B 0 1 0 1 Out Dibuja el Lay-Out del 7408 y verifica las compuertas A 0 0 1 1 B 0 1 0 1 Out 4.2.- Verificacion del retardo. Conecte los seis inversores del 7404 en cascada, la salida será la misma que la entrada excepto que se retardará la señal por le tiempo que necesita la señal para propagarse a través de los seis inversores. Obtener el retardo promedio de propagación por inversor utilizando el osciloscopio. Circuito Implementado Retardo Promedio 4.3.- Arme el circuito dela figura 3.1, compruebe la salida de “S” introduciendo los niveles logicos indicados en el punto 3.3. 4.4.- Arme el circuito dela figura 3.2, y verifique practicamente las tablas de verdad para las salidas “S1” y “S2” del punto 3.4 del preinforme. 8 LABORATORIO SISTEMAS DIGITALES I (LETN-601) Ing. Jose Luis Apaza Gutierrez 4.5.- Arme el circuito dela figura 3.3, y verifique practicamente las tablas de verdad para las salidas “S1” y “S2” del punto 3.5 del preinforme. 4.6.- Arme el circuito dela figura 3.4, y verifique practicamente las tablas de verdad para las salidas “S1” y “S2” del punto 3.6 del preinforme. Armar el circuito para verificar el funcionamiento de la compuerta EXOR (74LS86) verificar su funcionamiento. Compare la salida de la compuerta EXOR y el circuito de la figura 3.4. 5. INFORME 5.1.- Para cada punto del laboratorio realice una comparación entre los resultados que se obtuvo en laboratorio y los datos teóricos. 5.2.- Indique las conclusiones del laboratorio. 6. BIBLIOGRAFÍA - Fundamentos de electronica digital, Thomas L. Floyd - Diseño Digital, Morris Mano - Análisis y Diseño de Circuitos Lógicos Digitales, Nelson, V., Troy, Prentice Hall, 1996. - Sistemas electrónicos digitales, Enrique mandado - Teoría de conmutación y diseño lógico, Hill Peterson, Limusa, 1978 - Manuales: TTL Data Book National, CMOS data Book National 9