Paradigma de paso de mensajes

Anuncio

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Paradigma de paso de mensajes

Curso 2011-2012

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

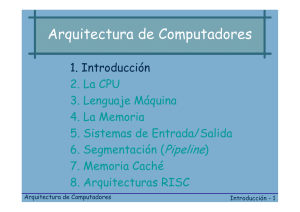

Índice

• Visión lógica del paradigma de paso de

mensajes.

• Operaciones básicas en paso de mensajes.

• Operaciones bloqueantes.

• Operaciones no bloqueantes.

• MPI: the Message Passing Interface.

• Casos reales: Intel Paragon y Meiko CS-2.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Visión lógica del paradigma de paso de mensajes

• Espacio de memoria distribuido:

– p procesadores, cada uno con su espacio de direcciones exclusivo.

– Es preciso un reparto de los datos de entrada a cada procesador.

– Conlleva más dificultas y trabajo manual, pero favorece el principio

de proximidad espacial: crítico en sistemas NUMA.

• Toda comunicación implica dos procesadores:

– El procesador que envía los datos tiene que gestionar la

comunicación aunque no tenga implicación directa en el cálculo del

procesador destino.

– La necesidad de sincronización dificulta la programación.

• Paralelismo explícito:

– La tarea de descomposición y paralelización de código se hace de

forma manual por el programador: tiende a ser complicado.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones básicas en paso de mensajes

• Si P0 tiene un HW dedicado de comunicaciones, la transmisión se

puede realizar tras la modificación de a, recibiendo P1 un valor

incorrecto: Problemas de sincronización.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones básicas en paso de mensajes

• A la hora de evitar problemas de sincronización,

se establecen dos mecanismos de comunicación:

– Operaciones bloqueantes: Cuando un procesador

encuentra una operación de comunicación, se bloquea

hasta que acaba de realizarse. Degrada el

rendimiento.

– Operaciones no-bloqueantes: Cuando un procesador

encuentra una operación de comunicación, sigue

adelante protegiendo la información que se va a

trasmitir, hasta que dicha operación se produce.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones bloqueantes sin buffer

• Si el emisor y el receptor ejecutan la operación de comunicación

en instantes próximos, el rendimiento es bueno.

• Sin embargo, si ambos la ejecutan con una cierta diferencia

temporal, el rendimiento se degrada mucho. Esta es la situación

normal en entornos asíncronos.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones bloqueantes sin buffer: Interbloqueos

P0

P1

send (&a, 1, 1);

receive (&b, 1, 1);

send (&a, 1, 0);

receive (&b, 1, 0);

• En operaciones bloqueantes sin buffer, se pueden producir

situaciones de interbloqueo.

• Los dos procesos se suspenden indefinidamente.

• La reorganización del código para evitar estas situaciones hace

que los programas sean complejos.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones bloqueantes con buffer

Con HW dedicado

Sin HW dedicado (copia directa a

buffer destino)

• Cuando el emisor encuentra una operación de comunicación,

copia los datos a un buffer. Al acabar esta copia, continúa con la

ejecución normal, sin riesgo de datos.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones no-bloqueantes sin buffer

• En las operaciones no bloqueantes, el emisor realiza una petición de

comunicación, y sigue la ejecución normal. En esta etapa, las variables

comunicadas están protegidas.

• Cuando el receptor está listo, manda una interrupción y se produce la

comunicación.

• Al final de la comunicación, las variables comunicadas dejan de estar

protegidas y son modificables.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones no-bloqueantes con buffer

• En las operaciones no-bloqueantes con buffer, el emisor inicia una

operación de DMA (hacia el buffer) y regresa inmediatamente a la

ejecución normal del proceso.

• Los datos pasan a ser seguros (desprotegidos) en el momento en que la

operación de DMA se completa (se han escrito en el buffer).

• El receptor inicia un proceso de comunicación desde el buffer inicial al

propio.

• Ventaja frente a operación no-bloqueante sin buffer: Los datos están

protegidos durante menos tiempo, ya que se liberan en cuanto se

almacenan en el buffer.

• Ventaja frente a operación bloqueante con buffer: La tarea de escritura

en buffer se realiza por DMA y la CPU queda libre para continuar con

la ejecución normal inmediatamente.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

MPI: the Message Passing Interface

• Inicialmente, cada fabricante proporcionaba un conjunto de rutinas

paralelas propias.

• La falta de estandarización producía muchos problemas a la hora de

portar código, por lo que se llevaron a cabo varias iniciativas de

integración. Una de estas iniciativas dio lugar a MPI.

• MPI define una biblioteca estándar para el paso de mensajes, que puede

ser utilizada a la hora de desarrollar programas portables en lenguajes

estándar como C o Fortran.

• Consta de 125 rutinas, pero todo programa se puede escribir en función

de únicamente 6:

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Operaciones de comunicación estándar en MPI

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Ejemplo de programa SPMD en MPI

#include <stdio.h>

#include <string.h>

#include “mpi.h”

main (int argc, char* argv[])

{

int

my_rank; /* Id del procesador que ejecuta el proceso */

int

p; /* Número de procesadores accesibles */

int

source;

int

dest;

int

tag=0; /* Id de la comunicación */

char message[100]; /* Mensaje con valor inicial */

MPI_Status

status;

MPI_Init (&argc, &argv);

MPI_Comm_rank (MPI_COMM_WORLD, &my_rank);

MPI_Comm_size (MPI_COMM_WORLD, &p);

if (my_rank != 0)

{

sprintf (message, “Saludos del proceso %d !”, my_rank);

dest = 0;

MPI_Send (message, strlen(message+1), MPI_CHAR, dest, tag, MPI_COMM_WORLD);

}

else

for (source=1; source<p; source++)

{

MPI_Recv(message, 100, MPI_CHAR, source, tag, MPI_COMM_WORLD, &status);

printf (“%s \n”, message);

}

MPI_Finalize();

}

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Organización orientada a paso de mensajes

Cada nodo suele tener un procesador de comunicación dedicado (CP) que

realiza las transferencias ordenadas por el procesador principal a través del

interfaz de red (IN).

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Caso real: Intel Paragon

Cada nodo contiene 2 ó más procesadores i860XP a 50 MHz, un interfaz de red,

memoria de 16 ó 32 Mb, bus de 64 bits a 400 Mb/s y dos unidades de DMA para

transferencia rápida.

AT5128 – Arquitectura e Ingeniería de Computadores II

Juan Antonio Maestro (2004/05)

Caso real: Meiko CS-2

El CP (procesador de comunicaciones), se descompone en varios procesadores

físicos dedicados para ejecutar comandos de I/O (cmd), gestionar las entradas y

salidas (out, in, reply), los eventos (event) y la traducción de direcciones (V→P).