Memorias

Anuncio

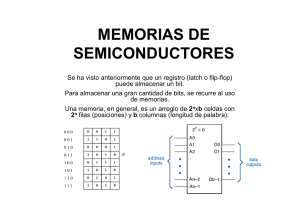

Memorias Índice Características: escritura y persistencia Tipos de memorias Construcción de memorias Jerarquía de memorias RAM avanzada Memorias Almacenamiento de bits m x n: m palabras de n bits Señales de direcciones k = Log2(m) o m = 2^k posiciones Ej: memoria 4096 x 8: 32,768 bits 12 líneas de direcciones 8 líneas de datos Señales de acceso a memoria RD/WR: lectura o escritura Enable o chip select: habilitación Multipuerto: accesos simultáneos a diferentes posiciones También acceso serie o paralelo Estructuras de memorias Memoria m × n … R/W Memoria 2k × n /CS A0 m posic iones … … Ak-1 … n bits por posición Qn-1 Q0 Persistencia Escritura y persistencia ROM Vida del producto OTP ROM EPROM Decenas de años Duración de la batería (~10 años) Memoria ideal EEPROM FLASH NVRAM No volátiles Programables en campo Casi nada SRAM/DRAM Escritura En la ProgramadorProgramador En campo En campo fabricación (1 vez) (1000s veces) (1000s) (1000s ciclos) por bloques En campo sin límite de ciclos Escritura Capacidad de escritura Alta Media Es necesario un “programador” (equipo específico) Ej: EPROM, OTP ROM Nula El micro escribe a la memoria, más lentamente Ej: FLASH, EEPROM Baja El micro escribe a la memoria de forma directa, rápida y fácil Ej: RAM Sólo se escribe durante la fabricación Ej: ROM de máscara Programación en campo El micro puede escribir en el funcionamiento normal del sistema Memorias en el nivel alto o medio de capacidad Persistencia Persistencia del almacenamiento Alta Media La información permanece mientras haya alimentación Ej: SRAM Muy baja La información se mantiene durante días, meses o años sin alimentación Ej: NVRAM Baja Nunca pierde la información Ej: ROM de máscara La información se empieza a perder justamente tras ser escrita Ej: DRAM Memoria no volátil Mantiene la información sin alimentación Nivel alto o medio de persistencia ROM: Read-Only Memory Memoria no volátil Se puede leer en campo, pero no escribir Lo normal es escribirla antes de insertarla en el sistema Usos Programa (software )de un sistema empotrado Cada instrucción puede ocupar una o más direcciones Constantes necesarias en el sistema o LUTs Circuito combinacional Ejemplo: ROM 8x4 Horizontal = palabra Vertical = dato Sólo hay conexiones en los puntos Si A=010, el DEC pone a la línea horiz. 2 a 1 Las líneas de datos Q3 y Q1 se ponen a 1 por las conexiones programadas con la línea 2 La línea 2 no está conectada con Q2 ni Q0 La salida es 1010 Internal view 8 × 4 ROM enable word 0 3×8 decoder word 1 word 2 A0 A1 A2 word line data line programmable connection wired-OR Q3 Q2 Q1 Q0 ROM de máscara Las conexiones se programan al fabricarse Más baja capacidad de escritura 1 vez Más alta persistencia Máscaras de fotolitografía Nunca pierde la información salvo daño físico Se usa para el producto final en grandes tiradas OTP ROM Las conexiones se programan por el usuario Fichero de conexiones. Programador de ROM Cada conexión programable es un fusible Donde no debe haber conexión el fusible se funde Capacidad escritura muy baja Persistencia muy alta Sólo una vez Los bits permanecen mientras no se fundan más fusibles Usada en producto final Barata, difícil de modificar accidentalmente EPROM Transistor MOS programable (FAMOS) floating gate Puerta flotante y aislante drain source (a) Los electrones forman el canal. Se almacena un 1 (b) Tensión alta en la puerta. Los electrones quedan atrapados en la puerta flotante. El transistor no conduce. Se almacena un 0 (c) (Borrado) UV en la puerta flotante. Los electrones vuelven al canal. Se vuelve a almacenar un 1 +15V (b) source drain (d) Chip EPROM con ventana 5-30 min Se puede borrar y programar miles de veces source (c) Persistencia media (a) Capacidad de escritura media 0V Persiste 10 años, pero es sensible a la radiación y al ruido eléctrico Se usa en la fase de diseño (d) drain EEPROM Programación y borrado eléctrico Tensión más elevada Se pueden borrar palabras o bloques de una vez Capacidad de escritura Programable en campo si hay un circuito de generación de tensiones altas Muy lentas de programar y borrar Suelen tener un controlador de memoria para gestionar el ciclo de programación Suelen tener una señal de “ocupado” Se pueden programar y borrar decenas de miles de veces Persistencia 10 años (como EPROM) Mucho más caras que EPROM Flash Extensión de las EEPROM Similar estructura de puerta flotante, aunque diferente efecto físico Misma capacidad de escritura y persistencia Borrado rápido La escritura puede ser más lenta Se pueden borrar bloques (decenas de kilobits) de una vez Leer bloque, modificar un valor, escribir el bloque entero Se usa en sistemas que necesiten gran capacidad de almacenamiento Ej: cámaras digitales, móviles, grabadores vídeo,... Flash NAND y NOR NAND: mayor densidad (aprox. el doble), menor tiempo de escritura, acceso secuencial o por bloques Memoria de almacenamiento NOR: mucho menor tiempo de lectura, acceso aleatorio Memoria de arranque o de ejecución RAM Memoria volátil La información se pierde si falla la alimentación e xt er n al 2k × n read and vi write memory e w r/w enable A0 … Ak-1 … Fácil lectura y escritura en funcionamiento Qn-1 Q0 internal view I3 I2 I1 I0 La estructura interna es más compleja 4×4 RAM enable 2×4 decoder A0 A1 rd/wr Memory cell To every cell Q3 Q2 Q Q 1 0 Tipos de RAM SRAM: Static RAM Cada bit se almacena en un biestable 6 transistores por bit Mantiene el dato si hay alimentación SRAM Data' Data W DRAM: Dynamic RAM Se usa un transistor y un condensador por bit Mucho más compacta que SRAM Necesita refresco debido a las pérdidas del C Las celdas se refrescan al leerse Tiempo de refresco típico 15.625us Más lentas que SRAM DRAM Data W Estructura interna RAM Expansión de memorias Expansión del tamaño de palabra Expansión de la capacidad RAM avanzada Hoy día DRAM es la memoria principal en la mayoría de sistemas empotrados (alta capacidad, bajo coste) Variantes de DRAM Mejora al mismo ritmo que la velocidad de los micros FPM DRAM: Fast Page Mode DRAM EDO DRAM: Extended Data Out DRAM SDRAM/ESDRAM: Synchronous and Enhanced Synchronous DRAM. SDR, DDR, DDR2, DDR3, DDR4 RDRAM: RAMBUS DRAM DRAM El circuito de refresco se deshabilita en los ciclos de lectura o escritura address Sense Amplifiers cas ras Col Decoder cas,ras, clock Lee direcciones consecutivas periódicamente, forzando el refresco de las celdas Refresh Circuit Row Decoder rd/wr ColAddr . Bufer El circuito de refresco puede ser externo o interno data RowAddr.Bufer Se captura la fila y la columna, secuencialmente, indicado por las señales RAS y CAS DataIn Bufer Bus de direcciones multiplexado en filas y columnas DataOut Bufer Bit storage array Problemas con DRAM La SRAM se integra en el chip del micro Pero la DRAM no: Proceso de fabricación diferente En la fabricación CMOS normal: En la fabricación de DRAM: Se trata de minimizar las capacidades parásitas para reducir las pérdidas y los retrasos Se trata de hacer condensadores grandes Hay algunos procesos capaces de integrar ambos Memory Management Unit (MMU) Trata los detalles de acceso a DRAM Señales RAS, CAS y otras Mapeado direcciones lógicas a físicas Muchos micros la traen ya integrada Permite el acceso a DRAM de forma transparente al programador