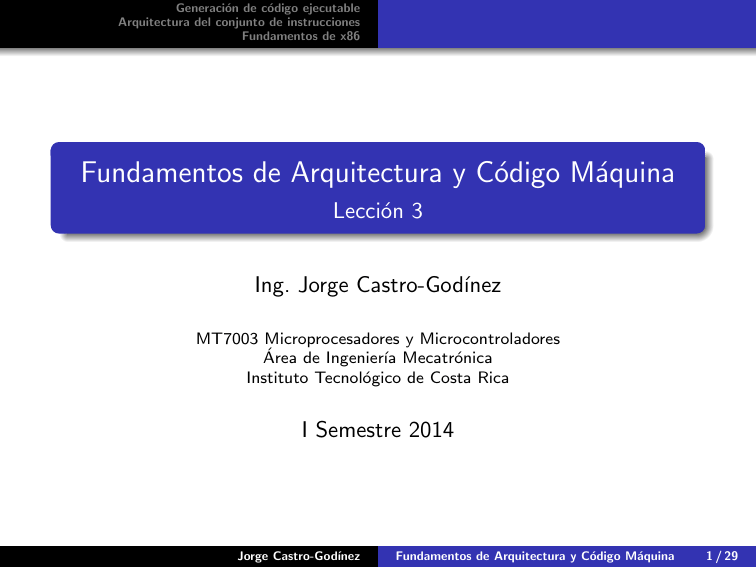

Fundamentos de Arquitectura y Código Máquina

Anuncio

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Fundamentos de Arquitectura y Código Máquina

Lección 3

Ing. Jorge Castro-Godı́nez

MT7003 Microprocesadores y Microcontroladores

Área de Ingenierı́a Mecatrónica

Instituto Tecnológico de Costa Rica

I Semestre 2014

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

1 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Contenido

1

Generación de código ejecutable

2

Arquitectura del conjunto de instrucciones

3

Fundamentos de x86

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

2 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

¿En qué se parecen estos bloques?

(1)

if (x != 0) y = (y+z)/x;

cmpl

je

movl

movl

leal

movl

sarl

idivl

movl

$0, -4(%ebp)

.L2

-12(%ebp), %eax

-8(%ebp), %edx

(%edx, %eax), %eax

%eax, %edx

$31, %edx

-4(%ebp)

%eax, -8(%ebp)

Jorge Castro-Godı́nez

1000001101111100001001000001110000000000

0111010000011000

10001011010001000010010000010100

10001011010001100010010100010100

100011010000010000000010

1000100111000010

110000011111101000011111

11110111011111000010010000011100

10001001010001000010010000011000

Fundamentos de Arquitectura y Código Máquina

3 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

¿En qué se parecen estos bloques?

(2)

if (x != 0) y = (y+z)/x;

!*

cmpl

je

movl

movl

leal

movl

sarl

idivl

movl

$0, -4(%ebp)

.L2

-12(%ebp), %eax

-8(%ebp), %edx

(%edx, %eax), %eax

%eax, %edx

$31, %edx

-4(%ebp)

%eax, -8(%ebp)

"#

#

$*

1000001101111100001001000001110000000000

0111010000011000

10001011010001000010010000010100

10001011010001100010010100010100

100011010000010000000010

1000100111000010

110000011111101000011111

11110111011111000010010000011100

10001001010001000010010000011000

Realmente se trata de una misma lı́nea de código.

El HW entiende en 1’s y 0’s. Sin embargo no es un lenguaje

“amigable” para el ser humano.

Las instrucciones en lenguaje máquina son mucho más cortas

que el número de bits que se necesitarı́an para representar los

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

4 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Interfaz HW/SW: Perspectiva histórica

El HW inicialmente fue muy primitivo.

Diseños de HW eran costosos. Las instrucciones debı́an ser

muy simples.

E.g., una sola instrucción para sumar dos enteros.

El SW también era bastante primitivo.

Las primitivas de SW reflejaban el HW de una manera muy

cercana.

Architecture Specification (Interface)

Hardware

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

5 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Interfaz HW/SW: Ensambladores

Los ensambladores facilitaron la vida, por mucho...

1 instrucción en ensamblador = 1 instrucción en lenguaje

máquina

Las instrucciones en ensamblador son cadenas de caracteres.

Más fácil de leer y escribir para los humanos.

Uso de nombres simbólicos.

Assembler specification

User

program

in

asm

Assembler

Jorge Castro-Godı́nez

Hardware

Fundamentos de Arquitectura y Código Máquina

6 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Interfaz HW/SW: Lenguajes de alto nivel

Un mayor nivel de abstracción

La complejidad de los programas creció.

1 lı́nea de código en un lenguaje de alto nivel podrı́a ser

compilado en muchas lı́neas de lenguaje ensamblador.

C language specification

User

program

in C

C

compiler

Jorge Castro-Godı́nez

Assembler

Hardware

Fundamentos de Arquitectura y Código Máquina

7 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Interfaz HW/SW: escritura, compilación y ejecución

:+6%*>#=%*

:+=?#2%*>#=%*

User

program

in C

C

compiler

.c file

Jorge Castro-Godı́nez

R4"*>#=%*

Assembler

Hardware

.exe file

Fundamentos de Arquitectura y Código Máquina

8 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Rendimiento en la traducción de programas

¿De que depende el tiempo requerido para traducir un

programa?

Del programa mismo, por ejemplo si está escrito en C.

Del compilador: cuál es el conjunto (set) de instrucciones

traduce del programa en C.

De la arquitectura del conjunto de instrucciones (ISA,

Instruction Set Architecture): cuál es el conjunto de

instrucciones disponible para el compilador.

La implementación de hardware: cuanto tiempo toma

ejecutar las instrucciones.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

9 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Arquitectura del Conjunto de Instrucciones

El ISA define:

El estado del sistema: registros, memoria, contador de

programa.

Las instrucciones que el CPU puede ejecutar.

El efecto que cada una de las instrucciones tiene en el estado

del sistema.

CPU

PC

Memory

Registers

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

10 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Desiciones de diseño de los ISA

Instrucciones

¿Qué instrucciones estarán disponibles? ¿Qué hacen estas

instrucciones?

¿Cómo estarán codificadas estas instrucciones?

Registros

¿Cuántos registros habrán?

¿Qué tamaño tendrán los registros?

Memoria

¿Cómo se especificarán las ubicaciones en memoria?

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

11 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

x86

Aquellos procesadores que implementan el ISA de x86

completamente, dominan el mercado de los servidores, las pc

de escritorio y laptop.

Diseño evolucionario:

Compatibilidad hacia atrás hasta 8086 (de 1978)

Cada vez se han agregado más funcionalidades en el tiempo.

CISC: Complex Instruction Set Computer

Muchas diferentes instrucciones con muchos diferentes

formatos.

Solo un conjunto pequeño de estas instrucciones se encuentran

en programas en Linux.

Instrucciones más complejas pero capaces de realizar cosas

complejas.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

12 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Evolución de x86

Nombre

8086

386

Pentium 4F

Año

1978

1985

2005

Transistores

29k

275k

230M

MHz

5-10

16-33

2800-3800

Evolución de 16, 32 y 64 bits.

Capacidades para emplear sistemas operativos complejos,

como los basados en Unix, fue posible.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

13 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Procesadores x86

486

Pentium

Pentium/MMX

Pentium Pro

Pentium III

Pentium IV

Core 2 Duo

Core i7

(1)

1989

1993

1997

1995

1999

2001

2006

2008

1.9M

3.1M

4.5M

6.5M

8.2M

42M

291M

731M

Funcionalidades se han agregado en el tiempo.

Instrucciones para soportar funcionalidades multimedias.

Operaciones en paralelo de 1, 2 y 4 bytes de datos.

Instrucciones para mejorar la eficiencia de operaciones

condicionales.

Más núcleos! Fin del escalamiendo de Dennard y de la ley de

Moore.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

14 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Procesadores x86

Jorge Castro-Godı́nez

(2)

Fundamentos de Arquitectura y Código Máquina

15 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Evolución de los Procesadores

100,000

Performance (vs. VAX-11/780)

10,000

Intel Xeon 6 cores, 3.3 GHz (boost to 3.6 GHz)

Intel Xeon 4 cores, 3.3 GHz (boost to 3.6 GHz)

Intel Core i7 Extreme 4 cores 3.2 GHz (boost to 3.5 GHz)

24,129

Intel Core Duo Extreme 2 cores, 3.0 GHz

21,871

19,484

Intel Core 2 Extreme 2 cores, 2.9 GHz

14,387

AMD Athlon 64, 2.8 GHz

11,865

AMD Athlon, 2.6 GHz

Intel Xeon EE 3.2 GHz

7,108

6,043 6,681

Intel D850EMVR motherboard (3.06 GHz, Pentium 4 processor with Hyper-Threading Technology)

4,195

IBM Power4, 1.3 GHz

3,016

Intel VC820 motherboard, 1.0 GHz Pentium III processor

1,779

Professional Workstation XP1000, 667 MHz 21264A

1,267

Digital AlphaServer 8400 6/575, 575 MHz 21264

993

AlphaServer 4000 5/600, 600 MHz 21164

649

Digital Alphastation 5/500, 500 MHz

481

Digital Alphastation 5/300, 300 MHz

280

Digital Alphastation 4/266, 266 MHz

183

IBM POWERstation 100, 150 MHz

117

Digital 3000 AXP/500, 150 MHz

80

HP 9000/750, 66 MHz

51

1000

100

10

IBM RS6000/540, 30 MHz

MIPS M2000, 25 MHz

18

MIPS M/120, 16.7 MHz

13

Sun-4/260, 16.7 MHz

9

VAX 8700, 22 MHz

5

24

22%/year

52%/year

AX-11/780, 5 MHz

25%/year

1.5, VAX-11/785

1 1

1978 1980 1982 1984 1986 1988 1990 1992 1994 1996 1998 2000 2002 2004 2006 2008 2010 2012

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

16 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Clones de x86: AMD

Historicamente AMD (Advanced Micro Devices) ha seguido

de cerca a Intel.

Un poco más lentos, pero mucho más baratos

En su momento contrataron diseñadores de circuitos de

Digital Equipment y otras compañias.

Fabricaron el Opteron: fuerte competidor del Pentium 4

Desarrollaron x86-64, su propia extensión de x86 a 64 bits.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

17 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Definiciones

Arquitectura

También se conoce como ISA o arquitectura abstracta.

Las partes del diseño del procesador que deben ser

comprendidas para escribir código en lenguaje ensamblador.

¿Qué es visible para el SW?

Microarquitectura

Es la impementación de la arquitectura o arquitectura

abstracta.

Arquitectura concreta.

¿Es el tamaño de la memoria caché parte de la arquitectura?

¿La frecuencia de operación de núcleo?

¿El número de registros del procesador?

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

18 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Perspectiva del programador de ensamblador

(1)

Memory

CPU

Addresses

PC

Registers

Data

Condition

Codes

Instructions

Object Code

Program Data

OS Data

Stack

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

19 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Perspectiva del programador de ensamblador

(2)

Estado visible al programador.

PC: Program Counter (Contador de programa).

Dirección de la siguiente instrucción a ser ejecutada.

Llamado EIP (IA32) o RIP (x86-64)

Archivo de registros

Altamente usados por los programas para procesar datos.

Códigos de condición

Almacena la información del estado de las operaciones

ariméticas y lógicas recientemente usadas.

Usadas para los saltos condicionales.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

20 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Perspectiva del programador de ensamblador

(3)

Memoria

Arreglos direccionables por bytes.

Código/programa, datos, datos del SO.

Incluye el uso de la pila (stack) usada para soportar

procedimientos.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

21 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Convertir un archivo de C en Código Objeto

Suponga código en archivos p1.c y p2.c

Comando de compilación: gcc -O1 p1.c p2.c -o p

Optimizaciones básicas (-O1)

El resultado queda en p

p

text

C program (p1.c p2.c)

Compiler (gcc -S)

text

Asm program (p1.s p2.s)

Assembler (gcc or as)

binary

Object program (p1.o p2.o)

Static libraries (.a)

Linker (gcc or ld)

binary

Executable program (p)

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

22 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Convertir un archivo de C en Ensamblador

gcc -O1 -S code.c

Produce un archivo code.s

Generated IA32 Assembly

C Code

int sum(int x, int y)

{

int t = x+y;

return t;

}

Jorge Castro-Godı́nez

sum:

pushl %ebp

movl %esp,%ebp

movl 12(%ebp),%eax

addl 8(%ebp),%eax

movl %ebp,%esp

popl %ebp

ret

Fundamentos de Arquitectura y Código Máquina

23 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Disassembly

“Desensamblar”

objdump -d program

Es una herramienta útil para examinar el código objeto.

Puede ser ejecutado sobre archivos .o o binarios finales.

Disassembled

00401040 <_sum>:

0:

55

1:

89 e5

3:

8b 45 0c

6:

03 45 08

9:

89 ec

b:

5d

c:

c3

Jorge Castro-Godı́nez

push

mov

mov

add

mov

pop

ret

%ebp

%esp,%ebp

0xc(%ebp),%eax

0x8(%ebp),%eax

%ebp,%esp

%ebp

Fundamentos de Arquitectura y Código Máquina

24 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Tipos básicos de instrucciones

Realizar funciones aritméticas empleando registros o datos en

memoria.

Transferir/mover información entre registos y memoria

Cargar datos de memoria a registros.

Almacenar datos de los registros a la memoria.

Transferencia de control

Saltos incondicionales desde o hacia procedimientos.

Saltos condicionales.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

25 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

¿Qué es un registro?

Es una ubicación dentro del CPU que almacena una pequeña

cantidad de datos, los cuales pueden ser accesados muy

rápidamente (una vez cada ciclo de reloj).

Entre más pequeño más rápido.

Registros constituyen el corazón/centro de la programación en

ensamblador

Recurso muy importante, pero escaso, en x86.

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

26 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

general purpose

Registros Enteros IA32

%eax

accumulate

%ecx

counter

%edx

data

%ebx

base

%esi

source

index

%edi

destination

index

stack

pointer

base

pointer

%esp

%ebp

32-bits wide

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

27 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

general purpose

Registros Enteros IA32

%eax

%ax

%ah

%al

accumulate

%ecx

%cx

%ch

%cl

counter

%edx

%dx

%dh

%dl

data

%ebx

%bx

%bh

%bl

base

%esi

%si

source

index

%edi

%di

destination

index

%esp

%sp

%ebp

%bp

stack

pointer

base

pointer

16-bit virtual registers

(backwards compatibility)

Instruction Set Architecture

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

28 / 29

Generación de código ejecutable

Arquitectura del conjunto de instrucciones

Fundamentos de x86

Registros x86-64

%rax

%eax

%r8

%r8d

%rbx

%ebx

%r9

%r9d

%rcx

%ecx

%r10

%r10d

%rdx

%edx

%r11

%r11d

%rsi

%esi

%r12

%r12d

%rdi

%edi

%r13

%r13d

%rsp

%esp

%r14

%r14d

%rbp

%ebp

%r15

%r15d

Jorge Castro-Godı́nez

Fundamentos de Arquitectura y Código Máquina

29 / 29