Ejemplo de ejecución de una instrucción de acceso a subrutina

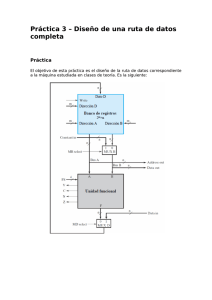

Anuncio

Reloj FP Memoria Princ. PC R0 R1 R2 R3 R4 R5 R6 R7 B 00038AC5 000000FE 00000007 00000027 1 XX DB DA A 3 2 Mux. X 1 XY 2 3 4 Mux. Y Dirección Contenido 00000008 A302001A 0000000C 54345435 D 00000118 0C000C01 0000011C 7400B403 Operador OP 00000234 0B001C01 TP Estado Bus de Direcciones 00001000 00001004 00001008 FD 0000100C FS RM EJECUCIÓN DE LA SECUENCIA CALL TS TRD TD FRA RA A' Banco de Registros CR SP FLM FEM TA TRA Bus de Datos TRM TM TI XE FI I RET PO Unidad de Control RF Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador TE Estado RE CM L E Pedro de Miguel Anasagasti Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S Esta animación presenta la ejecución de una llamada a procedimiento, es decir, la combinación de una instrucción CALL y una RET. R3 00000007 R4 00000027 R5 El programa R6 R7 A' Banco de Registros CR Operador OP a ejecutarEstado es el siguiente: Bus de Direcciones FRA CALL #1A[.R2] RA ADD .R3,.R4 TA TRA TE Mux. XE FI I Comparador =0 <0 Desbord. Acarreo Interr. . Inhib. que Núcl./Usu. es elInt.mismo FEST Estado RE 00000234 0B001C01 TD TRD TS 00001000 00001004 00001008 FD 0000100C FS RM PUSH .R0 SP FLM PUSH.R1 FEM LD .R0#H’B403 Bus de Datos . TI . RF Reloj . PO POP .R0 Unidad deRET Control Señales de Control de la animación “callret1“ DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid TP TRM TM Oscilador DB DA A diferencia con otras animaciones, se ha supuesto que la máquina es Reloj de 32 bits y que los accesos a memoria se FP hacen en un ciclo. La Memoria Princ. PC memoria se direcciona a nivel de byte y existen instrucciones de 16 y CM Dirección Contenido 00000008 yA302001A L palabra 32 bits. Las instrucciones de 16 bits van pareadas en una una 0000000C 54345435 E B A 3 1 2 basta 1desplazar 2 3 4 vez ejecutada laXXprimera, con el registro I para pasar a R0 00000118 0C000C01 XY Mux. X Mux. Y 00038AC5 la segunda, sin necesidad de hacer otra lecturaD de0000011C R1 7400B403 ejecutar memoria. R2 000000FE Control de E/S 1 La animación contempla dos imágenes por ciclo de reloj. La primera corresponde a las señales de control de tipo nivel, mientras que la segunda refleja las señales de carga. Reloj 3 1 2 1 2 3 4 R0 00000118 0C000C01 XX XY Mux. X Mux. Y R1 00038AC5 0000011C 7400B403 D El000000FE contador de programa contiene 8, que corresponde con la dirección R2 OP 00000234 0B001C01 Operador R3 00000007 de00000027 la instrucción CALL.Estado Los registros tiene valoresTPobtenidos R4 00001000 R5 Bus de Direcciones 00001004 anteriormente, en concreto destacamos que el puntero de pila SP = R6 00001008 TS R7 TRD TD FD 0000100C FRA .H’104 RA A' Banco de FS Registros CR SP RM FLM DB DA El contador de fases se inicializa cuando seFPrealiza la decodificación de Memoria Princ. PC la instrucción, puesto que es desde este instante cuando código Contenido de CMel Dirección 00000008 A302001A L operación de la nueva instrucción empieza a actuar. 0000000C 54345435 E B A Obsérvese que lo primero que se hace en el procedimiento es salvar en FEM TRA la pila los registros que sean TA necesarios (instrucciones PUSH), TM TRM Bus de Datos restituyendo sus valores antes de retornar (instrucciones POP). TI XE FI I PO Unidad de Control RF Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 2 Prepara lectura instrucción Se prepara: D PC R0 R1 R2 R3 R4 R5 R6 R7 00000008 PC CM L E FP B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D DB DA Reloj Operador OP Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos TRM 00A34B8F 00000000 45AB98E3 746DE98A TM TI XE FI I PO Unidad de Control RF 2 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE 00000118 0C000C01 0000011C 7400B403 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Dirección Contenido 00000008 A302001A 0000000C 54345435 00000234 0B001C01 TP Estado Memoria Princ. Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 3 Prepara lectura instrucción Se realiza: D PC Se incrementa RF: RF RF + 1 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM TI XE FI I PO Unidad de Control RF 3 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 00000008 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 4 Lectura instrucción Ciclo de memoria Se prepara incremento de PC: PC PC + 4 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 0000000C Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM A302001A TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 3 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 00000008 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 5 Lectura instrucción Ciclo de memoria, se realiza: I M(D) Se realiza incremento de PC: PC PC + 4 Se incrementa RF: RF RF + 1 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 0000000C Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I A302001A 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM A302001A TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 4 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 6 Decodificación instrucción B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM TI XE FI I A302001A PO Unidad de Control RF 4 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 7 Decodificación instrucción Se pone RF a 0: RF 0 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM TI XE FI I A302001A PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 8 Ejecuta instrucción: se salva la dirección de retorno Se prepara la carga de SP en D: D SP Se prepara PC para escribirlo: RM PC B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y OP TP 0000000C Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I A302001A 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM 0000000C TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000008 R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 9 Ejecuta instrucción: se salva la dirección de retorno Se realiza la carga de SP en D: D SP Se realiza la carga de PC en RM: RM PC Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY D Operador Y OP TP 0000000C Bus de Direcciones Estado RA TA TRA TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 00000000 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000104 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos 0000000C TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000104 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 10 Se salva la dirección de retorno e incrementa SP Ciclo de memoria D: M(D) RM Se prepara incremento de SP: SP SP + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000108 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 00000000 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000104 0000104 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000104 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 11 Se salva la dirección de retorno e incrementa SP Ciclo de memoria D: M(D) RM Se realiza incremento de SP: SP SP + 4 Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000108 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 0000104 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000104 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 12 Ejecuta instrucción: calcula dirección y bifurca Calcula dirección bifurcación: PC R2 + desplaz.; D 0000000C PC CM L E FP 000000FE 1 XX 3 2 Mux. X 1 XY D Operador Y+X OP TP 00000118 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 DB DA=2 DA 0000001A 00000104 Reloj R2 + desplaz. Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 13 Ejecuta instrucción: calcula dirección y bifurca Calcula dirección bifurcación: PC R2 + desplaz.; D Se incrementa RF: RF RF + 1 00000118 PC CM L E FP 000000FE 1 XX 3 2 Mux. X 1 XY D Operador Y+X OP TP 00000118 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y Memoria Princ. RF 3 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 DB DA=2 DA 0000001A 00000118 Reloj R2 + desplaz. Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 14 Lectura instrucción Ciclo de memoria Se prepara incremento de PC: PC PC + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 0000011C Bus de Direcciones Estado RA TA TRA TI XE FI I A302001A PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos 0C000C01 TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000118 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 3 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000118 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 15 Lectura instrucción Ciclo de memoria, se realiza: I M(D) Se realiza incremento de PC: PC PC + 4 Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 0000011C Bus de Direcciones Estado RA TA TRA TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos 0C000C01 TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000118 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 4 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 16 Decodificación instrucción 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000118 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 4 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 17 Decodificación instrucción Se pone RF a 0: RF 0 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000118 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 0 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 18 Ejecuta instrucción: se prepara PUSH de R0 Se prepara la carga de SP en D: D SP Se prepara R0 para escribirlo: RM R0 1 XX 3 2 Mux. X 1 XY Operador Y OP TP 0389EFA5 Bus de Direcciones RA TA TRA TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0000000C FEM TM TRM Bus de Datos 0389EFA5 TD FRA Memoria Princ. RF 0 Reloj Oscilador Estado A' Banco de Registros CR TE 2 3 4 Mux. Y D DB DA DA=0 R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 0000011C PC CM L E FP 0389EFA5 00000118 Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 19 Ejecuta instrucción: se prepara PUSH de R0 Se realiza la carga de SP en D: D SP Se realiza la carga de R0 en RM: RM R0 Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY Operador Y OP TP 0389EFA5 Bus de Direcciones RA TA TRA TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos 0389EFA5 TD FRA Memoria Princ. RF 1 Reloj Oscilador Estado A' Banco de Registros CR TE 2 3 4 Mux. Y D DB DA DA=0 R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 0000011C PC CM L E FP 0389EFA5 00000108 Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 20 Ejecuta instrucción: se salva R0 Ciclo de memoria D: M(D) RM Se prepara incremento de SP: SP SP + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 0000010C Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C000C01 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 45AB98E3 TS TRD FD 0000100C 746DE98A 00000108 FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000108 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 21 Se salva R0. Se desplaza I para pasar a la siguiente instrucción Ciclo de memoria D: M(D) RM Se realiza incremento de SP: SP SP + 4 Se desplaza I para ejecutar la otra instrucción Se incrementa RF: RF 1 XX 3 2 Mux. X D Operador Y+4 OP TP 0000010C Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I DI 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 1 XY 00000108 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj RF + 1 Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 22 Decodificación instrucción 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000108 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 23 Decodificación instrucción Se pone RF a 0: RF 0 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 00000108 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 0 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 24 Ejecuta instrucción: se prepara PUSH de R1 Se prepara la carga de SP en D: D SP Se prepara R0 para escribirlo: RM R0 1 XX 3 2 Mux. X 1 XY Operador Y OP TP 00038AC5 Bus de Direcciones RA TA TRA TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 0389EFA5 FEM TM TRM Bus de Datos 00038AC5 TD FRA Memoria Princ. RF 0 Reloj Oscilador Estado A' Banco de Registros CR TE 2 3 4 Mux. Y D DB DA=1 DA R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 0000011C PC CM L E FP 00038AC5 00000108 Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 25 Ejecuta instrucción: se prepara PUSH de R1 Se realiza la carga de SP en D: D SP Se prepara R0 para escribirlo: RM R0 Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY Operador Y OP TP 00038AC5 Bus de Direcciones RA TA TRA TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos 00038AC5 TD FRA Memoria Princ. RF 0 1 Reloj Oscilador Estado A' Banco de Registros CR TE 2 3 4 Mux. Y D DB DA=1 DA R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 0000011C PC CM L E FP 00038AC5 0000010C Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 26 Ejecuta instrucción: se salva R1 Ciclo de memoria D: M(D) RM Se prepara incremento de SP: SP SP + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000110 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 746DE98A 0000010C FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000010C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 27 Ejecuta instrucción: se salva R1 Ciclo de memoria D: M(D) RM Se realiza incremento de SP: SP Se incrementa RF: RF RF + 1 SP + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000110 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000010C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 28 Prepara ectura instrucción Se prepara: D PC 1 XX 3 2 Mux. X 1 XY D Operador OP TP 00000120 Bus de Direcciones Estado RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000010C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 29 Prepara ectura instrucción Se realiza: D PC Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 3 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 30 Lectura instrucción Ciclo de memoria Se prepara incremento de PC: PC PC + 4 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000120 Bus de Direcciones Estado RA TA TRA TI XE FI I 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos 7400B403 TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 3 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 0000011C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 31 Lectura instrucción Ciclo de memoria, se realiza: I M(D) Se realiza incremento de PC: PC PC + 4 Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X 1 XY D Operador Y+4 OP TP 00000120 Bus de Direcciones Estado RA TA TRA TI XE FI I 7400B403 0C010000 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos 7400B403 TD FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 4 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000120 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 32 Decodificación instrucción 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 7400B403 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 4 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000120 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 33 Decodificación instrucción Se pone RF a 0: RF 0 1 XX 3 2 Mux. X 1 XY D Operador OP TP Estado TD RA TA TRA 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 7400B403 PO Unidad de Control Comparador Estado RE =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos Bus de Direcciones FRA A' Banco de Registros CR TE 2 3 4 Mux. Y 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 0 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000120 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 34 Ejecuta instrucción y prepara lectura instrucción siguiente Se prepara carga: R0 Inmediato Se prepara: D PC 1 XX 3 2 Mux. X Operador OP TP Estado TD RA Mux. 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 7400B403 PO Unidad de Control Comparador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST TA TRA 0000B403 Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos Bus de Direcciones FRA TE 2 3 4 Mux. Y D A' Banco de Registros CR Estado RE 1 XY 0000011C B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 0 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000120 PC CM L E FP DB DA=0 DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 35 Ejecuta instrucción y prepara lectura instrucción siguiente Se realiza carga: R0 Inmediato Se prepara: D PC 1 XX 3 2 Mux. X Operador OP TP Estado TD RA Mux. 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TI XE FI I 7400B403 PO Unidad de Control Comparador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST TA TRA 0000B403 Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00A34B8F 00001004 0000000C 00001008 0389EFA5 TS TRD FD 0000100C 00038AC5 00000110 FS SP RM FLM 00038AC5 FEM TM TRM Bus de Datos Bus de Direcciones FRA TE 2 3 4 Mux. Y D A' Banco de Registros CR Estado RE 1 XY 00000120 B A 0000B403 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000120 PC CM L E FP DB DA DA=0 Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 36 Reloj FP Memoria Princ. PC R0 R1 R2 R3 R4 R5 R6 R7 B 1 XX 00038AC5 000000FE 00000007 00000027 DB DA A 3 2 Mux. X 1 XY 2 3 4 Mux. Y Dirección Contenido 00000008 A302001A 0000000C 54345435 D 00000118 0C000C01 0000011C 7400B403 Operador OP 00000234 0B001C01 TP Estado Bus de Direcciones 00001000 00001004 00001008 FD 0000100C FS RM SigueFRAla ejecución del TRD procedimiento TS TD RA A' Banco de Registros CR SP FLM FEM TA TRA Bus de Datos TRM TM TI XE FI I PO Unidad de Control RF Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador TE Estado RE CM L E Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 37 Prepara ectura instrucción Se prepara: D PC B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I PO Unidad de Control RF 2 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 0000011C R0 R1 R2 R3 R4 R5 R6 R7 00000234 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 38 Prepara ectura instrucción Se realiza: D PC Se incrementa RF: RF RF + 1 B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I PO Unidad de Control RF 3 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000234 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 39 Lectura instrucción Ciclo de memoria Se prepara incremento de PC: PC PC + 4 B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 00000238 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos FI I 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0B001C01 TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 3 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000234 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 40 Lectura instrucción Ciclo de memoria, se realiza: I M(D) Se prepara incremento de PC: PC PC + 4 Se incrementa RF: RF RF + 1 B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 00000238 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos FI I 0B001C01 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0B001C01 TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 3 4 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 41 Decodificación instrucción B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 0B001C01 PO Unidad de Control RF 4 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 42 Decodificación instrucción Se pone RF a 0: RF 0 B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 0B001C01 PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 43 Ejecuta instrucción: se prepara la dirección de pila Se prepara decremento de SP y se carga en D: SP B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y–4 OP TP 00000108 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 0000010C SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 0B001C01 PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA SP – 4 Memoria Princ. 00000234 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj SP – 4; DP Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 44 Ejecuta instrucción: se prepara la dirección de pila Se realiza decremento de SP y se carga en D: SP Se incrementa RF: RF RF + 1 B A 0000B403 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y–4 OP TP 00000108 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000108 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 0B001C01 PO Unidad de Control RF 1 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA SP – 4 Memoria Princ. 00000108 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj SP – 4; DP Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 45 Se carga R0. Se desplaza I para pasar a la siguiente instrucción Se lee de memoria y se carga en R0: R0 M(D) 1 XX 3 2 Mux. X D Operador OP Bus de Direcciones RA FLM Mux. FI I DI 1C010000 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0389EFA5 TI XE 00000118 0C000C01 0000011C 7400B403 00001000 00001004 00001008 FD 0000100C FS RM FEM Bus de Datos PO Unidad de Control Comparador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST 00000108 SP TA TRA 0389EFA5 TS TRD TD A' Banco de Registros CR Estado RE TP Estado FRA TE 2 3 4 Mux. Y 1 XY Dirección Contenido 00000008 A302001A 0000000C 54345435 00000108 B A 0000B403 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 1 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA=0 DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 46 Se carga R0. Se desplaza I para pasar a la siguiente instrucción Se lee de memoria y se carga en R0: R0 M(D) Se desplaza I para ejecutar la otra instrucción Se incrementa RF: RF RF + 1 1 XX 3 2 Mux. X D Operador OP Bus de Direcciones RA FLM Mux. FI I DI 1C010000 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0389EFA5 TI XE 00000118 0C000C01 0000011C 7400B403 00001000 00001004 00001008 FD 0000100C FS RM FEM Bus de Datos PO Unidad de Control Comparador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST 00000108 SP TA TRA 0389EFA5 TS TRD TD A' Banco de Registros CR Estado RE TP Estado FRA TE 2 3 4 Mux. Y 1 XY Dirección Contenido 00000008 A302001A 0000000C 54345435 00000108 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 Memoria Princ. RF 2 Reloj Oscilador R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA=0 DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 47 Decodificación instrucción B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000108 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 1C010000 PO Unidad de Control RF 2 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000108 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 48 Decodificación instrucción Se pone RF a 0: RF 0 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000108 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 1C010000 PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000108 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 49 Ejecuta instrucción: se prepara la dirección de pila Se prepara decremento de SP y se carga en D: SP B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y–4 OP TP 00000104 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000108 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 1C010000 PO Unidad de Control RF 0 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA SP – 4 Memoria Princ. 00000108 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj SP – 4; DP Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 50 Ejecuta instrucción: se prepara la dirección de pila Se realiza decremento de SP y se carga en D: SP Se incrementa RF: RF RF + 1 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y–4 OP TP 00000104 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM TI XE FI I 1C010000 PO Unidad de Control RF 1 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA SP – 4 Memoria Princ. 00000104 R0 R1 R2 R3 R4 R5 R6 R7 00000238 PC CM L E FP DB DA Reloj SP – 4; DP Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 51 R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY M(D) 00000238 04B6 PC CM L E FP 2 3 4 Mux. Y D DB DA Reloj M(D); D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I 1C010000 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0000000C TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 1 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 00000104 Se lee de la pila el PC antiguo Se lee de memoria y se carga en D y PC: PC Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 52 R0 R1 R2 R3 R4 R5 R6 R7 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY M(D) 0000000C 04B6 PC CM L E FP 2 3 4 Mux. Y D DB DA Reloj M(D); D Operador OP TP Estado Bus de Direcciones RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I 1C010000 00000234 0B001C01 TRM 00A34B8F 0000000C 0389EFA5 00038AC5 TM 0000000C TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 2 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 0000000C Se lee de la pila el PC antiguo Se lee de memoria y se carga en D y PC: PC Se incrementa RF: RF RF + 1 Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 53 Lectura instrucción Ciclo de memoria, se prepara: I M(D) Se prepara incremento de PC: PC PC + 4 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 00000010 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I 1C010000 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM 54345435 TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 2 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 0000000C R0 R1 R2 R3 R4 R5 R6 R7 0000000C PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 54 Lectura instrucción Ciclo de memoria, se realiza: I M(D) Se realiza incremento de PC: PC PC + 4 Se incrementa RF: RF RF + 1 B A 0389EFA5 00038AC5 000000FE 00000007 00000027 1 XX 3 2 Mux. X 1 XY 2 3 4 Mux. Y D Operador Y+4 OP TP 00000010 Bus de Direcciones Estado RA A' Banco de Registros CR TS TRD TD FRA 00000104 SP FLM Bus de Datos FI I 54345435 00000234 0B001C01 TRM 00A34B8F 00000000 45AB98E3 746DE98A TM 54345435 TI XE 00000118 0C000C01 0000011C 7400B403 PO Unidad de Control RF 3 Reloj Oscilador =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST Mux. Comparador Estado RE TE Dirección Contenido 00000008 A302001A 0000000C 54345435 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Memoria Princ. 0000000C R0 R1 R2 R3 R4 R5 R6 R7 00000010 PC CM L E FP DB DA Reloj Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S 55 Reloj FP Memoria Princ. PC R0 R1 R2 R3 R4 R5 R6 R7 B 00038AC5 000000FE 00000007 00000027 1 XX DB DA A 3 2 Mux. X 1 XY 2 3 4 Mux. Y Bus de Direcciones RA FIN TS TRD SP FLM 00001000 00001004 00001008 FD 0000100C FS RM FEM TA TRA Bus de Datos TRM TM TI FI I PO Unidad de Control RF Reloj Oscilador XE Comparador Estado RE 00000118 0C000C01 0000011C 7400B403 00000234 0B001C01 TD A' Banco de Registros CR =0 <0 Desbord. Acarreo Interr. . Inhib. Int. Núcl./Usu. FEST D TP Estado Mux. Dirección Contenido 00000008 A302001A 0000000C 54345435 Operador OP FRA TE CM L E Señales de Control DA DB OP XX XY ........ Pedro de Miguel Anasagasti - Universidad Politécnica de Madrid Control de E/S