Introducción al VHDL

Anuncio

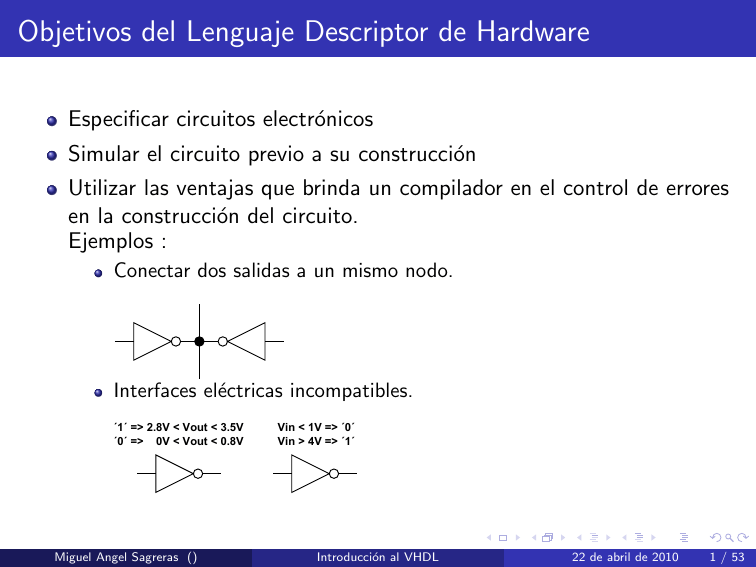

Objetivos del Lenguaje Descriptor de Hardware

Especificar circuitos electrónicos

Simular el circuito previo a su construcción

Utilizar las ventajas que brinda un compilador en el control de errores

en la construcción del circuito.

Ejemplos :

Conectar dos salidas a un mismo nodo.

Interfaces eléctricas incompatibles.

´1´ => 2.8V < Vout < 3.5V

´0´ => 0V < Vout < 0.8V

Miguel Angel Sagreras ()

Vin < 1V => ´0´

Vin > 4V => ´1´

Introducción al VHDL

22 de abril de 2010

1 / 53

El Lenguaje Descriptor de Hardware VHDL

VHDL sigla que significa VHSIC Hardware Description Language.

VHSIC significa Very High Speed Integrated Circuit. Fue un programa

gubernamental del Departamento de Defensa de EE.UU.

Su especificación se encuentra en la NORMA IEEE-1076.

Objetivos:

Normalizar la descripción de los circuitos integrados de aplicación

especı́fica o A.S.I.C provistos al DoD.

Especificar el comportamiento de circuitos digitales pero no su

construcción.

Permite la descripción de los circuitos en base a tres modelos

Comportamiento

Estructural

Data Flow

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

2 / 53

Entidad de diseño

La entidad de diseño es equivalente al encapsulado de los circuitos

integrados.

Define cuáles son sus puertos y los modos de dichos puertos.

Ejemplos de encapsulados:

DIP

Miguel Angel Sagreras ()

SMD

Introducción al VHDL

PLCC

22 de abril de 2010

3 / 53

Ejemplo de diseño

Contador de dos bits de flanco ascendente y con una entrada de reset

asincronica que cuando tenga el valor 1 las salidas deben ponerse en ’0’

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

4 / 53

Encapsulado y entidad de diseño

CONT2

RST

Q1

CLK

Q0

e n t i t y cont2

port (

rst :

clk :

q0

:

q1

:

end ;

in

bit

in

bit

buffer

buffer

;

;

bit ;

bit );

Código VHDL

Diagrama

Miguel Angel Sagreras ()

is

Introducción al VHDL

22 de abril de 2010

5 / 53

Descripción de la Entidad de diseño

Pasos a seguir

Indentificar la entidad con un nombre.

Definir parámetros de construcción generic.

Indentificar y declarar los puertos de acceso port.

Definir los modos de los puertos in, out, inout, etc.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

6 / 53

Descripción de modelos estructural y data flow

Las instrucciones que se utilizan en estos modelos se llaman concurrentes.

La secuencia en que se escriben no afecta el comportamiento del circuito

especificado.

Modelo estructural : se interconectan componentes por medio de las

señales.

Modelo data-flow : se asigna un valor a una señal mediante una

expresión. Tambien se la conoce como Lenguaje de Transferencia de

Registro o RTL.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

7 / 53

Diagrama en bloque

Q0

D

CLK

Q

D

CK

Q

Q1

CK

CLR

CLR

RST

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

8 / 53

Identificación de los nodos de interconexión

D0

Q0

D

CLK

Q

D

CK

Q

Q1

CK

CLR

CLR

RST

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

9 / 53

Identificación de los nodos de interconexión

D0

D1

Q0

D

CLK

Q

D

CK

Q

Q1

CK

CLR

CLR

RST

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

9 / 53

Identificación de unidades de los componentes

D0

D1

Q0

FFD0

D

CLK

Q

CK

CLR

D

Q

Q1

CK

CLR

RST

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

10 / 53

Identificación de unidades de los componentes

D0

D1

Q0

FFD0

D

CLK

Q

CK

CLR

D

Q

CK

CLR

FFD1

RST

Miguel Angel Sagreras ()

Q1

Introducción al VHDL

22 de abril de 2010

10 / 53

Compuertas y componentes

Las compuertas se pueden describir directamente con expresiones

lógicas del propio lenguaje por medio de los operadores not, and, or,

xor, nor, nand.

Los componentes son los equivalentes de los zocalos en donde luego

se conectarán los circuitos integrados representados por la entidad de

diseño.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

11 / 53

Zócalos

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

12 / 53

Declaración de componentes

En el diagrama se tienen dos unidades de un flip-flop D. Se debe declarar

un componente cuyo nombre arbitrario será ffd que luego se referirá a una

entidad que cumpla con la función de dicho flip-flop.

component f f d

port (

c l r : in

ck : i n

d

: in

q

: out

end component ;

Miguel Angel Sagreras ()

Introducción al VHDL

bit

bit

bit

bit

;

;

;

);

22 de abril de 2010

13 / 53

Sintaxis del Cuerpo de arquitectura

a r c h i t e c t u r e nombre o f e n t i d a d i s

C o n j u n t o de d e c l a r a c i o n e s

begin

C o n j u n t o de i n s t r u c c i o n e s

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

14 / 53

Cuerpo de arquitectura del contador de 2 bits

a r c h i t e c t u r e mix o f c o n t 2 i s

s i g n a l d0 , d1 : b i t ;

component f f d

port (

c l r : in b i t ;

ck : i n b i t ;

d

: in b i t ;

q

: out b i t ) ;

end component ;

begin

f f d 0 : f f d p o r t map ( r s t , c l k , d0 , q0 ) ;

f f d 1 : f f d p o r t map ( r s t , c l k , d1 , q1 ) ;

d0 <= not q0 ;

d1 <= q0 xor q1 ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

15 / 53

Pasos a seguir

Realizar un diagrama en bloque.

Identificar los nodos de interconexión.

Declarar los componentes a utilizar.

Declarar las señales que representan los nodos de interconexión.

Interconectar los componentes a través de dichas señales.

Realizar las asignaciones de señales para generar las compuertas

necesarias que acompañen el circuito.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

16 / 53

Especificación completa del contador de dos bits

e n t i t y cont2

port (

rst :

clk :

q0

:

q1

:

end ;

is

in

bit

in

bit

buffer

buffer

;

;

bit ;

bit );

a r c h i t e c t u r e mix o f c o n t 2 i s

s i g n a l d0 , d1 : b i t ;

component f f d

port (

c l r : in

bit ;

ck

: in

bit ;

d

: in

bit ;

q

: ou t b i t ) ;

end component ;

begin

f f d 0 : f f d p o r t map ( r s t , c l k , d0 , q0 ) ;

f f d 1 : f f d p o r t map ( r s t , c l k , d1 , q1 ) ;

d0 <= no t q0 ;

d1 <= q0 x o r q1 ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

17 / 53

Diagrama en bloque completo del contador de dos bits

Entity cont2

Architecture

mix

D0

not

Q0

D1

FFD0

D0

CLK

in

CLK

D

FFD

CK

CLR

RST

in

Miguel Angel Sagreras ()

Q0

Q0

xor

buffer

Q1

FFD1

Q

Q0

D1

CLK

component

instantiation

RST

D

FFD

Q1

Q1

buffer

CK

CLR

RST

Introducción al VHDL

Q

component

instantiation

22 de abril de 2010

18 / 53

Diseño por modelo de comportamiento

El circuito se especifica en base a una secuencia de instrucciones que indica

como sus salidas se modifican en base al valor y/o cambio de sus entradas.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

19 / 53

Entidad de diseño del flip-flop D

FFD

D

Q

CK

CLR

entity ffd is

port (

c l r : in

ck

: in

d

: in

q

: ou t

end ;

;

;

;

);

Código VHDL

Diagrama

Miguel Angel Sagreras ()

bit

bit

bit

bit

Introducción al VHDL

22 de abril de 2010

20 / 53

Descripción por comportamiento

Cuerpo de arquitectura del flip-flop D

a r c h i t e c t u r e beh o f f f d i s

begin

p r o c e s s ( ck , c l r )

begin

i f c l r = ’1 ’ then

q <= ’ 0 ’ ;

e l s i f ck ’ e v e n t and ck = ’1 ’ then

q <= d ;

end i f ;

end p r o c e s s ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

21 / 53

Entidad de simulación

entity testbench i s

end ;

architecture simul

signal clock :

signal reset :

signal tstq0 :

signal tstq1 :

of

bit

bit

bit

bit

testbench i s

;

;

;

;

component c o n t 2

port (

rst : in bit ;

clk : in bit ;

q0

: buffer bit ;

q1

: buffer bit );

end component ;

begin

r e s e t <= ’ 1 ’ , ’ 0 ’ a f t e r 30 n s ;

c l o c k <= no t c l o c k a f t e r 50 n s ;

t e s t c o n t 2 : c o n t 2 p o r t map ( r e s e t , c l o c k , t s t q 0 , t s t q 1 ) ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

22 / 53

Diagrama de tiempos

entity testbench

/testbench/reset

/testbench/clock

/testbench/tstq0

/testbench/tstq1

component testcont2

/testbench/testcont2/rst

/testbench/testcont2/clk

/testbench/testcont2/q0

/testbench/testcont2/q1

/testbench/testcont2/d0

/testbench/testcont2/d1

component ffd0

/testbench/testcont2/ffd0/clr

/testbench/testcont2/ffd0/ck

/testbench/testcont2/ffd0/d

/testbench/testcont2/ffd0/q

component ffd1

/testbench/testcont2/ffd1/clr

/testbench/testcont2/ffd1/ck

/testbench/testcont2/ffd1/d

/testbench/testcont2/ffd1/q

0

100

200

300

400

500

141 ns

Entity:testbench Architecture:simul Date: Thu Aug 17 15:49:27 ART 2006 Row: 1 Page: 1

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

23 / 53

Descripción por comportamiento

El circuito digital se describe en base a una secuencia de instrucciones

que se llaman secuenciales

Las instrucciones secuenciales solo pueden ir dentro de un bloque que

permita su uso. Dichos bloques solo permiten este tipo de

instrucciones y se encuentran en las instrucciones process, function,

procedure

Las instrucciones secuenciales son las siguientes :

if-then-else

case

loop

next

exit

Miguel Angel Sagreras ()

return

wait

asignación de señales

asignación de variables

llamadas a procedimientos

Introducción al VHDL

22 de abril de 2010

24 / 53

Instrucción process

Es una instrucción concurrente. Su bloque de instrucciones permite la

descripción de circuitos en base al modelo de comportamiento.

Sintaxis :

[ etiqueta : ] process [ ( lista de sensibilidad ) ]

declaraciones

begin

instrucciones

end process ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

25 / 53

Instrucción process

Bloque de instrucciones

Pueden ir todas instrucciones secuenciales excepto por la instrucción

return.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

26 / 53

Instrucciones secuenciales

if-then-else

[ etiqueta: ] if condición then

secuencia de instrucciones secuenciales

{ elsif condición then

secuencia de instrucciones secuenciales }

[ else

secuencia de instrucciones secuenciales ]

end if ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

27 / 53

Instrucciones secuenciales

Ejemplo de uso de la instrucción if-then-else

Descripción por medio del modelo de comportamiento el circuito lógico

correspondiente al siguiente mapa de Karnaugh:

X0

X2

X1

X3

00

00

01

1

1

01

11

1

1

11

10

Miguel Angel Sagreras ()

10

1

1

Introducción al VHDL

1

22 de abril de 2010

28 / 53

Ejemplo de uso de la instrucción if-then-else

Entidad de diseño

FUN

X0

X1

X2

O

X3

Miguel Angel Sagreras ()

e n t i t y FUN

port (

x0

x1

x2

x3

o

end ;

Introducción al VHDL

is

:

:

:

:

:

in

in

in

in

out

bit

bit

bit

bit

bit

;

;

;

;

);

22 de abril de 2010

29 / 53

Descripción por comportamiento

a r c h i t e c t u r e compt o f f u n i s

begin

p r o c e s s ( x0 , x1 , x2 , x3 )

begin

o <= ’ 0 ’ ;

i f x0 = ’0 ’ t h e n

i f x2 = ’0 ’

i f x3 = ’0 ’ t h e n

o <= ’ 1 ’ ;

e l s i f x1 = ’1 ’ t h e n ;

o <= ’ 1 ’ ;

end i f ;

e l s i f x3 = ’0 ’ and x1 = ’0 ’ t h e n

o <= ’ 1 ’ ;

end i f ;

else

i f x1 = ’1 ’ t h e n

i f x2 = ’0 ’ and x3 = ’1 ’ t h e n

o <= ’ 1 ’ ;

e l s i f x2 = ’1 ’ and x3 = ’0 ’ t h e n

o <= ’ 1 ’ ;

end i f ;

e l s i f x2 = ’1 ’ and x3 = ’1 ’ t h e n

o <= ’ 1 ’ ;

end i f ;

end i f ;

end p r o c e s s ;

end ;

Miguel Angel Sagreras ()

X0

X2 X1 0 0

X3

00

1

01

01

11

1

1

1

11

10

Introducción al VHDL

10

1

1

1

22 de abril de 2010

30 / 53

Instrucciones secuenciales

Instrucción case

—

—

[ etiqueta : ] case expresión is

when value { value } =>

secuencia de instrucciones secuenciales

{ when value { value } =>

secuencia de instrucciones secuenciales }

end case ;

value puede ser others en referencia el resto de los casos no enumerados.

Ejemplo :

case x i s

when ” 00 ” | ” 11 ” =>

z <= ’ 1 ’ ;

when o t h e r s =>

z <= ’ 0 ’ ;

end c a s e ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

31 / 53

Declaración de tipos

Un tipo se caracteriza por un conjunto de valores y un conjunto de

operaciones.

Por ejemplo

el tipo bit permite tener solo dos valores el ’1‘ y el ’0‘.

Un tipo más concreto permitirı́a poseer otros valores como por ejemplo

0 débil, 1 débil, etc.

Dos tipos distintos podrı́an caracterizar dos interfaces electricas

diferentes.

Los tipos se declaran en la parte declarativa de cualquier instrucción.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

32 / 53

Tipos enumerados

Indica los valores que puede tomar un objeto : signal, variable, constant,

declarado con dicho tipo.

Sintaxis:

—

type identifier is ( emumeration literal {, emumeration literal } )

emumeration literal ::= identifier character literal

identifier es una de las alternativas posibles que puede tener dicho tipo

descripto como un identificador. Ej: TRUE, FALSE

character literal es otra forma de representar una alternativa como un

caracter. Ej: ’1‘, ’0‘.

Ejemplos :

type bit is ( ’0‘, ’1’) ;

type boolean is ( FLASE, TRUE ) ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

33 / 53

Declaración de variables

Se declaran en la parte declarativa de las instrucciones cuyo bloque sólo pueden

tener instrucciones secuenciales. Ejemplo : process, function, procedure.

Sintaxis :

variable declaration :==

variable idenifier list : subtype indication [ := expression ] ;

identifier list es la lista de variables a declarar. Ej : aux1, aux2.

subtype indication indica el tipo de dato que tendrán las variables de datos

declaradas. Ej : bit .

:= expression inicializa la lista de variables con el valor de la expresión. Ej :

:= ’1‘

Ejemplo :

variable aux : bit := ’1’;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

34 / 53

Asignación de variables

variable assignment statement :==

[ label : ] target := expression ;

target es el nombre de la variable que se quiere asignar. Ej : aux.

expression es una expresión cuyo valor se asignará en la variable. Ej :

cols*rows

Ejemplo :

aux := cols*rows ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

35 / 53

Diagrama en bloque de un circuito de Mealy

X

Q

n

C

O

M

B

I

N

A

C

I

O

N

A

L

O

Q

n+1

M

E

M

O

R

I

A

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

36 / 53

Ejemplo de un circuito de Mealy

Entidad de diseño y Diagrama de estados

X/O

0/1

SEQMLY

X

O

CLK

A

1/0

0/0

e n t i t y seqmly

port (

clk :

x

:

o

:

end ;

is

in

bit ;

in

bit ;

out b i t ) ;

1/0

C

B

1/0

0/0

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

37 / 53

Ejemplo de un circuito de Mealy

Cuerpo de arquitectura y tabla de transiciones

a r c h i t e c t u r e beh o f s e q m l y i s

begin

process ( clk , x )

type e s t a d o s i s ( a , b , c ) ;

variable estado : estados ;

begin

i f c l k = ’1 ’ and c l k ’ e v e n t t h e n

i f x = ’0 ’ t h e n

case estado i s

when a =>

e s t a d o := a ;

when b =>

e s t a d o := c ;

when c =>

e s t a d o := a ;

end c a s e ;

else

e s t a d o := b ;

end i f ;

end i f ;

i f x = ’0 ’ t h e n

case estado i s

when a =>

o <= ’ 1 ’ ;

when o t h e r s =>

o <= ’ 0 ’ ;

end c a s e ;

else

o <= ’ 0 ’ ;

end i f ;

end p r o c e s s ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

X

q

0

1

A

A ,1

B ,0

B

C ,0

B ,0

C

A ,0

B ,0

22 de abril de 2010

38 / 53

Diagrama en bloque de un circuito de Moore

C

O

M

B

I

N

A

C

I

O

N

A

L

X

Q

n

Miguel Angel Sagreras ()

Q

n+1

C

O

M

B

I

N

A

C

I

O

N

A

L

M

E

M

O

R

I

A

Introducción al VHDL

O

22 de abril de 2010

39 / 53

Ejemplo de un circuito de Moore

Entidad de diseño y diagrama de estados

SEQ

00

X

Q(0)

1

1

0

CLK

Q(1)

0

11

01

0

e n t i t y seq

port (

clk

x

q

end ;

0

is

: in

bit ;

: in

bit ;

: out b i t v e c t o r ( 0 t o 1 ) ) ;

Miguel Angel Sagreras ()

1

Introducción al VHDL

1

10

22 de abril de 2010

40 / 53

Ejemplo de un circuito de Moore

Cuerpo de arquitectura y tabla de transiciones

a r c h i t e c t u r e beh o f s e q i s

begin

process ( clk )

v a r i a b l e e s t a d o : b i t v e c t o r ( 1 downto 0 ) ;

begin

i f c l k = ’1 ’ and c l k ’ e v e n t t h e n

i f x = ’0 ’ t h e n

case estado i s

when ” 00 ” =>

e s t a d o := ” 01 ” ;

when ” 01 ” =>

e s t a d o := ” 10 ” ;

when ” 10 ” =>

e s t a d o := ” 11 ” ;

when ” 11 ” =>

e s t a d o := ” 00 ” ;

end c a s e ;

else

case estado i s

when ” 00 ” =>

e s t a d o := ” 11 ” ;

when ” 01 ” =>

e s t a d o := ” 00 ” ;

when ” 10 ” =>

e s t a d o := ” 01 ” ;

when ” 11 ” =>

e s t a d o := ” 10 ” ;

end c a s e ;

end i f ;

q <= e s t a d o ;

end i f ;

end p r o c e s s ;

Miguel Angel Sagreras ()

Introducción al VHDL

X

q

0

1

00

01

11

01

10

00

10

11

01

11

00

10

22 de abril de 2010

41 / 53

Diagrama en bloque de un circuito asincrónico

X

y

c

o

m

b

i

n

a

c

i

o

n

a

l

Z

Y

retardos

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

42 / 53

Ejemplo de un circuito asincrónico

Entidad de diseño y diagrama de estados

ASINC

XY

00

01

11

10

a

b

a

a

0

a

b

c

−−

0

d

c

c

c

1

d

c

−−

a

1

Y

Z

Z

X

entity asinc is

port (

x : in

bit ;

y : in

bit ;

z : out b i t ) ;

end ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

43 / 53

Ejemplo de un circuito asincrónico

Cuerpo de arquitectura

entity asinc is

port (

x : in

bit ;

y : in

bit ;

z : out b i t ) ;

end ;

when o t h e r s =>

null ;

end c a s e ;

when ” 01 ” =>

case estado i s

when a =>

e s t a d o <= b ;

when d =>

e s t a d o <= c ;

when o t h e r s =>

null ;

end c a s e ;

when ” 11 ” =>

case estado i s

when b =>

e s t a d o <= c ;

when o t h e r s =>

null ;

end c a s e ;

when ” 10 ” =>

i f e s t a d o = d then

e s t a d o <= a ;

end i f ;

end c a s e ;

end p r o c e s s ;

a r c h i t e c t u r e beh o f a s i n c i s

type e s t a d o s i s ( a , b , c , d ) ;

si gn al estado : estados ;

begin

process (x , y , estado )

begin

case estado i s

when a | b =>

z <= ’ 0 ’ ;

when c | d =>

z <= ’ 1 ’ ;

end c a s e ;

c a s e b i t v e c t o r ( 0 t o 1 ) ’ ( x&y ) i s

when ” 00 ” =>

case estado i s

when b =>

e s t a d o <= a ;

when c =>

e s t a d o <= d ;

Miguel Angel Sagreras ()

end ;

Introducción al VHDL

22 de abril de 2010

44 / 53

Instrucción loop

loop statement ::=

[ loop label : ] [ iteration scheme ] loop

sequence of statement

end loop ;

—

iteration scheme ::=

while condition

for identifier in discrete range

discrete range indica un rango de valores. Ej : 0 to 9. Los rangos

también pueden ser identificadores que representen un discrete range.

identifier es el nombre de un ı́ndice que puede referenciarse luego

dentro del loop. Alcanza los valores especificados por discrete range.

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

45 / 53

Instrucción next

[ label : ] next [ loop label ] [ when condition ] ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

46 / 53

Instrucción next : Ejemplo I

etiqueta1: loop

etiqueta2: loop

secuencia_de_instrucciones

If ...... then

next;

end if;

secuencia_de_instrucciones

end loop;

secuencia_de_instrucciones

end loop;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

47 / 53

Instrucción next

etiqueta1: loop

etiqueta2: loop

secuencia_de_instrucciones

If ...... then

next etiqueta1;

end if;

secuencia_de_instrucciones

end loop;

secuencia_de_instrucciones

end loop;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

48 / 53

Instrucción exit

[ label : ] exit [ loop label ] [ when condition ] ;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

49 / 53

Instrucción exit : Ejemplo I

etiqueta1: loop

etiqueta2: loop

secuencia_de_instrucciones

If ...... then

exit;

end if;

secuencia_de_instrucciones

end loop;

secuencia_de_instrucciones

end loop;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

50 / 53

Instrucción exit : Ejemplo II

etiqueta1: loop

etiqueta2: loop

secuencia_de_instrucciones

If ...... then

exit etiqueta1;

end if;

secuencia_de_instrucciones

end loop;

secuencia_de_instrucciones

end loop;

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

51 / 53

Descripción de la sintaxis

Los nombres en minúsculas se usan para indicar una categorı́a sintáctica. Por ejemplo:

expression

Las palabras escritas en negritas simbolizan palabras claves. Por ejemplo :

array, port, entity, . . . .

—

Una expresión sintáctica consiste de un lado izquierdo, el sı́mbolo ::= que se puede leer

como “se reemplaza por”, y un lado derecho. El lado izquierdo es una categorı́a sintáctica,

el lado derecho es la regla que lo reemplaza.

—

—

La barra vertical ” ”separa alternativas a menos que ocurra inmediatamente después de la

apertura de una llave ”{”, en ese caso significa él mismo.

letter or digit ::= letter digit

choices ::= chioce { choice }

—

Los corchetes [ ] encierran items opcionales. Las siguientes expresiones son equivalentes.

return statement ::= return [ expression ] ;

return statement ::= return ; return expression ;

—

Las llaves { } encierran items que se repiten en el lado derecho de la expresión. Los items

pueden aparecer cero o más veces. Las siguientes expresiones son equivalentes.

term ::= factor multiplying operator factor

term ::= factor { multiplying operator factor

Miguel Angel Sagreras ()

Introducción al VHDL

22 de abril de 2010

52 / 53