Intel 80486

Anuncio

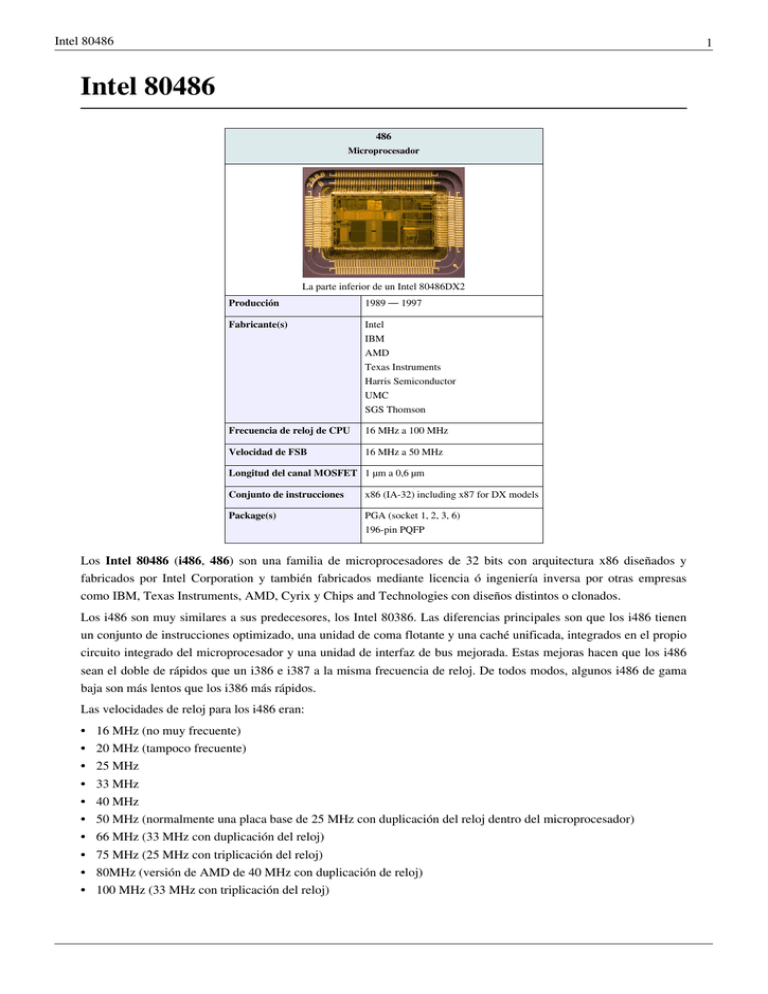

Intel 80486 1 Intel 80486 486 Microprocesador La parte inferior de un Intel 80486DX2 Producción 1989 — 1997 Fabricante(s) Intel IBM AMD Texas Instruments Harris Semiconductor UMC SGS Thomson Frecuencia de reloj de CPU 16 MHz a 100 MHz Velocidad de FSB 16 MHz a 50 MHz Longitud del canal MOSFET 1 µm a 0,6 µm Conjunto de instrucciones x86 (IA-32) including x87 for DX models Package(s) PGA (socket 1, 2, 3, 6) 196-pin PQFP Los Intel 80486 (i486, 486) son una familia de microprocesadores de 32 bits con arquitectura x86 diseñados y fabricados por Intel Corporation y también fabricados mediante licencia ó ingeniería inversa por otras empresas como IBM, Texas Instruments, AMD, Cyrix y Chips and Technologies con diseños distintos o clonados. Los i486 son muy similares a sus predecesores, los Intel 80386. Las diferencias principales son que los i486 tienen un conjunto de instrucciones optimizado, una unidad de coma flotante y una caché unificada, integrados en el propio circuito integrado del microprocesador y una unidad de interfaz de bus mejorada. Estas mejoras hacen que los i486 sean el doble de rápidos que un i386 e i387 a la misma frecuencia de reloj. De todos modos, algunos i486 de gama baja son más lentos que los i386 más rápidos. Las velocidades de reloj para los i486 eran: • • • • • • • • 16 MHz (no muy frecuente) 20 MHz (tampoco frecuente) 25 MHz 33 MHz 40 MHz 50 MHz (normalmente una placa base de 25 MHz con duplicación del reloj dentro del microprocesador) 66 MHz (33 MHz con duplicación del reloj) 75 MHz (25 MHz con triplicación del reloj) • 80MHz (versión de AMD de 40 MHz con duplicación de reloj) • 100 MHz (33 MHz con triplicación del reloj) Intel 80486 2 • 120 MHz (40 MHz con triplicación de reloj, exclusivo de AMD). Existió un 80486 de 133MHz fabricado por AMD denominado Am5x86-P75 que disponía de 16KB de caché L1, arquitectura de 0'35 micras (contra las 0'6 micras de los modelos anteriores), un multiplicador de 4x y FSB de 33 MT/s, del cual se fabricaron también diferentes versiones con diferente voltaje y diferente encapsulación, de 3.3V y 3.45V, posibilitando una enorme capacidad para el overclock que le permitía subir hasta los 160Mhz, equiparando su rendimiento con el de un Pentium-90. Posteriormente AMD diseñó el Am5x86-P75+ de 150Mhz, 16KB de caché L1, multiplicador 3x y FSB de 55 MT/s a 3.45V, haciéndolo el procesador 80486 más potente jamás fabricado, del cual apenas se comercializaron unidades siendo un preciado objeto de colección entre aficionados. El sucesor del microprocesador Intel 80486 es el Intel Pentium. Variantes del i486 Hay varias variantes del diseño básico del i486, entre las que se encuentran: • Intel 80486-DX - la versión modelo, con las características indicadas anteriormente. • Intel 80486-SX - un i486DX con la unidad de coma flotante deshabilitada por defecto de fabricación (más tarde sería deshabilitada aun sin defecto para cubrir la creciente demanda de modelos SX). • Intel 80486-DX2 - un i486DX que internamente funciona al doble de la velocidad suministrada por el reloj externo, a la que funcionan el resto de dispositivos del sistema. Intel 80486-SX / 33 MHz. • Intel 80486-SX2 - un i486SX que funciona internamente al doble de la velocidad del reloj. • Intel 80486-SL - un i486DX con una unidad de ahorro de energía. • Intel 80486-SL-NM - un i486SX con una unidad de ahorro de energía. • Intel 80486DX4 - como un i486DX2 pero triplicando la velocidad interna. • Intel 80487 o 80487-SX - una versión del i486DX diseñado para ser usado como unidad de coma flotante del i486SX. El i487 se instala en el zócalo de coprocesador que se encuentra al efecto en las placas base para i486SX. el cual era un 486DX completo que inhabilitaba el 486SX Arquitectura del 486DX2. • Intel 80486 OverDrive (486SX, 486SX2, 486DX2 o 486DX4) - variaciones de los modelos anteriores diseñados como procesadores de actualización, que tienen un voltaje diferente. Normalmente estaban diseñados para ser empleados en placas base que no soportaban el microprocesador equivalente de forma directa. Duplicación y triplicación de reloj Para no exigir mayor velocidad a las placas base, Intel introdujo la duplicación (y más tarde la triplicación) de frecuencia reloj dentro del integrado. Mientras la placa base y sus comunicaciones con el microprocesador a través de sus pines se realizaba a la frecuencia del reloj, las operaciones internas del microprocesador se realizaban al doble (o al triple) de velocidad. De este modo los bloques de código cargados en la memoria caché interna alcanzaban la máxima velocidad, que bajaba a la mitad (o a un tercio) cuando accedía a la memoria RAM. Intel 80486 Intel designó con el sufijo "2" a los microprocesadores que empleaban duplicación de frecuencia de reloj. La frecuencia indicada en el microprocesador correspondía a la frecuencia ya duplicada. Por ejemplo, el 80486 DX2 de 66 MHz tenía un reloj de 33 MHz en la placa base. El público no informado aceptó el sufijo "2" como un signo de superioridad, y se generalizó la creencia de que un 486 de 66 MHz duplicaba a 132 MHz. De manera aparentemente contradictoria, la mayoría de los test de velocidad mostraban que una PC con un microprocesador de 40 MHz (sin duplicación de velocidad) era más rápido que uno de 50 MHz (25 MHz con duplicación de velocidad). De una manera sorprendente, Intel designó con el sufijo "4" en lugar de "3" a los microprocesadores que empleaban triplicación de frecuencia de reloj, lo que hacía al público no informado sobrestimar la capacidad de estos microprocesadores. De este modo, un 486 de 100 MHz en tenía una frecuencia de reloj de 33 MHz, y la frecuencia triplicada llegaba a 99 MHz. Instrucciones a nivel de aplicación Con respecto al 386 se añadieron tres nuevas instrucciones, dos de ellas están orientadas al uso de sistemas de multiprocesador. En estos es usual acceder a los recursos compartidos y la regulación de estos se hace mediante semáforos. La tercera instrucción añadida tiene por misión facilitar el acceso a banco de datos de otros procesadores como los creados para ser utilizados en ordenadores IBM o equipos con microprocesadores Motorola. Instrucción de permutación de bytes BSWAP reg32 La instrucción BSWAP sirve para invertir el orden de los bytes en una palabra de 32 bits. Convierte una palabra almacenada con el objeto de menor peso en la dirección más baja en otra que tenga los mismos, pero con el octeto de menor peso en la dirección más alta. Proporciona mejor rendimiento en aritmética ASCII y BCD, ya que se procesan 4 octetos en lugar de uno solo. Es una instrucción que solo actúa sobre registros de 32 bits y se ejecuta en un ciclo de reloj. EAX 12345678H BSWAP EAX EAX 78563412H Instrucción de intercambio y suma XADD r/m, reg Usa dos operandos del mismo tamaño 8, 16 ó 32 bits. El segundo debe ser un registro. El primero puede ser un registro o un operando en memoria. Se ejecuta en tres o cuatro ciclos de reloj Ejemplo XADD OPLOP2 ; OP2:=OP1 ; OP1:= OP1 + OP2 IMOTEP ; OP3:=GATO </pre> IMOTEP,IMOTEP,IMOTEP,IMOTEP ERROR LOG Varios procesadores podrían compartir la ejecución de un mismo bucle de instrucciones simplificando el procesamiento en paralelo. Con la nueva instrucción del 486 la codificación sería: 3 Intel 80486 MOV EAX, 1 LOCK XADD N, FAX Instrucción de comparación e intercambio CMPNCHG r m,reg Necesita tres operandos del mismo tamaño 8, 16 ó 32 bits. El segundo debe ser un registro. El primero puede ser un registro o un operando en memoria. El tercero debe ser implícito: el acumulador (AL, AX, EAX, dependiendo del tamaño de los otros operandos). Se ejecuta en seis o siete ciclos de reloj si la comparación resulta cierta o hasta diez si es falsa. CMPXCHG DEST.ORGIA ; IF DEST=ACUM THEN DEST: ORGIA ; ELSE ACUM: =DEST Los señalizadores del registro EFLAGS indican el resultado de la comparación. Si es cierta o, ZF se pone a 1; si no se pone a 0. Se pueden realizar semáforos multivalor, y utilizar las instrucciones wait y signal desde múltiples procesos que pretendan compartir un recurso simultáneamente. MOV EBX. IDENT_DUEÑO BUCLE XOR EAX. EAX LOCK CMPCHG DUEÑO_SEMAFORO. EBX JNZ BUCLE ; Si está ocupado por otro, espera. (Semáforo adquirido: realización de la operación protegida) MOV DUEÑO_SEMAFORO. 0 ; Se libera el semáforo. Nuevas instrucciones a nivel de sistema El 486 tiene cuatro nuevas instrucciones específicas para él, que no existen en el 386. tres de ellas están relacionadas con la caché interna que incorpora el 486 para datos y código. La cuarta se refiere a la caché de la tabla de páginas. Carga y almacenamiento de registros de prueba MOV TRn, reg32 Como en el 486 existen tres nuevos registros relacionados con la caché interna, la función MOV también puede acceder a ellos. Invalidación del contenido de la caché INVD Con esta se invalida totalmente el contenido de la caché interna y se genera un ciclo de bus para indicar que a su vez las cachés externas deban invalidar sus contenidos. La instrucción se ejecuta en cuatro ciclos de reloj. 4 Intel 80486 Invalidación de la caché previa actualización de la memoria WBINVD Con esta se invalida totalmente el contenido de la caché interna y se genera dos ciclos de bus la primera indica a las cachés de tipo de escritura obligada que deberán actualizar la memoria principal. Para indicar a la segunda que a su vez las cachés externas deban invalidar sus contenidos. La instrucción se ejecuta en 5 ciclos de reloj. Invalidación de una entrada de la TLB (Translation Loackside Buffer) Genera una dirección virtual a partir del operando dado e invalida la correspondiente entrada de la caché de la tabla de páginas, la TLB. Invalida la entrada de la TLB que referencia a la página que incluye la dirección del operando en memoria dado. Esta instrucción codifica como INVLPG m y se ejecuta en doce ciclos. Registros de prueba de la TLB Los registros de prueba son una parte formal de la arquitectura 386 tenía para el arqueo del TLB (TR6 Y TR7). El 486 añade otros tres registros más de 32 bits para el control del buen funcionamiento de la caché interna del procesador. El registro TR6 no se ha modificado respecto al del 386. El TR7añade algunos bits más. Estos son: • PCD: Bit PCD de la entrada de la tabla de páginas. • PWT: bit PWD de la entrada de la tabla de páginas. • LRU: cuando se lee este campo se obtiene el valor de los tres bits usados en el algoritmo de reemplazo seudo-LRU de la caché. • PL: Corresponde con el bit HT del TR7 del 386. En el 486 se puede escribir a uno o cero. Registros de prueba de la caché interna • TR3 almacena los datos a transferir a la memoria caché. • TR4 contiene el estado de prueba. • TR5 es el registro de control de prueba de la caché. A todos se accede mediante instrucciones MOV ingresadas a nivel de mayor privilegio (cero). TR4 • • • • Válido: 4 bits de validación para las 4 vías del sector. LRU. V: bit de validación de la vía concreta que ha sido accedida entre las 4 que pertenecen al mismo sector. Etiqueta: fuerza el valor de la etiqueta a la dirección asignada en el campo. TR5 • CTL: • 00: Escritura o lectura de la memoria intermedia de la caché. • 01: Escritura de la caché. • 10: Lectura de la caché. • 11: invalidación de la caché. Se invalidan todas las posiciones. • ENT. En lectura/escritura de la caché selecciona una de las cuatro vías del sector seleccionado. En R/W de la memoria intermedia de la caché, selecciona una de las cuatro dobles palabras que componen la línea. 5 Intel 80486 Tipos de datos • • • • • • • Ordinales Enteros Reales Empaquetados BCD Cadenas de 8, 16 y 32 bit Cadenas de 64 a 4 Gbit Caracteres ASCII de 8 bit Enlaces externos • i486 en la web de Intel [1] (en inglés) • set de instrucciones 486 [2] (en inglés) Referencias [1] http:/ / www. intel. com/ design/ intarch/ intel486/ index. htm [2] http:/ / web. archive. org/ 20051121163920/ home. comcast. net/ ~fbui/ intel. html 6 Fuentes y contribuyentes del artículo Fuentes y contribuyentes del artículo Intel 80486 Fuente: http://es.wikipedia.org/w/index.php?oldid=76410929 Contribuyentes: Alejandrosilvestri, Angelito7, Avm, Bedwyr, CarlosPSY, Cinevoro, Conexxo, DMG, Dodo, Emijrp, GermanX, JavierCastro, Juanmacortes, Kizar, LordT, Matdrodes, Michal.Pohorelsky, Mnts, Murphy era un optimista, Rotlink, Sid, Sr Beethoven, Thunderbird2, Vanbasten 23, 31 ediciones anónimas Fuentes de imagen, Licencias y contribuyentes Archivo:80486dx2-large.jpg Fuente: http://es.wikipedia.org/w/index.php?title=Archivo:80486dx2-large.jpg Licencia: GNU Free Documentation License Contribuyentes: A23cd-s, Adambro, Admrboltz, Artnnerisa, CarolSpears, Denniss, Ghouston, Greudin, Julia W, Kozuch, Martin Kozák, Mattbuck, Rjd0060, Rocket000, 12 ediciones anónimas Archivo:Intel 80486sx.jpg Fuente: http://es.wikipedia.org/w/index.php?title=Archivo:Intel_80486sx.jpg Licencia: Creative Commons Attribution-ShareAlike 3.0 Unported Contribuyentes: User:NaSH Archivo:80486DX2 arch.svg Fuente: http://es.wikipedia.org/w/index.php?title=Archivo:80486DX2_arch.svg Licencia: GNU Free Documentation License Contribuyentes: Appaloosa (Original Diagram), Lucid/Appaloosa (SVG version) Licencia Creative Commons Attribution-Share Alike 3.0 //creativecommons.org/licenses/by-sa/3.0/ 7