Clase Práctica

Anuncio

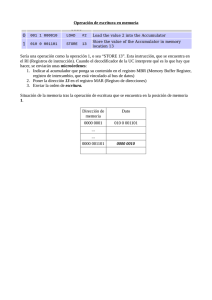

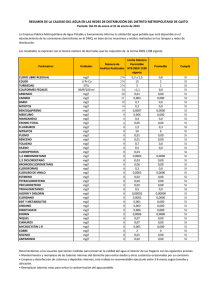

Clase Práctica - caché Organización del Computador 1 Mariano Moscato - Verano 2010 Ejercicio 1 1 Una computadora utiliza una caché de correspondencia directa de 32 lı́neas de 16 palabras cada una. La memoria principal mide 220 palabras y es direccionable a palabra. a) ¿cuántas lı́neas posee la memoria principal? ¿a cuántos bloques corresponde? Solución de Mariano M. Moscato. (10 de noviembre de 2011) La memoria posee 220 palabras. Cada lı́nea de caché es de 16 (24 ) palabras, entonces la 20 memoria tiene 224 = 216 lı́neas. Por otro lado, la caché tiene 32 lı́neas por lo que la memoria estará “dividida” en bloques de 16 32 lı́neas. Si tenemos 216 lı́neas de memoria y bloques de 32 (25 ) lı́neas, tendremos 225 = 211 bloques de memoria. b) Mostrar el formato de una dirección de memoria vista desde la caché (tag, line, index ). ¿Cuáles de estos campos deben guardarse en la caché? Solución de Mariano M. Moscato. (10 de noviembre de 2011) Como la lı́nea es de 16 palabras y se utiliza direccionamiento a palabra, el campo index tendrá 4 bits. Teniendo en cuenta que la caché tiene 32 lı́neas, el campo line tendrá 5 bits. Además sabemos que la memoria está dividida en 211 bloques, por lo que el campo tag tendrá 11 bits. tag 11 bits line 5 bits index 4 bits Sólo debemos guardar el tag. A modo de verificación notemos que la suma de los tamaños de los tres campos da veinte, que es justamente la cantidad de bits necesaria para asignar direcciones a este tipo de memoria (de 220 palabras con direccionamiento a palabra). c) ¿En qué lugar de la caché se guarda la palabra que se encuentra en la dirección de memoria 0x0DB63? Mostrar cómo queda la caché al leer dicha dirección. Solución de Mariano M. Moscato. (10 de noviembre de 2011) Primero, analicemos la dirección 0x0DB63; que en binario serı́a 0000 1101 1011 0110 0011. Escribamos cómo ve esta dirección la caché: 1 Ejercicio 1 del capı́tulo 6, L. Null & J. Lobur, Essentials of Computer Organization and Architecture 1 tag 0000 1101 101 0x6D line 1 0110 0x16 index 0011 0x3 Entonces, luego del pedido, la lı́nea 0x16 de la caché corresponderá al bloque 0x6D. En el ı́ndice 3 de esa lı́nea estará la palabra cuya dirección en memoria principal es 0x0DB63. Ejercicio 2 2 Una computadora utiliza una caché asociativa de 64 lı́neas de 32 palabras. La memoria principal cuenta con 216 palabras y es direccionable “a palabra”. a) ¿cuántas lı́neas posee la memoria principal? Solución de Mariano M. Moscato. (10 de noviembre de 2011) Cada lı́nea tiene 32 palabras de largo. Entonces la cantidad de lı́neas de la memoria será 216 = 211 25 b) Mostrar el formato de una dirección de memoria vista desde la caché (tag, index ). ¿Cuáles de estos campos deben guardarse en la caché? Solución de Mariano M. Moscato. (10 de noviembre de 2011) La lı́nea tiene 32 palabras; luego, alcanzan con cinco bits para el ı́ndice. En el punto anterior vimos que hay 211 lı́neas en memoria principal; entonces, bastan con once bits para el tag. tag 11 bits 2 Ejercicio index 5 bits 3 del capı́tulo 6, L. Null & J. Lobur, Essentials of Computer Organization and Architecture 2 c) ¿En qué lugar de la caché se guarda la palabra que se encuentra en la dirección de memoria 0xF8C9? Mostrar cómo queda la caché al leer dicha dirección. Solución de Mariano M. Moscato. (10 de noviembre de 2011) Como antes, comencemos por analizar la dirección 0xF8C9; en binario se escribe como 1111 1000 1100 1001. Utilizando el punto anterior sabemos que para esta dirección el tag es 0x7C6 y que el index es 9. Entonces, luego de procesar el pedido de la palabra cuya dirección es 0xF8C9, la primer lı́nea libre (o marcada como no válida) de la caché corresponderı́a a la lı́nea de memoria principal 0x7C6; donde la palabra pedida ocupa el lugar indicado por el ı́ndice 9. La siguiente figura muestra un ejemplo en el cual se asume que la caché estaba vacı́a antes de procesar el pedido. Ejercicio 3 3 Se tiene una computadora con 227 palabras de memoria principal. La caché tiene una capacidad total de 215 lı́neas de 64 palabras cada una. a) Mostrar el formato de una dirección de memoria para una caché asociativa por conjuntos de 2 vias. Solución de Mariano M. Moscato. (10 de noviembre de 2011) La memoria tiene 227 27 palabras. Como cada lı́nea tiene 64 palabras, la memoria tiene 226 = 221 lı́neas. La caché tiene 21 2 vias de 214 lı́neas cada una, entonces la memoria principal se encuentra dividida en 2214 = 27 bloques. tag 7 bits line 14 bits index 6 bits b) ¿Cómo queda cargada la caché al leer primero la posición de memoria 0x01178FC y luego 0x03178FC? 3 Ejercicio 5 del capı́tulo 6, L. Null & J. Lobur, Essentials of Computer Organization and Architecture 3 Solución de Mariano M. Moscato. (10 de noviembre de 2011) La primer dirección de memoria (000 0001 0001 0111 1000 1111 1100 en binario) será interpretada por la caché como 0x01 (tag), 0x05E3 (conjunto), 0x3C (ı́ndice). Si en ese conjunto las dos vı́as estuvieran libres, la memoria caché podrı́a quedar como se muestra en la siguiente figura. (Recordar que se carga toda la lı́nea.) La segunda dirección de memoria (000 0011 0001 0111 1000 1111 1100 en binario) será interpretada por la caché como 0x03 (tag), 0x05E3 (conjunto), 0x3C (ı́ndice). Siguendo con el ejemplo de la figura anterior, la caché cambiarı́a como se muestra a continuación. (Recordar que se carga toda la lı́nea.) 4 Ejercicio 4 Una computadora trabaja con palabras e instrucciones (de tamaño fijo) de 64 bits, direcciones y registros de 32 bits y direccionamiento a palabra. Sea el programa mostrado a la derecha, que calcula el producto escalar de dos vectores (el tamaño de los vectores se indica en R4). ciclo: Sabiendo que la etiqueta ciclo se encuentra cargada en la posición de memoria 0x0000 00F0, que las etiquetas de los vectores (v1 y v2) se encuentran en la posición 0xF000 00F0 y 0xFFFF 00F0, y suponiendo que dicha computadora cuenta con una memoria caché de 16 KB para almacenar datos, analizar la tasa de aciertos para una caché de correspondencia directa con lı́neas de 8 palabras. MOV R0,0 MOV R1,v1 MOV R2,v2 MOV R3,0 ADD R3,[R1] MUL R3,[R2] ADD R0,R3 MOV R3,0 INC R1 INC R2 DEC R4 JNZ ciclo Solución de Mariano M. Moscato. (10 de noviembre de 2011) Primero veamos cómo son los campos de acuerdo al tipo de caché con el que estamos trabajando. Como es una caché de correspondencia directa, cada dirección de memoria será interpretada utilizando los campos: tag, lı́nea e ı́ndice. Como hay 23 palabras en cada lı́nea y el procesador usa una dirección por palabra, alcanzarán 3 bits para el ı́ndice. Dado que la caché mide 16 KB, y cada palabra 8 bytes (64 bits), caben en ella 211 palabras. Como cada lı́nea agrupa 23 palabras, en la caché caben 28 lı́neas. Luego, alcanzan con 8 bits para el campo lı́nea. Entonces, como sabemos que las direcciones miden 32 bits, el campo tag deberá medir 32 − 8 − 3 = 21 bits. Veamos ahora los pedidos a memoria que vamos a tener a medida que ejecutemos el programa. Comencemos por las instrucciones anteriores al ciclo. pedido 1 2 3 4 0000 00EC 0000 00ED 0000 00EE 0000 00EF instrucción instrucción instrucción instrucción MOV MOV MOV MOV R0,0 R1,v1 R2,v2 R3,0 vista caché 000000 1D 4 000000 1D 5 000000 1D 6 000000 1D 7 resultado M H H H Hasta aquı́ tenemos cuatro pedidos, de los cuales el primero es un miss, pero provoca que se cargue la lı́nea correspondiente a los siguientes tres, que resultarán en sendos hits. La primera iteración del ciclo provoca los siguientes pedidos. pedido 5 6 7 8 9 10 11 12 13 14 0000 00F0 F000 00F0 0000 00F1 FFFF 00F0 0000 00F2 0000 00F3 0000 00F4 0000 00F5 0000 00F6 0000 00F7 instrucción dato instrucción dato instrucción instrucción instrucción instrucción instrucción instrucción ADD R3,[R1] MUL R3,[R2] ADD R0,R3 MOV R3,0 INC R1 INC R2 DEC R4 JNZ ciclo vista caché 000000 1E 0 1E0000 1E 0 000000 1E 1 1FFFE0 1E 0 000000 1E 2 000000 1E 3 000000 1E 4 000000 1E 5 000000 1E 6 000000 1E 7 resultado M M M M M H H H H H Si bien las ocho instrucciones del ciclo ocupan exactamente la lı́nea de tag cero y número de lı́nea 1E, el pedido de datos de las dos primeras instrucciones provocan que se desaloje (y se vuelva a alojar) dicha lı́nea en dos oportunidades sucesivas. Por lo tanto, tenemos diez pedidos más, los que se reparten equitativamente entre hits y misses. La segunda iteración provocará estos pedidos: 5 pedido 15 16 17 18 19 20 21 22 23 24 0000 00F0 F000 00F1 0000 00F1 FFFF 00F1 0000 00F2 0000 00F3 0000 00F4 0000 00F5 0000 00F6 0000 00F7 instrucción dato instrucción dato instrucción instrucción instrucción instrucción instrucción instrucción ADD R3,[R1] MUL R3,[R2] ADD R0,R3 MOV R3,0 INC R1 INC R2 DEC R4 JNZ ciclo vista caché 000000 1E 0 1E0000 1E 1 000000 1E 1 1FFFE0 1E 1 000000 1E 2 000000 1E 3 000000 1E 4 000000 1E 5 000000 1E 6 000000 1E 7 resultado H M M M M H H H H H Esta configuración es casi idéntica a la anterior, la única diferencia es que el primer pedido no provoca un miss como antes debido a que la lı́nea ya se encontraba en la caché (por el último pedido de la iteración anterior). Sin embargo, vuelve a repetirse el desalojo sucesivo de la lı́nea 1E. Es fácil ver que esto ocurre porque los pedidos de datos corresponden a lı́neas con el mismo número de lı́nea (1E) que las direcciones de las instrucciones. Dado que los datos pedidos se ubican en el primer ı́ndice de la lı́nea y se van pidiendo secuencialmente, esta misma configuración se repetirá en las siguientes seis iteraciones del ciclo. La novena iteración provocará los siguientes pedidos. pedido 95 96 97 98 99 100 101 102 103 104 0000 00F0 F000 00F8 0000 00F1 FFFF 00F8 0000 00F2 0000 00F3 0000 00F4 0000 00F5 0000 00F6 0000 00F7 instrucción dato instrucción dato instrucción instrucción instrucción instrucción instrucción instrucción ADD R3,[R1] MUL R3,[R2] ADD R0,R3 MOV R3,0 INC R1 INC R2 DEC R4 JNZ ciclo vista caché 000000 1E 0 1E0000 1F 0 000000 1E 1 1FFFE0 1F 0 000000 1E 2 000000 1E 3 000000 1E 4 000000 1E 5 000000 1E 6 000000 1E 7 resultado H M H M H H H H H H A partir de esta iteración ya no tenemos el desalojo de la lı́nea 1E, mencionado más arriba, y logramos aumentar la cantidad de hits a ocho de los diez pedidos que el ciclo realiza. Entonces: Si R4 = 1, la tasa de aciertos es de 8 14 ; Si 1 < R4 ≤ 8, la tasa de aciertos es de 3+5+6(R4−1) 4+10(R4) ; Si 8 < R4 ≤ 2032, la tasa de aciertos es de 3+5+6·7+8(R4−8) ; 4+10(R4) Preguntas finales: a) ¿Qué pasa si R4 es mayor a 2032? b) ¿Cómo cambiarı́a el resultado del ejercicio si se utilizara una caché asociativa por conjuntos de 2 vı́as con lı́neas de 8 palabras y algoritmo de reemplazo LRU? 6