deco_demux_Mux_demux.. - Escuela de Ingeniería Electrónica

Anuncio

1 of 36

Instituto Tecnológico de Costa Rica

Escuela de Ingeniería Electrónica

EL 3307 Diseño Lógico

Ejercicios

Tema: Codificadores, Decodificadores, Multiplexores,

Demultiplexores

Recopilación realizada por:

Ing. José Alberto Díaz García

Diciembre 2008

PROBLEMAS. 397

2 of 36

12. Parael comparadorde 4 bits de la Figura 6.80, dibujar cada forma de onda de salida para las

entradasque se muestran.Las salidas son activas a nivel ALTO.

.oto

-r:-'L-~-J-~

A1

I

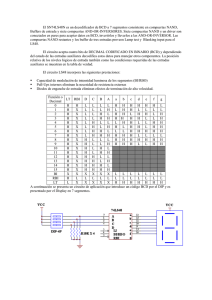

I

I

I

-+-f-1-1--4-+

1

I

A2:

-t-f

¡

I

I

.J

AJ

I

Bo~!

U

B2

I

:

I

I

;

1

i

i

I

i

i

I

i

~

I

I

I

I

1

1

I

I

!

L-L

i

1

..-+!

t--1 J-f I-i

BI 1

1

I

:

I

!!U1

I

1

I

11

1

I

-f:---1-+--~-~

! '-4 L

BJ-1--J

!!_.I.~ L

FIGURA

6.80

13.Paralos

grupos de númerosbinarios, detenninar los estadosde salida para el com-

paradorde la Figura6.22.

(.)A~~lAO

= 1100; B)B~IBO = 1001

(b)A~~,Ao= IOOO;B~~lBo= 1011

(c) A~~IAo = 0100;B)B~,BO= 0100

SECCIÓN6.S

Decodificadores

14. Cuando en la salida de cada puerta de decodificación de la Figura 6.81 hay un nivel ALTO,

¿cuáles el código binario que apareceen sus entradas?El bit más significativo (MSB) esAJ.

(a)

At

A 1

-.co

rLr-

'--

Az

A,

(e)

FIGURA

6.81

(d)

lS. ¿Cuáles la lógica de decodificación para cadauno de los siguientescódigos, si se requiereuna

salida activa a nivel ALTO (I)?

(a) 1101

(b) 1000

(c) 11011

(d) 11100

(e) 101010

(1) 111110

(1) 000101

(b) 1110110

16. Resolver el Problema 13, suponiendoque se requiere una salida activa a nivel BAJO (O).

398

.

FUNCIONES

DELA LÓGICA

COMBINACIONAL

3 of 36

17. Se deseadetectarúnicamentela presenciade los códigos 101O, 1100,0001 y 1011. Paraindi.

car la presenciade dichos códigos se requiere una salida activa a nivel ALTO. Desarrollar la

lógica de decodificación mínima necesariaque tenga una única salida que indique cuándo

cualquierade estoscódigos se encuentraen las entradas.Paracualquier otro código, la salida

ha de ser un nivel BAJO.

18. Si se aplican las fonnas de onda de entradaa la lógica de decodificación de la Figura 6.82,

dibujar las fonnas de onda de salida en función de dichas entradas.

Ao-rl.

I

I

Al!

I

I

. Ir1-I

!

I

I

I

i

.

.

t

1'

I

r

I

j

A2 -J

t-t!

Ao

!

!

!

A.

r

A2

FIGURA

6.82

19. Se aplican secuencialmentenúmerosBCD al decodificador BCD-decimal de la Figura 6.83.

Dibujar un diagramade tiempos que muestrecada salida en relación con el resto de las señales de salida y con las de entrada.

BCD/DEC

o

Ao

Al

.,rl."

~--~~-:--1--'¡'1

r:-~-~I

I

I

I

I

~

A2 ..LJ

I

r-1

A3 -J

I

I

I

I

I

I

~

L-J ,

I

I

!

I

I

!

I

I

I

I

LJ

I

r-1

I

I

1 '-

-rL

I

I

I

I

I

I

,

L--J 1--01L-L !

..

I

I

1.1

I

III

I

I

I

!

I

4.- '"o

Al

-'2

1

2

4

1

)

4-

A]

8

'

6

7""8 "'"-

-

9

74HC42

FIGURA

6.83

20. Un decodificador/excitadorde 7-segmentoscontrola el display de la Figura 6.84. Si se aplican

las fonDasde onda de entradaque se muestran,determinar la secuenciade dígitos que aparece en el display.

~

I

~

A. --+--t

A2

AJ

Ji

_Rrl

t

I

11! f

-L-J--1-J

BCD/7

I

1':

I

1:

::jll t--1

':

I

I

I

!

I!

l'

I

¡l~-J.

-'

I

I

:

!!

.

I

I~ :!

t--f

I L-

~

Ao

h

Al

A2

~

C

d

.

f

..

FIGURA

6.84

"

,~

~

,

PROBLEMAS.4 of399

36

SECCiÓN 6.6

21. Suponerque el codificador lógico decimal-BCD de la Figura 6.38 tiene las entradas3 y 9 a

nivel ALTO. ¿Cuál es el código de salida?¿Esésteun código BCD (8421) válido?

22. Un decodificador74HCI47 tiene niveles BAJOS de tensión en suspiDes2, 5 Y 12.¿Quécódigo BCD apareceen las salidassi tOdaslas demásentradaSestána nivel ALTO?

SECCiÓN 6.7

Convertidores de código

23. Convertir a BCD los siguientesnúmerosdecimalesy luego a binario.

(a) 2

(b) 8

(d) 26

(e) 33

(c) )3

24. Explicar )a lógica requeridapara convertir a código Gray un número binario de ) Obits, y utilizar esta lógica para convertir los siguientesnúmerosbinarios:

(a) 10)010)0)0

(b) 1111100000

(c) 0000001110

(d) 111111111)

25. Explicar la lógica requerida para convertir a binario un código Gray de 10 bits Y utilizar esta

lógica para convertir a binario los siguientescódigos Gray:

SECCIÓN 6.8

(a) 1010000000

(b) 0011001100

(c) 1111000111

(d) 00000oo001

Multiplexores (.electores de datos)

26. En el demultiplexor de la Figura 6.85, determinarla salida para los siguientesestadosde entrada: Do = O, DI= 1, D2= 1, D3= O, So = 1, SI = O

MUX

~

l}O'

Do

DI

y

D2

D3

FIGURA

6.85

27. Si las entradasde selecciónde datosdel multiplexor de la Figura 6.85 se secuenciantal y como

se muestraen las formas de onda de la Figura 6.86, detenninar la forma de onda de salidapara

los datosde entradadel Problema26.

So

---~

:'I

I

I

I

~

SI

--J

I

L-J

I

1,

:L-_J---l~-J---l

I

I

I

I

I

I

I

I

I

~t---1

I

LJ

L~

I

!

I

I

J

I

I

I

,

L-

FIGURA

6.86

28. Las formas de onda mosttadasen la Figura 6.87 se aplican a las entradasde un multiplexor de

ocho enttadas74LS 151. Dibujar la senalde salida Y.

SECCIÓN 6.9

Demultiplexores

29. Desarrollar el diagramade tiempos completo (entradasy salidas)de un 74HCl54 utilizado en

una aplicación de demultiplexación en el que las entradasson las siguientes:las entradasde

selecciónde datostoman, de forma repetitiva y secuencialmente,los valores generadospor un

400

.

5 of 36

FUNCIONES

DELA LÓGICA

COMBINACIONAL

contadorbinario que comienzaen 0000, y la enb"adade datos es una cadenade datos serie,en

BCD, que representanal número decimal 2468. El dígito menossignificativo (8) es el primero de la secuencia,con el bit menossignificativo en primer lugar, y deberáapareceren los cuatro primeros bits de la salida.

So

SI

Entradasde

selección

::

;;

I

----l-LJ ~

S~

"

~-,

I

:

¡

:I¡; ir::

I

I

I

I

I

I

I

I

I

t

-1

I

L

¡

t-.t~-:1'!:1

!¡¡

I

I

I

I

I

I

f

I

I

1

¡

:

¡

¡!

1

I

I

1

i

Do

DI

I

I

I

I

I

1

IIII

I

I

I

I

I

1

I

1

I

I

I

I

1

I

I

I

I

I

I

I

I

1

¡!!

1:

J!

D)

D

4

1

::

I

~ "i

¡ i

I

~;

I

1

I

I

111

¡¡

llJ---t---t-'

:i.

¡

!.

1

I

I

--t~~rl

~¡!¡¡I

D.1

I

1

I

I

: 'T

°6

II II

J I

-

¡ ¡

I

1

1

1

I

1

1

1

1

I

I

I

I

1

I

1

1

I

IH r-

1-1--1-11

I 1 1

I

I

I

i

f

1!

--++---~..-r1-1~

I

¡-~--4-~---1

D2

::

1'1

H 1:--1

¡ H Ir ¡ 11;

H:

~

Entradas

de datos

::

rTr ,1

¡ I

I

I

1

I

I

I

I

I

I

I

I

I

1

1

1

I

I

I

1

I

I

I

t "r:'t1

¡ ; i

i

r

i ;

¡I

I

I

1

I

I

¡I11

1

I

I

1

I

I

I

I

I

I

I

I

I

I

I

I

I

11

1

I

1

I

I

!!

1 ~

1

1

:!

r-11L-J-1

l' L-1

I I

I1 1

1

I

1 J1

I

i

FIGURA

6.87

SECCIÓN 6.10

Duración

debit

~

Ao

+-J I::

S-T--l---l-J

.J-l.-1--T-1-J-'

A)

A2

I

I

I

I

I

I

r-i!!

A3

,

~

l'

I

I

I

I

I

I

¡III

I

¡

:!

I

I

I

I

I

I

I

I

I

I

I

I

I

::.

II

I

U1 I

j!

~

FIGURA

6.88

31. Determinar las salidas EImpar y EPar de un generador/comprobadorde paridad 74LS280 de

9 bits, para las entradasde la Figura 6.89. Utilice la tabla de verdad de la Figura 6.59.

SECCIÓN 6.11

Localización de ayerias

32. El sumadorcompleto de la Figura 6.90 se pruebabajo todas las condiciones de entradaposibles, con las señalesde entradaindicadas.A partir de la observaciónde las señalesE y Caut'

¿funcionacorrectamente?Si la respuestaes no, ¿cuáles la causamás probable de fallo?

33. Enumerarlos posibles fallos de cada codificador/display de la Figura 6.91.

34. Desarrollar un procedimientode pruebassistemáticopara verificar el funcionamiento completo del codificador de teclado de la Figura 6.42.

PROBLEMAS. 401

PAR

I

IMPAR

Ao

A

I

í

I

i

I

!:: !

:! It :! :! !:

--l__t

1-.o-J-l_J---1_-..-:-1 1_[-1--1___1.._1

I

I

1

I

-

A..

1

í

I

-:!

I

I

!

.

I

I

I

I

I

I

I

I

¡

!I1

I

I

A4

_

L_j-t-i_.l_s.-:--1

1

I

I

5

A

I¡

1t

I

I

lit

¡

1

I

I

I

¡t-_!!1

iI I

JJ.I!

A7

A

18

E

I

,

I

I

..

~~

- -~ r-l

,i

I

I

I

!

:

:

I

I

c- -

I

I

I

:

I

I

I

t

I

I

I

I

I

!

J

"t~j1

FIGURA

6.89

:

:i i:

~

t-1 i

I

I

:

1---4--r---T-.l'

I

I

I

I

I

--' t-1 J--.ft-1 '-"' ~

---:~!

I

I!!!

6

C..

I

__1...1___r1__Ji___J"-

A

B,

I

A3

!

6 of 36

;:' ¡r--1I

I

I

I

I

I

I

I

,

I

FIGURA

6.90

(a)

(c)

(b)

FIGURA

6.91

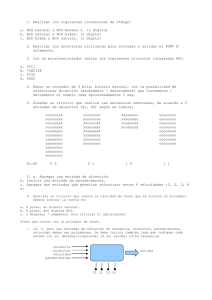

35. Hay que probar el convertidor BCD-binario fonDadopor cuatro sumadoresque se muestraen

la Figura 6.92. En primer lugar, hay que verificar que el circuito convierte de BCD a binario.

El procedimiento de prueba requiere la aplicación secuencialde númerosBCD, comenzando

por 0109

para comprobarque la salida binaria es la correcta.¿Quésíntomao síntomasaparecerían en las salidasbinarias si ocurrieran cadauno de los siguientesfallos? ¿Cuál es el número

BCD para el que se detectapor primera vez cada error?

(a) La entradaAl está en circuito abierto (sumador superior).

(b) Coutestá en circuito abierto (sumadorsuperior).

(c) La salida E4 está cortocircuitada a masa(sumador superior).

(d) La salida 32 está cortocircuitada a masa(sumador inferior).

402

.

FUNCIONES

DELA LÓGICA

COMBINACIONAL

Salida binaria de 7 bits

7 of 36

FIGURA

6.92

36. En el display con multiplexación de la Figura 6.52, detenninar la causa(o las causas)másprobable para cadauno de los siguientessíntomas:

(a) El display del dígito B (el más significativo) no se enciende.

(b) Ninguno de los displays de 7-segmentosse enciende.

(c) El segmentof de ambosdisplays apareceencendidosiempre.

(d) Hay un parpadeovisible en los displays.

37. Desarrollar un procedimiento sistemáticopara probar exhaustivamenteel CI selectorde datos

74LS151.

38. Durante las pruebasdel sistemade transmisión de datos de la Figura 6.60, se aplica un código a las entradasDo a D6 que contiene un número impar de ls. Se introduce deliberadamente

un único bit erróneo en la línea de transmisión serie entre el multiplexor y el demultiplexor,

pero el sistemano detectael error (salida de error = O). Tras algún tiempo de investigación,

se verifican las entradascon el comprobadorde paridad par y se encuentraque en Do a D6 hay

un número par de 1s, como se esperaba,y también se compruebaque el bit de paridad D7 es

l. ¿Cuálesson las posibles razonesde que el sistemano indique el error?

39. Describir de forma generalcómo probaríamosel sistemade transmisión de datos de la Figura

6.60 y especificarun método de introducción de erroresde paridad.

Aplicacióna los sistemasdigitales

40. El bloque de la lógica de salida del semáforo se implementa en el sistemausando lógica de

función fija mediante un 74LS08 con puertas AND operando como puertas negativa-NOR.

PROBLEMAS.

8 of 36 403

Utilizar un 74LSOO(puertasNAND cuádruples)y cualquier otro dispositivo que seanecesano para generarsalidasactivas a nivel BAJO para las entradas

41. Implementar la lógica de salida del semáforo con el 74LSOOsi se necesitansalidasactivas a

nivel BAJO.

Problemasespecialesde diseño

42. Modificar el diseño del sistema de multiplexación del display de 7-segmentosde la Figura

6.52 para permitir visualizar dos dígitos adicionales.

43. Utilizando la Tabla 6.2, escribir las expresionesde suma de productos para E y CouIde un

sumador completo. Utilizar un mapa de Karnaugh para minimizar las expresionesy luego

implementarlasempleandoinversoresy lógica AND-OR. Indicar cómo se puede reemplazar

la lógica AND-OR con selectoresde datos 74LS151.

44. Implementar la función lógica especificadaen la Tabla 6.12 utilizando un selector de datos

74LS151.

TABLA 6.12

45. Utilizando dos de los módulos sumadoresde 6 posicionesde la Figura 6.14, diseñarun sistema de votación de 12 posiciones.

46. El bloque sumadordel sistemade control y recuento de pastillas de la Figura 6.93 realiza la

sumadel número binario de 8 bits del contadory del número binario de 16 bits del registro B.

El resultadode la suma se almacenaen el registro B. Utilizar circuitos 74LS283 para implementar esta función y dibujar un diagrama lógico completo que incluya la numeraciónde los

piDes.Revise el funcionamiento del sistemaen el Capítulo l.

47. Utilizar circuitos 74HC85 para implementar el bloque comparador del sistema de control y

recuentode pastillas de la Figura 6.93 y dibujar un diagrama lógico completo que incluya la

numeraciónde pines. El comparadorcomparael número binario de 8 bits (en realidad sólo se

requierensietebits) del convertidor BCD-binario con el número binario de 8 bits del contador.

404.

9 of 36

DE LA LÓGICA

f.DCDCD

~ffi~

[[JDCD

C<xIific.

-..

4 hit,

Decimal.-+

aBCD

Te(:lado

8 biL~

RegiscroB

16-bita

'f~t~t~!

Coovenidor

decódigo

Bill8rio

DecOOifk..

B

BCDa

7-1e1

,,~:!~~'~.c

MUX

16bils

Entrada de ("Ontrol de la

secuencia de conmutación

FIGURA

6.93

48. Se utilizan dos decodificadoresBCD- 7-segmentosen el sistema de control y recuento de la

Figura 6.93. Uno de ellos se requierepara controlar el display de dos digitos pastillas/bote, y

el otro para controlar el display de 5 digitos número total de pastillas envasadas.Utilizar circuitos 74LS47 para implementar cada decodificador y dibujar un diagrama lógico completo

que incluya la numeraciónde pines.

49. El codificador que se muestraen el diagramade bloques de la Figura 6.93 codifica cadapulsación de una tecla decimal y la convierte en BCD. Utilizar un 74HC147 para implementar

esta función y dibujar un diagrama lógico completo que incluya la numeraciónde pines.

SO.El sistemade la Figura 6.93 requiere dos convertidoresde código. El convertidor BCD-binano convierte los dos númerosBCD de dos digitos del registro A en un código binario de 8 bits

(en realidad sólo se necesitan7 bits dado que el bit más significativo siempre es O).Utilizar

los convertidores de código circuito integrado apropiados para implementar la función del

convertidor BCD-binario, y dibujar un diagrama lógico completo que incluya la numeración

de pines.

REVIS

IONES

DECADASECCiÓN

SECCiÓN 6.1

l.

(a) 1: = 1, C. = O (b) E = O, C... = O

~

RESPUESTAS.405

10 of 36

(c) 1::= 1, C.. = O

(d) E = O,C. ~ 1

2. 1::= 1,C. = 1

SECCIÓN 6.2

Sumadores binaríos en paralelo

l. C_E4EJE2E¡= 11001

2.

Se requierentres 74LS283 para sumardos númerosde 10 bits.

SECCIÓN 6.3

1. CI = O,C, = 1

1. C. = 1

SECCIÓN 6.4

Comparadores

1. A > B = 1,A < B = O,A = B = OcuandoA = 1011y B = 101O

2. Comparador de la derecha: pin 7: A < B = 1; pin 6: A = B = O; pin 5: A > B = O

Comparador de la izquierda: pin 7: A < B = O;pin 6: A = B = O;pin 5: A > B = l

SECCIÓN 6.5

SECCIÓN 6.6

Oecodificadores

l. La salida 5 está activa cuandoen las entradasse aplica 101.

2.

Se utilizan cuatro 74HCI54 para decodificar un número binario de 6 bits.

3.

La salida activa a nivel BAJO controla el display de diodos LEO en cátodo común.

Codificadores

1. (a)Ao= 1,AI = 1,A2=0,A]=

1

(b) No, no es un código BCD válido.

(c) Sólo puedeestaractivadauna entradapara obtener una salida válida.

2. (a) ~ = O,~ = 1, Al = 1,Ao = 1

(b) La salida es 0111, que es el complementode lO()()(8).

SECCIÓN 6.7

Convertidores de código

1. 10000101(BCO)= 10101012

2. Un convertidor binario-código Gray de ocho bits estáformado por siete puertasOR-exclusiva

en una disposición como la de la Figura 6.43.

SECCIÓN 6.8

Multiplexores (selectoresde datos)

1. La salida es O.

2. (a) 74LS157: Selectorde datos cuádruplede 2 entradas.

(b) 74LS 151: Selectorde datos de 8 entradas.

3. La salida de datos alterna entre un nivel BAJO y un nivel ALTO a medida que las entradasde

selecciónde datos cambian, secuencialmente,entre los distintos estadosbinarios.

4. (a) El 74HCI57A multiplexa los dos códigos BCO al decodificador de 7-segmentos.

(b) El 74LS47 decodifica el código BCO para excitar el display.

(c) El 74LSI39 activa los displays de 7-segmentosalternativamente.

SECCIÓN 6.9

Demultiplexores

1. Se puede utilizar un decodificador como multiplexor, utilizando las lineas de entradacomo

entradasde selecciónde datos y una linea de activación como entradade datos.

2. Las salidasestántodas a nivel ALTO exceptoDIo, que es un nivel BAJO.

406

.

FUNCIONES

DELA LÓGICA

COMBINACIONAL

11 of 36

SECCiÓN 6.10

Comprobadores/generadores de paridad

1. (a) Paridadpar: 1110100

(b) Paridadpar: 00 11000 11

2. (a) Paridadimpar: 11010101

(b)11000001

3. (a) El código es correcto, cuatro ls.

(b) El código es erróneo,siete 1s.

SECCIÓN 6.11

Localización de aver'a.

1. Un g/itch es un pico de tensión de muy corta duración (generalmenteindeseado).

2. Los g/itches los originan los estadosde transición.

3. Validar (strobing) consiste en la activación de un dispositivo durante un período de tiempo

especificado,mientrasel dispositivo no se encuentraen un estadode b'ansición

PROBLEMASRELACIONADOS

6.2

E = 1, C. = 1

El = O,E2= O,E3 = 1, E. = 1

6.3

1011+ 1010 = 10101

6.4.

Véasela Figura 6.94.

6.1

FIGURA

6.94

6.5.

Véasela Figura 6.95.

Ao= 1=::)1:~:»o.~--i.-~

: : :::::DoJ-~

B, = 1

-

O=> distinto

O

FIGURA

6.95

6.6

A > B

= O,A = B = O,A < B = 1

6.7.

Véasela Figura 6.96.

6.8.

Véasela Figura 6.97.

6.9. Salida 22

RESPUESTAS.407

12 of 36

FIGURA

6.96

FIGURA

6.97

6.10. Véasela Figura 6.98.

o

2

3

4

6

!:: ! !:: ! !: !: !: If--i r-::

íí

í

.

.

í

i

i

~

7

,

,

.

.

~

~,.,

,

I

S

8

;

..

;

;.

L-J

. .

I

,

,

,

;

¡;

"'"

u

,

.

"

"

,

,

.: :. .: : :

~

.

.

,

I

,

,

,

,

~

~

~

.

I

"..

""

9

.'U

FIGURA 6.98

6.11. Todas las entradasa nivel BAJO:

Aa

= O. ~ = l. ~ = l. ~ = O

Todaslas entradasa nivel ALTO: todas las salidasa nivel ALTO.

6.12 BCD 01O(MNM)

1

I~~======~~~~~

:

Binario

6.13 SietepuertasOR-exclusiva.

~l

OOIOI<KK>

00101001

1

~

41

408

.

FUNCIONES

DELA LÓGICA

COMBINACIONAL

13 of 36

6.14. Véasela Figura 6.99.

So:

~~r~_-rn

syI ~L-r-'l~LrI

~.r--,~

..

. .

FIGURA

6.99

6.15. Do:

D4:

= O,S2= O,SI =

S) = O, ~ = 1, SI =

O,So= O

S)

O, So = O

DI: S) = 1, S2= O,S, = O,So= O

DI): S) = 1, S2= 1, S, = O,So= 1

6.16. Véasela Figura 6.100.

6.17. Véasela Figura 6.101.

6.18. Véasela Figura 6.102.

EN

MUX

O

.4

.4

}

09

1

2

---

O

1

2

,)

4

+SV

--

- -

y,A.,A.Ao+.4~.Ao+.4~.Ao

,

6

7

-

74LS1S1

FIGURA6.100

A)AZAiAo+ A)A~,Áo

+ A)ÁzAiAo + A)Á~IAo

+ Á)AZAtÁO+ Á,A~,Ao

+ Á)ÁzAiAo + Á)Á~tÁo

FIGURA

6.101

SO

S,

~J-1---r1-T~

I I

DI

O

.

DI!

~Lr1

D3:-1

.

I

.

.

I

L

!

!

!

:

I

I

I

I

I

I

r-'1

!

~ !

.

I

!

!

.

I

I

')

I

I

I

I

I

r--,

I

.

.

I

I

!

!

!

!

!

!

!

!

:r-~

FIGURA6.102

CAPíTULO 6

372

.

BLOQuES CONSTRUCTORESDE CIRCUITOS COM8INAClONALES

LIBRARY ieee ;

USE ieee.stdJogic_1164.a11

;

E~'TITY shifter IS

PORT(w

Shift

y

k

END shifter ;

Sm.LOGIC_V ECI'OR(3 OOWNTO O) ;

:IN

:IN

Sm.LOGIC;

: OUT Sm.LOGIC- VECTOR(3 DOWNTO O);

: OUT Sm.LOGIC ) ;

ARCHITEcrURE BehaviorOF shifter IS

BEGIN

PROCESS(Shift, w)

BEGIN

IF Shift = '1' THEN

y(3) < = 'O' ;

y(2 OOWNTO O)< = w(3 OOWNTO 1) ;

k<= w(O);

ELSE

y<=w;

k<= '0' ;

END IF ;

END PROCESS;

END Behavior ;

Figura 6.59

C6digo estructural de VHDl que especifica el circuito de

corrimientode la figura 6.56.

PROBLEMAS

14 of 36

Al final del libro seproporcionanlas respuestasde los problemasmarcadoscon asterisco.

6.1

Muestrecómo implementarla función f(w), W2,W3)= ¿m(O, 2, 3,4,5,7) con un decodificador binario tres a ocho y una compuertaORo

6.2

Muestrecómo implementarla función f(Wl, W2,W3) = ¿m(l,

2, 3,5,6) con un decodifica-

dor binario tres a ocho y una compuertaORo

-6.3

6.4

-6.5

Considerela función f = W¡W3+ W2W3

+ WlW2.Use la tabla de verdada fin de derivarun circuito paraf que useun multiplexor dos a uno.

Repitael problema6.3parala funciónf

Para la función f(Wl'

W2, W3)

= ¿m(O,

= W2W3+ W1W2.

2, 3, 6), use la expansión de Shannon para derivar

una implementación

que utilice un multiplexordos a uno y cualesquieraotrascompuertas

necesanas.

6.6

Repitael problema6.5 para la función f (Wl, W2,W3)= ¿ m(O,4, 6, 7).

373

15 of 36

LffiRARY ieee ;

USE ieee.stdJogic_II64.all;

USE ieee.numeric-5td.all;

-;:

ENTITYshifterIS

:IN

UNSIGNED(3 OOWNTO O) ;

PORT(w

Shift :IN

STD.LOGIC ;

: OUT UNSIGNED(3 OOWNTO O) ;

y

k

: OUT STD.LOGIC) ;

END shifter;

ARCHITECTURE BehaviorOF shifterIS

BEGIN

PROCESS

(Shift,w)

BEGIN

IF Shift="1" THEN

y <=wSRL 1;

k <= w(O);

ELSE

y<=w;

k <= "O" ;

END IF ;

ENDPROCESS

;

ENDBehavior;

Figura 6.60

6.7

Código por comportamiento de VHDl que especifica

el circuitode corrimientode la figuro 6.56.

Considerela función !

= W2+WtW3+WtW3. Muestre cómo se puede usar la

aplicación repetida de la expansión de Shannon para derivar los mintérminos

de!

= W2 + WtW3.

6.8

Repitael problema6.7para!

6.9

Demuestre el teorema de expansión de Shannon expuesto en la sección 6.1.2.

*6.10

6.11

En la sección 6.1.2 se muestra la expansión de Shannon en forma de suma de

productos. Con el principio de dualidad, derive la expresión equivalente en

forma de producto de sumas.

Considerela función ! = Wt W2+ W2W3+ WtW2W3.Proporcione un circuito

que implemente f con el mínimo número de LUT de dos entradas. Muestre la

tabla de verdad implementada dentro de cada LUT.

*6.12

6.13

Para la función del problema 6.11, el costo de la expresión en mínima suma de

productos es 14, que incluye cuatro compuertas y 10 entradas a las compuertas. Utilice la expansión de Shannon para derivar un circuito multinivel que

tenga un costo menor y proporcione el costo de su circuito.

Considere la función !(Wt,

W2, W3, W4)

= ¿m(O,

1,3,6,8,9,14,15).

Deri-

ve una implementación

que useel mínimonúmeroposiblede LUT de tres

entradas.

374

CAPíTULO 6

.

BLOQUES CONSTRUcrO~

DE CIRCUITOS COMBINAClONALES

16 of 36

LffiRARY ieee;

USE ieee.std.Jogic_ll64.all;

USE ieee.numeric_std.all

;

ENTITYbarre}IS

PORT(w : IN UNSIGNED(3 DOWNTO O) ;

UNSIGNED( 1 DOWNTO O) ) ;

s :IN

- -,

y: OUT UNSIGNED(3 OOWNTO O) ) ;

END barre} ;

ARCHITEcruRE BehaviorOF barrel IS

BEGIN

PROCESS(s, w)

BEGIN

CASE s IS

WHEN "00" = >

y<=w;

WHEN"01" =>

y < = w ROR 1 ;

WHEN "10" =>

y<= wROR2;

WHEN arHERS = >

y<= wROR3;

ENDCASE;

END PROCESS;

END Behavior;

Figura 6.61

.6.14

Código de VHDl que especificael circuitode corrimiento

en cilindro de la figura 6.57.

Dé dos ejemplos de funciones lógicas con cinco entradas, Wl' . . . , ws'quese

pueda realizar con dos LUT de cuatro entradas.

6.1S

Parala función! del ejemplo 6.27, realice expansión de Shannonrespectode las

variables Wl y W2'en lugar de Wl y W4'¿Cómo se compara el circuito resultante con el de la figura 6.52?

6.16

Actel Corporation fabrica una familia de FPGA llamada Act 1, que tiene el

bloque lógico basado en multiplexor que se muestra en la figura P6.1. Indique

cómo implementarla función f

W2W3+ WIW3+ W2W3sólo con un bloque

=

lógico Act l.

6.17

Muestre cómo se realiza la función f

= WIW3+WIW3+W2W3+WIW2

con

bloques lógicos Act 1. Note que no hay compuertas NOT en el chip; por tanto,

los complementos de las señalesdeben generarsecon multiplexores en el blo.

que lógico.

PROBLEMAS

17 of 36

i.

;2

i3

'4

i.5

;6

Figura P6.1

-6.18

Bloquelógico Act 1 de Actel.

Considereel código de VHDL de la figura P6.2. ¿Quétipo de circuito representa?Comentesi el estilo de código usado es una buena elección para el

circuito que representa.

6.19

Escribael códigodeVHDL querepresente

la funcióndel problema6.1,empleandouna asignaciónde señalseleccionada.

~:,

ii.

~~

~

,"

~'O

*;;

'{~

~~"

~'

6.20

Escribael códigodeVHDL querepresentela función del problema6.2,usando

una asignaciónde señalseleccionada.

6.21

Con unaasignaciónde señalseleccionada,escribael código deVHDL paraun

codificadorbinario cuatroa dos.

6.22

Con una asignaciónde señalcondicional,escribael código deVHDL paraun

codificadorbinario ocho a tres.

6.23

Derive el circuito paraun codificadorde prioridad ocho a tres.

6.24

Con una asignaciónde señalcondicional,escribael código de VHDL paraun

codificadorde prioridad ocho a tres.

6.25

Repitael problema6.24 ahoracon una instrucciónif-then-else.

6.26

CreeunaentidaddeVHDL llamadaif2to4 que representeun decodificadorbinario que useuna instrucciónif-then-else.Creeuna segundaentidadllamada

h3to8querepresenteel decodificadorbinario tres a ocho de la figura 6.17,con

dos instanciasde la entidadif2to4.

6.27

Cree una entidadde VHDL llamadah6to64 que representeun decodificador

binario 6 a 64. Use la estructuraarborescentede la figura 6.18 en la que el

decodificador6 a 64 seconstruyacon cinco instanciasdel decodificadorh3to8

creadoen el problema6.26.

6.28

Escribael código de VHDL para un convertidorde código BCD a siete segmentosusandouna asignaciónde señalseleccionada.

.6.29

Derive expresionesen mínima sumade productospara las salidasa, b y c de

la pantallade sietesegmentosde la figura 6.25.

"

375

376

CAPíTULO 6

.

BLOQUES CONSTRUCTORESDE CIRCU1T~ COMBINAClONALI:S

18 of 36

LffiRARY ieee;

USE ieee.stdJogic_II64.a11

;

ENTITY problem15

PORT(w

:IN

Sm-LOGIC-VECfOR(1DOWNTO O) ;

:IN

En

Sm-LOGIC;

END proble:' y l. y2, y3 : OUT Sm-LOGIC ) ;

.

ARCHITECfURE BehaviorOF problemIS

BEGIN

PROCESS(w, En)

BEGIN

yO <= 'O' ; yl <= 'O' ; y2 <= '0' ; y3 <= '0' ;

IF En '1' THEN

IF w = "00" THEN yO<= ' l' ;

ELSIF w = "01" THEN yl <= '1' ;

ELSIF w = "10" 1HEN y2 <= '1' ;

ELSEy3 <= '1' ;

ENDIF;

ENDIF;

ENDPROCESS

;

END Behavior;

Figura P6.2

Códigopora el problema6.18.

6.30

Derive expresiones en mínima suma de productos para las salidas d. e.f y g de

la pantalla de siete segmentos de la figura 6.25.

6.31

Diseñe un circuito de corrimiento, similar al de la figura 6.56, que pueda correr un vector entrada de cuatro bits, W = W3W2W¡WO.

una posición de bit a la

derecha cuando la señal de control Right sea igual al, y una posición de bit

a la izquierda cuando la señal de control Left sea igual a l. Cuando Right =

Left = O, la salida del circuito debe ser la misma que el vector entrada. Suponga que la condición Right = Left = 1 nunca ocurrirá.

6.32

En la figura 6.21 se muestra un diagrama de bloques de una ROM. Un circuito

que implementa una 'pequeña ROM, con cuatro hileras y cuatro columnas, se

muestra en la figura P6.3. Cada X en la figura representa un interruptor que

determina si la ROM produce un 1 o un O cuando dicha ubicación se lee.

Q) Muestre cómo realizar un interruptor (X) empleandoun solo transistor NMOS.

b) Dibuje completo el circuito ROM de 4 x 4 utilizando los interruptores

creados en el inciso anterior. La ROM debe programarse para almacenar los

bits O1O1 en la fila O (la superior), 10l O en la 1, 1100 en la 2 y 00 11 en la 3 (la

fila inferior).

c) Muestre cómo implementar cada interruptor (X) como un interruptor programable (en oposición a ofrecer I o O de manera permanente), con una celda

EEPROM, como se muestra en la figura 3.64. Describa brevemente cómo se

oon..1.. n.I~.. ~. ..1n-.",..n..n-.iAftf'"

377

;Cf:.fj#,;

vD.,

,n;~

19 of 36

1"r,ñ.$1.

al

Figura P6.3

6.33

CircuitoROMde 4 x 4.

Muestreel circuitocompletoparaunaROMqueuselasceldasde almacenamientodiseñadas

en el incisoa) del problema6.32querealicelas funciones

lógicas

d3= aoeal

d 2 = 'D:o""$QI

dI = aoal

do= ao+al

E. Shannon,"Symbolic AnalysisofRelay and SwitchingCircuits", TransactionsAIEE 57

~38),pp. 713-723.

tel Corporation,"MX FPGA Data Sheet",http://www.actel.com

ickLogic Corporation,"pASIC 3 FPGA Data Sheet",http://www.quicklogic.com

I.roblenl.ts

573

describir la operación de estos circuitos, pero los compiladores modernos como CUPL también ofrecen el formato de anotación de la tabla de verdad.

::':

"~

-

B

B

B

ánodo

bus de.común

datos

decodificador-excitador

BCD a 7 segmentos de

multiplexaje(MUX)

multiplexor

bus flotante

cátodo común

codificador

codificador de prioridad

conversión de paralelo a

serial

decodificador

decodificador de BCD a

decimal

demultiplexor (DEMUX)

dividir y vencer

excitador

excitador de bus

LCD

líneas bidireccionales de

datos

matriz activa

matriz pasiva

observación-análisis

palabra

píxel

plano posterior

TFT

20 of 36

SECCiÓN 9-1

9-1. Consulte la figura 9-3. Determine los niveles en cada salida del decodificador

para los siguientes conjuntos de condiciones de entrada.

(a) Todas las entradas en BAJO.

(b) Todas las entradas en BAJO, excepto E3 = ALTO.

(c) Todas las entradas en ALTO, excepto El = El = BAJO.

(d) Todas las entradas en ALTO.

9-2. ¿Cuál es el número de entradas y salidas de un decodificador que acepta 64

combinaciones diferentes?

9-3. Para un 74ALS138, ¿qué condiciones de entrada producirán las siguientes salidas?:

(a) BAJO en ~

(c) BAJO en

(b) BAJO en ~

(d) BAJO en 'C>oy~,

de manera simultánea.

9-4. Muestre cómo usar circuitos 74LSl38 para fonnar un decodificador 1 de 16.

9-5. En la figura 9-56 se muestra cómo se puede usar un decodificador en la generación de señales de control. Suponga que ha ocurrido un pulso de RESTABLECIMIENTO en el tiempo lo, y determine las formas de onda de

CONTROL para 32 pulsos de reloj.

~

D

I

1.I.r+-J-l

J--~_J"

I

I

I

to

(a)

.11

(b)

t2

574

Capítulo 9 / Circuitos lógicos MSI

21 of 36

~.

D

Modifique el circuito de la figura 9-56 para generar una forma de onda

CONTROL que pase a BAJO de 120a 124'(Sugerencia: la modificación no

quiere lógica adicional.)

9-7. El decodificador 7442 de la figura 9-5 no tiene una entrada HABILITAR.

embarg<!.!lo ~emos

operar como decodificador 1 de 8 no empleando

salidas 08 y 09 Y usando la entrada D como una ENABLE. Esto se ilustra

la figura 9-57. Describa cómo funciona esta configuración como un

cador habilitado 1 de 8 y explique en qué forma el nivel en D habilita o

habilita las salidas.

FIGURA 9-57

Problema 9-7.

9-8. Considere las formas de onda de la figura 9-58. Aplique estas

74LSl38como sigue:

A-+Ao

B~A1

C-+

A2

D-+~

Suponga que E LY

para las salidas °0,

A

s

q

o

t~

FIGURA 9-58

D

t11

Problemas 9-8 y 9-41.

9-9. Modifique el circuito de la figura 9-6 de manera que el relevador K1 perm2nezca energizado de 13a ~, y K2 permanezca energizado de 1(>a ~. (Sugerencia: esta modificación no requiere circuitería adicional.)

~

Problt'1J)

~75

a~

22 of 36

SECCIONES9-2 y 9-3

B, D

B

c, D

8

.

9-10. Muestre cómo conectar decodificadores-excitadores de BCD a 7 segmentos y

visualizadores LED de 7 segmentos al circuito de reloj de la figura 7-47, para visualizar minutos y horas. Suponga que cada segmento operará en aproximadamente 10 mA a 2.5 V.

9-11. (a) Consulte la figura 9-10 y dibuje el segmento y las formas de onda del

plano posterior relativas a tierra para CONTROL = O. Luego dibuje la

forma de onda del voltaje del segmento relativa al voltaje del plano posterior.

(b) Repita el inciso (a) para CONTROL = 1.

9-12. El decodificador-excitador de BCD a 7 segmentos de la figura 9-8 contiene la

lógica para activar cada segmento en las entradas BCD apropiadas. Diseñe

la lógica para activar el segmento 8.

SECCiÓN 9-4

9-13. PREGUNTA DE REPASO

Para cada punto, indique si se refiere a un decodificador o a un codificador.

(a) Tiene más entradas que salidas.

(b) Se usa para convertir acciones clave a un código binario.

(c) Sólo se puede activar una salida a la vez.

(d) Se puede usar para conectar una entrada BCD a un vísualizador LED.

(e) A menudo tiene salidas tipo excitador para manejar 1 y V grandes.

9-14. Determine los niveles de salida para el codificador 74147cuando As = ~ =

OY el resto de las entradasson ALTAS.

9-15. Aplique las señalesde la figura 9-58 a las mtradas de un 74147como sigue:

A -+ A7

c,D

B -+ ~

C -+ A2

D -+ Al

Dibuje las formas de onda de las salidasdel codificador.

9-16. En la figura 9-59 se muestra el dia~ma de bloques de un circuito lógico

empleado para controlar el número de copias que hace una máquina copiadora. El operador de la máquina selecciona el número de copias deseado

cerrando uno de los interruptores de SELECT de 51 a

~. Este número

está

codificado en BCD por el codificador y se envía a un circuito comparador.

9-59 Problemas9-16

57.

.

s.

53

'='

..

~'.:

~-

5781

Cótpít.ulo 9 I Circuitos lógicos MSI

23 of 36

c, D

Luego el operador acciona un intemJptor de contacto momentáneo de INI..

CIO que borra el contador e inida una salida ALTA DE OPERACIÓN, la cual;,~

es enviada a la máquina para indicarle que haga copias. A medida que la má."

quina hace cada copia, se genera un pulso de copiado y se alimenta al COnta

dor BCD. Las salidas del contador se comparan continuamente con las salidaS;;"

codificadas del intemJptor mediante el comparador. Cuando los dos númerosI "~

BCD son iguales, lo que indica_que el número deseado de copias se ha he-Jt~

cho, la salida del comparador X pasa a BAJO, esto causa que el nivel OPE-1"i:

RAR retorne a BAJO y pare la máquina de modo que no haga más copias.:~";

Activando el intemJptor de INICIO causará que este proceso se repita. Diseñe!;:C

la circuitería lógica completa para las secciones del comparador y de control '1

de este sistema.

j j',

9-17. El circuito de teclado de la figura 9-16 está diseñado para aceptar un número "-:'"

decimal de tres dígitos. ¿Qué sucedería si se activaran cuatro teclas de dígi- :

tos (por ejemplo, 3095)?Diseñe la lógica necesaria que se debe agregar a este "

circuito de modo que después que se hayan ingresado tres dígitos, cualquier

dígito adidonal sea ignorado hasta que se presione la tecla BORRAR. En

otras palabras, si se ingresa 3095 mediante el teclado, los registros de salida

visual izarán 309 e ignorarán cualesquiera dígitos siguientes hasta que se borre el circuito.

l.,

T

SECCIÓN9-6

9-18. Un técnico conecta el circuito de entrada del teclado numérico de la figura

9-16 y prueba su operación tratando de ingresar una serie de números de

tres dígitos. Se da cuenta que algunas veces el dígito "O" se ingresa en vez

del dígito que presionó. Asimismo, observa que sucede con todas la~ teclas

más o menos de forma aleatoria, aunque es peor para algunas teclas que para otras. Reemplaza todos los CIs y el mal funcionamiento persiste. ¿Cuálde

las siguientes fallas del drcuito explicaría sus observaciones? Explique cada

una de sus elecciones.

(a) El técnico olvidó conectar a tierra las entradas no usadas de la compuerta ORo

(b) Por error usó

T

T

T

Q en

vez de Q del MV monoestable.

(c) El rebote del intemJptor de las teclas de dígitos dura más que 20 ns.

(d) Las salidas Yy Z están cortocircuitadas entre sÍ.

9-19. Repita el problema 9-18 con el siguiente síntoma: los registros y visualizadores permanecen en O sin importar cuántas veces se presione una tecla.

9-20. Mientras prueba el circuito de la figura 9-16, el técnico encuentra que cuando se presiona cada tecla con número non resulta en el dígito correcto ingresado, pero cuando se presiona cada tecla con número par resulta en el

ingreso del número equivocado como sigue: la tecla "O" ocasiona que se ingrese un "1", la tecla "2" causa que se ingrese el número "3", la tecla "4",

que se ingrese el número "5", etcétera. Considere cada una de las siguientes

fallas como causas posibles del mal funcionamiento, y en cada caso explique

por qué puede ser o no la causa real.

(a) Hay una conexión abierta en la salida del inversor del LSB a las entradas

D de los FF.

(b) La entrada D del flip-flop {:?s está cortocircuitada internamente a Vc'c"

(c) Un puente de soldadura está cortocircuitando 00 a tierra.

9-21. Un técnico prueba el circuito de la figura 9-4, como se describe en el ejemplo 9-7 Y obtiene los siguientes resultados: todas las salidas funcionan, excepto 016 a 019 y 024 a 027, que están en ALTO de manera permanente.

¿Cuáles la falla más probable del circuito?

577

Probl('ma~

24 of 36

T

9-22. Un técnico prueba el circuito de la figura 9-4, como se describe en el ejemplo 9-7, Y encuentra que se activa la salida incorrecta para cada código de

entrada posible, excepto los listados en la tabla 9-7. Examine esta tabla y determine la causa probable del mal funcionamiento.

TABLA 9-7

T

T

f

(a:

9-23. Suponga que por error se usó una resistencia de 22 n para el segmentog de

la figura 9-8. ¿De qué manera afecta esto al visualizador? ¿Qué problemas

podrían surgir?

9-24. Repita el problema 9-8 con la secuencia observada que se muestra a continuación.

T

9-25. Repitael ejemplo 9-8 con la secuenciaobservadaque se muestraa continuación.

T

9-26. Para probar el circuito de la figura 9-11, un técnico conecta un contador

BCD a las entradas del 74HC4511 y pulsa el contador a una velocidad muy

baja. Nota que el segmento f funciona de manera erdtica y no es evidente

ningún patrón en particular. ¿Cuáles son algunas causas posibles del mal

funcionamiento? (Sugerencia: recuerde que los CIs son CMOS.)

li

t

~

~

578

(:apítulo 9 / Circuitos lógicos MSI

25 of 36

SECCIONES

9-7 Y 9-8

B

FIGURA 9-60

:>-27.

Problema

9-27. El diagrama de sincronización de la figura 9-60 se aplica a la figura 9-19. ~

buje la forma de onda de salida Z.

11

lO

I l

r-l_r...L I l 1l_J-l

L_rL..j.L.J-l__J-LJ.L.Jl_r1_J-L..I-

S

9-28. En la figura 7-45 se muestra un circuito que selecciona frecuencias de reloj.

Muestre cómo reemplazar el interruptor rotario con un multiplexor 74HC151

e indique las condiciones de control de entrada necesarias para seleccionar

la frecuencia de reloj de 1 kHz.

9-29. El circuito de la figura 9-61 usa dos multiplexores de dos entradas (figura 9-19).

Determine la función que realiza este circuito.

FIGURA 9-61

)-29.

r

Problema

I

3

'2

I

I

I

I

I

.

I

I

I

I

I

I

1,

~~.1

~ ;- .

,c;'"

I

1

lO

D

c, D

II

Z

I

I

I

I

I

I

I

I

I

-

I

I

S

MUX

lO

11

I

I

I

I

I

I

"

Z

-

1,

I

I

lO

MUX

MUX

lO

S

S,r

S

j'

-.:

So

I

I

Z

I

I

I

I

I

I

9-30. Use la idea del problema 9-29 para configurar varios multiplexores 74151de

1 a 8 para formar un multiplexor de 1 de 64.

9-31. Muestre cómo se pueden configurar dos 74157 y un 74151 para formar un

multiplexor 1 de 16 sin que se requiera ninguna otra lógica. Etiquete las e~

tradas10 a /15para mostrarcómo correspondenal código de SELECT.

D

9-32. (a) Amplíe el circuito de la figura 9-24 para visual izar el contenido de dos

contadores BCD de tres etapas.

(b) Cuente el número de conexiones en este circuito y compare su número

con el que se requeriría si se usara un decodificador-excitador por sepa.

rado para cada etapa del contador.

9-33. En la figura 9-62 se muestra cómo se puede usar un multiplexor para gene.

rar formas de onda lógicas con cualquier patrón deseado. El patrón se pro-grama usando ocho interruptores SPDT, y la forma de onda se produce de

manera repetitiva pulsando el contador MOD-8. Dibuje la forma de onda en

Z para las posiciones del interruptor determinadas.

l.robl('lna~

26 of 36

1 579

Problemas

D

D

N

9-34. Cambie el contador M°o:-s de la figura 9-62 a un contador MOD-16, y conecte el MSBa la entrada E del multiplexor. Dibuje la forma de onda Z.

9-35. Muestre cómo se puede usar un 74151 para generar la función lógica Z =

AB+ BC+ A.C

9-36. Muestre cómo se puede usar un multiplexor de 16 entradascomo el 74150

para generar la función Z = ABCD+ BCD + A.BV+ ABCD.

9-37. En el circuito de la figura 9-63 ~e muestra cómo un MUX de ocho entradas

se puede usar para generar una función lógica de cuatro variables, aunque

el MUX sólo tenga tres entradas de SELEcr. Tres de las variables lógicas A.,

B Y C están conectadas a las entradas de SELECT.La cuana variable D y su

inverso 15 están conectadas a entradas de dat~ seleccionadas del MUX, según lo requiera la función lógica deseada. Las otras entradas de datos del

MUX están conectadas a un BAJO o a un ALTO, de acuerdo con lo que necesite la función.

(a) Prepare una tabla de verdad en la que se muestre la salida Z para las 16

combinaciones posibles de las variables de entrada.

(b) Escriba la expresión de suma de productos para Z y simplifíquela para

verificar que

Z = CBA + DCBA + OCBA

+5V

-=

lo

11

'2

13

14

E

A

So

B

MUX

74HC151

51

C

52

D

Z

15

le

17

580

1

Capíl.ulo 9 I Clreultos lógicos MSI

27 of 36

c, D

9-38. Se puede emplear el método de la figura 9-63 para generar cualquier

ción lógica de cuatro variablessiguiendo los siguientespasos:

1. Prepararla tabla de verdad para la función deseada,con Z como la sali

2. Escribir la expres~n de¿u~ de pr~uctos .,para Z;-..!l2se siJ!!P.!i~ca.

p

ejemplo, z= DCBA + DCBA + DCBA + DCBA + DCBA + DCBA.

3. Buscartérminos que tengan la misma combinación de C, B y A, Y fact

zafios:

Z = DCBA + CBA (D + D) + CBA(D + D) + DCBA

= DCBA + CBA + CBA + DCBA

4. Considerar los términos que únicamente contienen C, B y A en fo

normal o complementada. Para cada uno de estos términos hay que

nectar la entrada de datos del MUX correspondiente a un nivel ALTO.

c.'BA -+ se conecta el nivel ALTO a la entrada 16

CBA -+ se conecta el nivel ALTO a la entrada 13

5. Considerar los términos que contienen la variable D. Conectar la variable

D o D a la entrada del MUX que corresponde a las variables CBA:

DCBA -+ se conecta D a la entrada Is

DCBA -+ se conecta D a la entrada 11

6. Conectar las entradas del MUX restantes a un nivel BAJO.

(a) Verificar el diseño de la figura 9-63 usando este método.

(b) Usar este método para implementar la función que produzca un nivel

ALTO cuando las cuatro variables de entrada estén en el mismo nivel,

o cuando las variables B y C estén en niveles distintos.

B

SECCiÓN 9-9

9-39. PREGUNTADE EJERCICIO

Para cada inciso indique si se refiere a un decodificador, codificador, MUX o

DEMUX.

(a) Tiene más entradas que salidas.

(b) Usa entradas de SELECT.

(c) Se puede usar en la conversión paralela a serial.

(d) Produce un código binario en su salida.

(e) Sólo una de sus salidas puede estar activa a la vez.

.

(f) Se puede usar para enrutar una señal de entrada a una de varias salidaS

posibles.

(g) Se puede usar para generar funciones lógicas arbitrarias.

9-40. Muestre cómo el decodificador 7442 se puede usar como demultiplexor de 1

a 8. (Sugerencia: consulte el problema 9-7.)

9-41. Aplique las formas de onda de la figura 9-58 a las entradas del DEM

74LS138de la figura 9-3OCa)como sigue:

D ~ A2

C-+ Al

B -+

Ao

Dibuje las formas de onda en las salidas del DEMUX.

A -+ El

ma~

581

28 of 36

9-12.Considereel sistemade la figura 9-32. Supongaque la frecuenciade reloj es

10 pps. Describa cuáles serán las indicaciones del panel de monitoreo para

cada uno de los siguientescasos.

(a) Todaslas puertascerradas.

(b) Todaslas puertasabiertas.

(c) Laspuertas 2 y 6 abiertas.

~3. Modifique el sistemade la figura 9-32 para manejar 16 puertas.Use un MUX

74150de 16 entradasy dos DEMUX 741$138.¿Cuántaslíneasvan al panel de

monitoreo remoto?

9-44. Dibuje las formas de onda en z. ~ O¡, Ozy ~ de la figura 9-33 para los siguientes datos de los registros: [..4]= 0011, [B] = 0110, [C] = 1001, [D] =

0111.

9-45. En la figura 9-64 se muestraun controlador de rejilla de visualizacióngráfica

de LCD de 8 X 8 mediante un 74HCl38 configurado como decodificador,y

un 74HCl38 configurado como demultiplexor. Dibuje 48 ciclos de reloj y los

datos de entrada necesariospara activar los píxeles que se muestranen el visualizador.

c, D

Columnas

o

o

--

Píxeles

Ic

Datos

1

E;

2

2

E3

3

3

~

4

4

5

5

~

6

6

A,

7

7

Ao

enCendidO~

Filas

74HC138

-=r~J...9.!j~~i=

+5

Ji

t__.:~~~

x

CLK

"

~ FIGURA

,

..

9-64

Problema 9-45.

T

1:'"

r

SECCiÓN

SECCiÓN 9-11

9-11

9-46. Considere e

el secuenciador de control de la figura 9-26. Describa cómo cada

una de las siguientes fallas afectará la operación.

(a) La entrada ~ del MUX está cortocircuitada a tierrci.

(b) Las conex.iones de los sensores 3 y 4 hacia el MUX están invertidas.

9 I Circuitos

582

T

29 of 36

9-47. Considereel circuito de la figura 9.24. Una prueba en el circuito produce

resultadosque se muestran en la tabla 9-8. ¿Cuálesson las causasposit

TABlA 9-8

T

9-48. Una prueba en el sistema de detección y vigilancia de la figura 9-32 pro

los resultados registrados en la tabla 9-9. ¿Cuálesfallas posibles podrían

sar esta operación?

TABLA 9-9

T

9-49. Una prueba en el sistema de detección y vigilancia de la figura 9-32 prodl

los resultados registrados en la tabla 9-10. ¿Cuálesson las posibles causas

falla en esta operación? ¿Cómo se puede verificar o eliminar esa falla?

TABLA 9-10

I'r..bl('mas

T

1 583

30 of 36

9-50. El sistema de transmisión síncrona de datos de la figura 9-33 no funciona de

manera correcta. Se usa un osciloscopio para monitorear las salidas del MUX

y del DEMUX durante el ciclo de transmisión, con los resultados que se

muestran en la figura 9-65. ¿Cuálesson las causas posibles del mal funcionamiento?

z

00

:

::'

:l'

:r--.l

I

,

'

,

,

I

I

r

I I

I I

.,

l'

I I

"

l'

II

I

I

.

I

I

I

I

I

I

,

I

I

I

I

,

I

,

I

I

I

I

I

I I

t2t-¡

I

I

~

~

,

O,

O

2

03

to

FIGURA

T

f

II

I

i ,

I

I

I

J...l

I

I

,

,

,

I

,

I

I

,

,

,

,

I

I

I

I

I

I

te

t7

:l'

:

:I

:I

:I

I

I

,

I

I

I

,

,

I

.

I

,

,

I

,

I

.

,

,

I

I

I

I

,

I

I

I

,

I

,

,

I

I

,

,

I

t.,

t

~

'1

I

I

I

.

I

,

I

I

,

I

,

.

I

I

,

I

I

I

te

tg

t

t1O

I

I

I

I

"

I

I

I

1,3

I

t14

r---l.--i

,

I

.

I

,

,

I

I

I

f

,

I

I

I

,

I

I

t'5

I

I

I

t18

I

t'7

I

I

I

,

,

.

I

,

,

I

I

,

.

I

,

I

,

r

I

I

t18

I

t19

9-65 Problema9-50.

9-51. El sistema de transmisión síncrona de datos de la figura 9-33 no funciona de

manera correcta, sus formas de onda se visualizan en un osciloscopio de alta

velocidad (figura 9-66). Note las transiciones en la señal Üt. Considere las

dos fallas posibles que se muestran a continuación. Para cada una, explique

si puede ser o no la causa del funcionamiento erróneo.

(a) Lasconexionesa los pines 51y So del DEMUX estáninvertidas.

(b) Las conexiones a los pines Q¡ y Qz del contador de palabras del receptor están invertidas.

Z

I

I

1

I

1

1

Ao

lA

I

B

2

J___lJ--;.-l

1

OO

01

O

2

03

¡

1

I

¡;

-' 1

1

I

I

1

I

I

I

I

I

I

I

I

I

1

I

I

I

I

.

I

I

to

1

II

1

I

I

I C

'C

1

1

1

I

3,

1

~I

I

0,

I

:1

:1

;I

;1

I

I

I

I

1

D3

I

-I--:.-.l___l...l

1

:1

I~

I;

I

1

I

1

I

,

I

;

1

:

I

;

1

:

1

I: ¡

I

I

1

1

I

'1

I:

l

11I

:

:

:

:1

:I1I

:

:l_..i_-

I

I

1

I

1

1

I

I

1

I

I

1

1

1

I

1

I

1

I

1

I

1

I

I

I

1

I

1

1

I

1

.

I

I

I

1

1,

l'

.

I

1

I

I

I

I

I

I

1

I

I

1

I

I

I

I

I

.

I I

'1

t2 t3

1

1

~

I

I

t11

I

I

t12

FIGURA 9-66

:I

I

1

t5

I

1

1

I

I

I

I

~

I

1

1

I

.

,

I

I

I

1

I

I

.

I

I

t7

I

I

t8

I

I

tg

Problema9-51.

1

I

I

I

811

I

I

t10

I

I

t13

11

1

I

'1

1

I

I

I

I

I

1

I

I

1

I

I

I

1

I

1

1

I

1

1

I

I

I

1

I

I

1

1

I

1

I

I

I

I

I

t14

I

I

t15

I

I

t18

1

1

t17

I

I

t18

I

1

t19

584 1

(:apílulo ~. / Circuitos lógicos MSI

31 of 36

c,D

D

T

SECCiÓN9-12

9-52. Rediseñe el circuito del problema 9-16 usando un comparador de magnituc

74HC85. Agregue una caracteñstica con respecto a "rebase de capacidad d«

copias" para que se active una salida de ALARMA si la salida OPERACI6~

no detiene la máquina cuando termine el número de copias que se solicitó.

9-53. Muestre cómo conectar varios 74HC85 para comparar dos números de 1(

bits.

SECCIÓN9-13

9-54. Suponga una entrada BCD de 69 para el convertidor de código de la figu~

9-40. Determine los niveles en cada salida 1'. y en la salida binaria final.

9-55. Un técnico prueba el convertidor de código de la figura 9-40 y observa lo~

siguientes resultados:

Entrada binarla

52

95

27

S!Ilide w..rla

0110011

1100000

0011011

¿Cuáles la falla probable del circuito?

B

SECCIONES9-14 A 9-16

9-56. PREGUNTA DE EJERCICIO

Cieno ofalso:

(a) Un dispositivo conectado a un bus de datos debe tener salidas de tre!

estados.

(b) La contención de bus ocurre cuando más de un dispositivo toma dato!

del bus.

(c) Se pueden transferir mayores unidades de datos sobre un bus de datO!

de ocho líneas que sobre uno de cuatro líneas.

(d) Un CI exdtador de bus por lo general tiene una impedanda alta de salida.

(e) Los registros bidireccionales y los búferes tienen líneas l/O comunes.

9-57. Con base en la configuración de bus de la figura 9-44. describa los requisito!

de la señal de entrada para transferir simultáneamente el contenido del regis

tro C a los otros dos registros.

9-58. Suponga que los registros de la figura 9-44 inicialmente son [A] = 1011

[.B) = 1000 y [C] = 0111. Las señales de la figura 9-67 se aplican a las entra

das de los registros.

(a) Determine el contenido de cada registro en los tiempos t}. t2. t3 Y 14.

(b) Describa qué pasaría si lEA fuera BAJO cuando ocurre el tercer pulso dc

reloj.

9-59. Suponga las mismas condiciones iniciales del problema 9-58 y bosqueje 1:

señal en D~ para las formas de onda de la figura 9-67.

58S

l~r(.bl('lIIas

32 of 36

9-61 Problemas9-58

~

OEA

~

OEB

~

OEC 1

-lEA

1

I

I

iEB

1

I

-

~L__I

;

1J

lEc 1

I

C LK

JL~-l-.4-J1

t,

O

~

I

t2

I

t3

11L+t4

9-60. En la figura 9-68 se muestrandos dispositivos que se agregaránal bus de datos de la figura 9-44. Uno es un conjunto de interruptores con búfer que se

puede usar para ingresar datos en forma manual hacia cualquiera de los re-

1 kO

SW3

Bus de detos

de 'a figura 9-44

.

~

\

DB3

082

08,

OSo

74HC125

+5V

220n

7406

Esw

RELOJ

(de la figura 9-U)

FIGURA 9-68

Problemas 9-60, 9-61 y 9-62.

(:apílulo 9 / Circuitos lógicos MSI

)86

33 of 36

gistros del bus. El otro dispositivo es un registro de salida que se usa para

clavar cualesquiera datos que estén en bus durante una operación de

renda de datos y mostrarlos en un conjunto de LEDs.

(a) Suponga que todos los registros contienen 0000. Resuma la secuencia

operacionesnecesariapara cargar los registros con los siguientesda;

de los interruptores:

[A]

C

= 1011,[B] = 0001,[C] = 1110.

(b) ¿Cuálserá el estado de los LEDs al final de esta secuencia?

9-61. Ahora que la circuitería de la figura 9-68 se ha agregado a la figura 9-44,

total de cinco dispositivos están conectados al bus de datos. El circuito de

figura 9-69(a) se usará ahora para generar las señales de ENABLE nec

con el fin de realizar las diferentes transferendas de datos sobre el bus de

tos. Usa un chip 74HC139 que contiene dos decodificadores idénticos e .

pendientes 1 de 4 con una ENABLE activa en BAJO. El decodifica

superior se usa para seleccionar el dispositivo que pondrá datos en el bus

datos (SELECf de salida) y el decodificador inferior se usa para decidir cuál

dispositivo tomará los datos del bus de datos (SELECf de entrada). Suponga,

que las salidas del decodificador están conectadas a las entradas de ENABLE

correspondientes de los dispositivos conectados al bus de datos. Asimismo

suponga que inicialmente todos los registros contienen 0000 en el tiempo ~'

y los interruptoresestánen las posicionesque se muestranen la figura 9-68.

~

(a) Determine el contenido de carga de registro en los tiempos t1, t2 Y t3

respuesta a las formas de onda de la figura 9-69(b).

(b) ¿Puedeocurrir la contención del bus en este circuito? Explique.

9-62. Muestre cómo se puede usar un 74HC541 (figura 9-47) en el circuito de la fi.

gura 9-68.

74HC138

."

{~:1

é.,O'.

o

--

~,

A1 ~3

~

Aa

C

CEe

CEA

2

01

00

-=

os,

_J--L__J--

oso--_J---'

I

IS,

II_

11-

{ IS1

A1

Aa

ISo

03

02

01

00

-=

r--L_-

ISo

iEc

iEe

iEA

(a)

RELOJ

lit

10

r-- -

Jl j1

1,

J~

13

2

(b)

FIGURA9-69 Problema9-61.

APLICACIONES PARA MICROCOMPUTADORA

C,N

9-63. En la figura 9-70 se muestra la circuitería básica para conectar un microprocegador (MPU) a un módulo de memoria. El módulo de memoria contendd

uno o más Cls de memoria (capítulo 11) que pueden recibir datos de la MPU

(una operación de ESCRI11JRA)o enviar datos a la MPU (una operación de

LECfURA). Los datos se transfieren sobre el bus de datos de ocho líneas. LaS

líneas de datos de la MPU y las líneas de datos l/O están conectados a este

~

587

l.robl(~m(ls

34 of 36

bus común. Por ahora nuestro interés se centrará en cómo la MPU controla

la SELECTdel módulo de memoria para una operación de LEC11JRA

o ESCRITURA.

Los pasos que involucra este proceso son:

1. La MPU coloca la dirección de memoria en sus líneas de dirección de salida A15 a

.-10.

2. La MPU genera la señal R/W Rara informar al módulo de memoria qué

operación se llevará a cabo: R/W = 1 para LEcruRA, R/W = O para ESCRIruRA.

3. Los cinco bits superiores de las líneas de dirección de la MPU los decodifica el 74Al.5138, el cual controla la entrada de ENABLE del módulo de

memoria. Esta entrada de ENABLE debe ser activa, para que el módulo

de memoria haga una operación de LECTURA o ESCRITURA.

4. Los otros 11 bits de dirección están conectados al módulo de memoria,

que los usa para seleccionar la localización específica interna de memoria a la que tendrá acceso la MPU, siempre y cuando la entrada de ENABLE esté activa.

5881

(:apílulo 9 / Clreultos lógicos MSI

35 of 36

Con el fin de leer en el módulo de memoria, o de escribir en éste, la MPU

debe poner la dirección correcta en las líneas de dirección para habilitar la

E

(a) Determine cuál o cuáles de estas direcciones hexadecimales aCtivaráel

módulo de memoria: 607F, 57FA, 5FOO.

(b) Determine qué intervalo de direcciones hex activará la memoria. (St.{gerencía: las entradas de Ao a Ato a la memoria pueden tener cualquier

b.

.'

.

memoria y luego pulsar CPal estadoALTO.

1I

'

!

)

com

macton.

(d) ¿Esposible que la MPU lea o escriba en ambos módulos al mismo tiempo? Explique su respuesta.

C, D

PROBLEMAS DE DISEÑO

9-64. El circuito de entrada por teclado de la figura 9-16 se usará como pal1e de

un cerrojo digital eleCtrónico que opera como sigue: cuando se activa una

salida ABRIR pasa a ALTO. Este nivel ALTO se usa para energizar un solenoide que retrae un pestillo y permite que se abra una puerta. Para aCtivar

ABRIR, el operador debe presionar la tecla BORRAR y luego ingresar la secuencia correcta de tres teclas.

(a) Muestre cómo se pueden agregar comparadores 74HC85 y cualquier ()tra

lógica necesaria para el circuito de entrada por medio del teclado, con el

fin de producir la operación de cerrado digital antes descrita para una

.

secuenCia

de

teclas

de

BORRAR-3-5-8.

(b) Modifique el circuito para activar una salida de ALARMA si el operador

ingresa algo que no sea la secuencia correcta de tres teclas.

SECCiÓN9-15

%5. Escriba el archivo fuente CUPL para implementar el codificador de la fi~ura

9-13 usando ecuaciones lógicas booleanas.

9-66. Escriba el archivo fuente CUPL para implementar el multiplexor de dos entradas de la figura 9-19 usando la anotación de la tabla de verdad.

RESPUESTASA LAS PREGUNTASDE REPASO

~ECCIÓN9-1

SECCIÓN9-4

i. No.

2. La entrada de ENABLE controla si la lógica

:lel decodificador responde o no al código binario de

~ntrada.

3. El 7445 tiene salidas de colector abierto

:¡ue pueden manejar hasta 30 V Y 80 mA.

4. 24 pi1es: 2 de ENABLE, 4 entradas, 16 salidas, Vcc, y tierra.

1. Un codificador produce un código de salida corres~

pondiente a la entrada aCtivada. Un decodiftcador aCTIva

una salida correspondiente a un código de entrada a~)llcado.

2. En un codificador de prioridad, el códig()

de salida corresponde a la entrada con el número ma~

yorque está activada.

3. BCD norntal = 0110.

4. (a) p~uce una .TPP ~ando se presiona una:e.cl;¡,

(b) convierte el acclonamlento de la tecla a su Códlg:L)

BCD,

(c) genera un pulso sin rebote para disparar el

,ECCIÓN 9-2

lb'

. a, ,C, f, g

2. Cierto.

,ECCIÓN 9-3'

l. LEDs: (a), (e), (O; LCDs: (b), (c), (d), (e).

!. (a) BCD de cuatro birs,

(b) ASCII de siete u ocho

Jits.

(c) valor binario para la intensidad del píxel.

contador de anillo,

(d) forma un contador de anillo

que sincroniza en secuencia los registros de salida,

(e) almacena códigos BCD generados por el acciona~

miento de las teclas.

SE:

1.

ger

cío!

(c) Suponga que ~e agrega un segundo módulo idéntico al circuito con su

dirección, R/W, y líneas l/O conectadas exactamente iguales que en el

primer -..!rlódulo, excepto que su entrada de ENABLE está conectada a la

salida °4, del decodificador. ¿Qué rango 4e direcciones hex activará este

segundo módulo?

,

LEC

SEI

. 1

,

,

dac

de )

2, (

ten¡

nar;

SE(

1 (

las~

cual

SE(

1, l

re!-11

con'

dí 11

h;~r

dire

Rt'SI)tlt'StétN

ét létN prt'AtlntétS

dt'

1 589

rt'pétNO

36 of 36

SECCIÓN 9-6

1. El número binario en las entradas de SELECTdetermina qué entrada de datos pasará a la salida.

2. 32 entradas de datos y 5 entradas de SELECT.

1..

"

~

SECCiÓN9-7

1. Conversión Paralela a serial, enrutamiento de datos,

~ generación de funciones lógicas, secuencias de operar', ciones.

2. Falso; se aplican a las entradas de SE't;;

~

c

LECf.

3. Contador.

~ SECCiÓN 9-8

ll.

Un MUX selecciona una de muchas señales de entrar da que pasará a su salida; un DEMUX selecciona una

, de muchas salidas para recibir la señal de entrada.

2. Cierto, con la condición de que el decodificador

tenga una entrada de ENABLE.

3. Los LEDs se iluminarán y apagarán en secuencia.

SECCiÓN 9-10

1. Con el fin de proporcionar un medio para expandir

las operaciones de comparadón a números con más de

cuatro bits.

2. °-4=B = 1; las otras salidas son O.

SECCiÓN 9-11

1. Un convertidor de código toma datos de entrada

representados en un tipo de código binario y los

" convierte a otro tipo de código binario.

2. Tres

digitos pueden desplegar visualmente valores decimales

hasta 999. Para desplegar visualmente 999 en binario

directo se requieren 10 bits.

SECCiÓN 9-12

1. Un conjunto de líneas de conexión al cual se pueden

conectar entradas y salidas de muchos dispositivos diferentes.

2. La contendón del bus ocurre cuando las

salidas de más de un dispositivo conectadas a un bus se

habilitan al mismo tiempo. Se evita controlando las entradas de ENABLE del dispositivo de manera que esto

no suceda.

3. Una condición en la cual todos los

dispositivos conectados a un bus están en el estado

Hi-Z.

SECCiÓN 9-13

l. 1011.

2. Cierto.

3. 0000.

SECCiÓN 9-14

1. Contencióndel bus.

2. Flotante,Hi-Z.

3. Proporciona salidasde baja impedancia. 4. Reduceel

número de pines del CI y el número de conexionesal

bus de datos.

5. Véasela figura 9-51.

SECCiÓN 9-15

l. Eone z O; Etwo =~Eth~

1,Atwo =~ne

=

~ero -:=-Q;. 2. Eone . Etwo . Ethree. Atwo .

Aone . Azero

3. Q¡

4. ~