Ejemplos de implementación de nuevas instrucciones en el

Anuncio

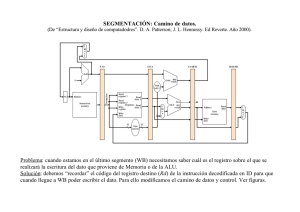

Ejemplos de implementación de nuevas instrucciones en el procesador monociclo ● ● ● ● Aquí se muestra la solución a algunos de los apartados del ejercicio 1 que se hicieron en clase. En todos los casos, hay soluciones alternativas que también serían válidas (e incluso mejores). Estas soluciones son parciales, ya que incluyen sólo el formato de instrucción, el dibujo con los cambios al camino de datos y el valor de las señales de control. En una solución completa habría también un análisis de la instrucción, una explicación detallada de los cambios en el camino de datos y una explicación de cómo afectarían los cambios realizados a las instrucciones preexistentes (como mínimo, cuál sería el valor de las nuevas señales de control). También conviene incluir un comentario de las alternativas de diseño existentes y una justificación de porqué se ha elegido la solución propuesta. Camino de datos y de control básico Inst. [25-0] Desp 32 28 Dirección de salto [31-0] Izq 2 26 4 32 Inst. [31-26] Control 32 Inst. [25-21] PC Dirección de lectura Instrucción [31-0] Memoria de instrucciones PC+4 [31-28] 32 4 Sum Inst. [20-16] 5 5 5 Inst. [15-11] 5 Inst. [15-0] 0 M5 U X 1 32 32 RegDest SaltoIncond SaltoCond LeerMem MemAReg ALUOp EscrMem FuenteALU EscrReg Sum Registro de Lectura 1 Registro de Lectura 2 Registro de Escritura Archivo de Registros Dato a Escribir 16 Inst. [5-0] Ext. Signo 6 32 Dato Leído 1 Dato Leído 2 1 M U X 0 32 Desp Izq 2 2 0 M 32 U X 1 0 M 32 U 1 X ALU Dirección Memoria de datos 32 Dato a Escribir 32 32 Control de la ALU 3 32 Dato Leído 32 0 M U X 1 bzr Inst. [25-0] Desp 32 28 Dirección de salto [31-0] Izq 2 26 4 32 Inst. [31-26] Control 32 Inst. [25-21] PC Dirección de lectura Instrucción [31-0] Memoria de instrucciones PC+4 [31-28] 32 4 Sum Inst. [20-16] 5 5 5 Inst. [15-11] 0 M5 U X 1 5 Inst. [15-0] RegDest SaltoIncond SaltoCond LeerMem MemAReg ALUOp EscrMem FuenteALU EscrReg cop(6) rs(5) rt(5) rd(5) desp(5) func(6) bzr 10 11 xx 0 0 X 0 1 0 X 01 0 10 0 Registro de Lectura 1 Registro de Lectura 2 Sum 16 32 0 M U 1 X 0 M 32 U X 1 1 M U X 0 SaltoBzr 1 2 32 Dato Leído 1 Dato Leído 2 Ext. Signo 6 32 Desp Izq 2 2 Registro de Escritura Archivo de Registros Dato a Escribir Inst. [5-0] EJEMPLO 0x04000000: bzr $10, $11 ... ... etiq:0x0400002C: ... FORMATO 32 0 32 00 M 32 U 01 X 10 ALU Dirección Dato Leído Memoria de datos 32 Dato a Escribir 32 32 Control de la ALU 3 32 Hay una solución mejor usando el formato de instrucción I. ¿Cómo sería? 32 0 M U X 1 abs Inst. [25-0] Desp 32 28 Dirección de salto [31-0] Izq 2 26 4 32 Inst. [31-26] Control 32 Inst. [25-21] PC Dirección de lectura Instrucción [31-0] Memoria de instrucciones PC+4 [31-28] 32 4 Sum Inst. [20-16] 5 5 5 Inst. [15-11] 0 M5 U X 1 5 Inst. [15-0] Hay una solución mejor que hace que la ALU reste en unos casos y que sume en otros. ¿Cómo sería? 32 32 RegDest 1 SaltoIncond 0 SaltoCond 0 LeerMem 0 MemAReg 1 ALUOp 01 EscrMem 0 FuenteALU 0 EscrReg 1 Sum Registro de Lectura 1 32 Dato Leído 1 Registro de Lectura 2 Dato Leído 2 0 M 32 U 1 X Registro de Escritura Archivo de Registros Dato a Escribir 16 Inst. [5-0] Ext. Signo ALU Dirección Memoria de datos 32 Dato a Escribir 32 32 6 Control de la ALU M 0 U X 1 3 32 MSB EJEMPLO 0x04000000: abs $10,$11 FORMATO cop(6) rs(5) rt(5) rd(5) desp(5) func(6) abs 0 10 11 0 0 1 M U X 0 32 Desp Izq 2 2 0 M 32 U X 1 Abs 1 Dato Leído 32 0 M U X 1 call 32 Desp Izq 2 Inst. [25-0] 28 26 Inst. [31-26] 1 0 M U 1 X Registro de Lectura 1 RegFuente 5 Dirección de lectura Instrucción [31-0] Memoria de instrucciones 29 Inst. [20-16] 5 Inst. [15-11] 5 cop(6) 4 dirección(26) 0x4001234>>2 5 29 Inst. [15-0] EJEMPLO 0x04000000: call eti ... ... eti: 0x04001234: ... FORMATO 5 00 M 5 U 01 X 11 Registro de Lectura 2 16 Desp Izq 2 0 M 32 U 1 X 1 M U 0 X 32 32 Dato Leído 2 Ext. de Signo 6 Sum Dato Leído 1 Registro de Escritura Archivo de Dato a Registros Escribir Inst. [5-0] 32 11 1 X 0 1 2 00 1 10 1 Control Inst. [25-21] 5 PC 32 RegDest SaltoIncond SaltoCond LeerMem MemAReg ALUOp EscrMem FuenteALU EscrReg 32 32 PC+4 [31-28] 4 Sum 4 32 00 M U 01 X 4 ALU Dirección Dato Leído Memoria de datos 32 0 M U 1 X 10 32 32 Control ALU 0 M U 1 X Dato a Escribir 32 3 FuenteDato 1 32 Esta solución usa el formato J y, por tanto, direccionamiento pseudodirecto. Hay una solución usando el formato I y direccionamiento relativo al PC. ¿Cómo sería?