Examen final IC parte A Ejercicio 1

Anuncio

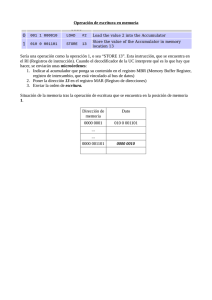

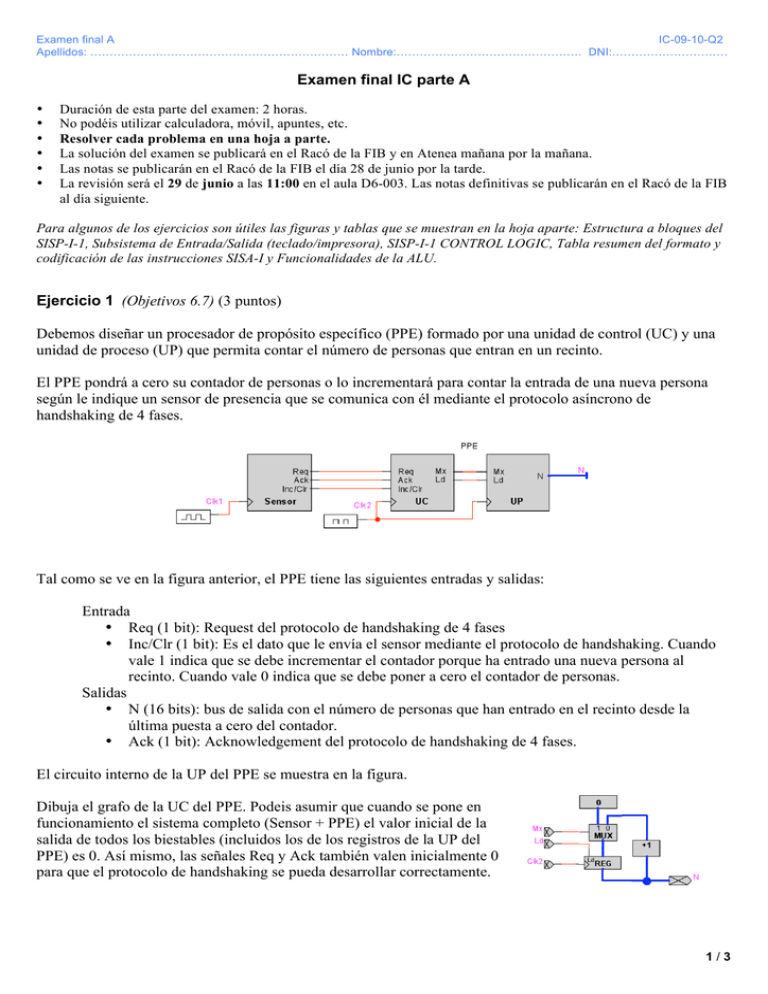

Examen final A IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… Examen final IC parte A • • • • • • Duración de esta parte del examen: 2 horas. No podéis utilizar calculadora, móvil, apuntes, etc. Resolver cada problema en una hoja a parte. La solución del examen se publicará en el Racó de la FIB y en Atenea mañana por la mañana. Las notas se publicarán en el Racó de la FIB el día 28 de junio por la tarde. La revisión será el 29 de junio a las 11:00 en el aula D6-003. Las notas definitivas se publicarán en el Racó de la FIB al día siguiente. Para algunos de los ejercicios son útiles las figuras y tablas que se muestran en la hoja aparte: Estructura a bloques del SISP-I-1, Subsistema de Entrada/Salida (teclado/impresora), SISP-I-1 CONTROL LOGIC, Tabla resumen del formato y codificación de las instrucciones SISA-I y Funcionalidades de la ALU. Ejercicio 1 (Objetivos 6.7) (3 puntos) Debemos diseñar un procesador de propósito específico (PPE) formado por una unidad de control (UC) y una unidad de proceso (UP) que permita contar el número de personas que entran en un recinto. El PPE pondrá a cero su contador de personas o lo incrementará para contar la entrada de una nueva persona según le indique un sensor de presencia que se comunica con él mediante el protocolo asíncrono de handshaking de 4 fases. Tal como se ve en la figura anterior, el PPE tiene las siguientes entradas y salidas: Entrada • Req (1 bit): Request del protocolo de handshaking de 4 fases • Inc/Clr (1 bit): Es el dato que le envía el sensor mediante el protocolo de handshaking. Cuando vale 1 indica que se debe incrementar el contador porque ha entrado una nueva persona al recinto. Cuando vale 0 indica que se debe poner a cero el contador de personas. Salidas • N (16 bits): bus de salida con el número de personas que han entrado en el recinto desde la última puesta a cero del contador. • Ack (1 bit): Acknowledgement del protocolo de handshaking de 4 fases. El circuito interno de la UP del PPE se muestra en la figura. Dibuja el grafo de la UC del PPE. Podeis asumir que cuando se pone en funcionamiento el sistema completo (Sensor + PPE) el valor inicial de la salida de todos los biestables (incluidos los de los registros de la UP del PPE) es 0. Así mismo, las señales Req y Ack también valen inicialmente 0 para que el protocolo de handshaking se pueda desarrollar correctamente. 1/3 Examen final A IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… Ejercicio 2 (5.5 puntos) Es vol afegir una nova instrucció que pugui realitzar una operació AND entre els dos bits d'una certa posició de dos registres. És a dir, donats dos registres Ra i Rb i la posició b (entre 0 i 15), es vol que la nova instrucció realitzi una operació AND entre els bits que es troben a la posició b d'aquests dos registres. El resultat es guardarà al registre Rd de manera que, tots els bits de Rd valdran 0 excepte el bita la posició b que prendrà per valor 0 o 1 en funció del resultat de l'operació AND. Per exemple, si R2 i R3 prenen per valor 0000 0000 0010 1001 i 1111 0101 1010 1101, respectivament, si realitzem l'operació AND entre els seus bits a la posició 3 (recorda que el bit de menys pes diem que és el bit que es troba a la posició 0), el valor guardat al registre destí després d'executar la nova instrucció serà 0000 0000 0000 1000. La sintaxi de la nova instrucció seria la següent: ANDB Rd, Ra, Rb, b ;Rd=(Ra AND (0x0001<<b)) AND (Rb AND (0x0001<<b)) a. (Objectiu 10.4) Escriu una seqüència d’instruccions del llenguatge assemblador SISA-I que emmagatzemi al registre R7 el mateix resultat que la instrucció ANDB R7, R2, R3, 4 (pots modificar el contingut de qualsevol dels registres del banc de registres sempre que al final de l’execució d’aquestes instruccions, el registre R7 contingui el resultat correcte de l’operació). (1 punt) b. (Objectiu 6.4) Dibuixa l’esquema intern d’un circuit lògic combinacional, el símbol del qual us donem a continuació: (1 punt) El circuit ANDb té dos busos d’entrada X i B i un bus de sortida W, tots ells de 16 bits, i implementa la funció: W = X AND (0x0001<<B) NOTA: pots utilitzar qualsevol bloc combinacional dels usats per construir el processador SISP-I-1. Pots utilitzar també un bloc, que pots anomenar “1”, que generi el valor 0x0001 representat en 16 bits. c. (Objectiu 11.8) Implementació de la nova instrucció. i. Dóna una codificació per aquesta nova instrucció. (0,5 punt) ii. Faries canvis a la Unitat de Procés General? En cas afirmatiu, quines modificacions s'han de fer? Si has de realitzar qualsevol modificació a un bloc no cal que el dibuixis sencer, sempre i quan les teves indicacions no continguin cap ambigüitat que afecti a la interpretació del nou disseny. (1,5 punts) NOTA: pots utilitzar qualsevol bloc combinacional dels usats per construir el processador SISPI-1, així com el nou bloc que has dissenyat ANDb. 2/3 Examen final A IC-09-10-Q2 Apellidos: ……………….………………………………………… Nombre:………………………………………… DNI:………………………… iii. Faries canvis a la Unitat de Control General? En cas afirmatiu, quines modificacions s'han de fer perquè s'interpreti la nova instrucció i es generin les paraules de control adequades, garantint que les instruccions originals del llenguatge assemblador SISA-I segueixen funcionant correctament. A més d'indicar el contingut de la ROM que correspon a la nova instrucció ANDB, si uses algun nou senyal que hagi de generar la ROM, indica clarament quin valor prendrà aquest senyal per a cada una de les instruccions del SISA-I, diferenciant quan ha de valer 0, 1 o X, si no importa el seu valor. (1,5 punts) NOTA 1: els senayls s’han d’escriure en el mateix ordre de la ROM (Bnz, Bz, Wr-Mem, Rd-In, Wr-Out, WrD InLD/Alu, In/Ld, Rb/N, OP1, OP0, Mx@A, MxF, Mx@B, MxN) i el(s) nou(s) al principi de tot. NOTA 2: l’ordre de les instrccions ha de ser el mateix que a la ROM (A / L, CMP, ADDI, LD, ST, MOVI, MOVHI, BZ, BNZ, IN, OUT, ANDB) segui t de la nova instrucció. Ejercicio 3 (Objectiu 6.4) (1.5 puntos) Suposa que afegim una nova instrucció anomenada ANDBR, la sintaxi de la qual és la següent: ANDBR Rd, Ra, Rb, Rc ;Rd=(Ra AND (0x0001<<Rc)) AND (Rb AND (0x0001<<Rc)) On Rd, Ra, Rb i Rc són registres del banc de registres (fixa’t que caldria ampliar el banc de registres per a que tingués tres busos de lectura A, B i C). Escriu una seqüència d’instruccions del llenguatge assemblador SISA-I ampliat amb la nova operació ANDBR que, donat el contingut dels registres R0 i R1, emmagatzemi a R2 el nombre de posicions que valen 1 alhora a tots dos registres. És a dir, si R0=0001 0101 0000 1110 i R1=1101 0101 0000 0000, el contingut del registre R2 després d’executar el fragment de codi que proposis ha de ser 0x0003, ja que les posicions 8, 10 i 12 valen 1 a tots dos registres. NOTA 1: no pots utilitzar l’antiga instrucció AND. NOTA 2: pots modificar el contingut de qualsevol dels registres del banc de registres sempre que utilitzis correctament el valor inicial dels registres R0 i R1 i que el registre R2 contingui el resultat correcte de l’operació als final de l’execució del programa. 3/3