El transistor

Anuncio

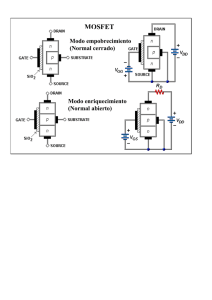

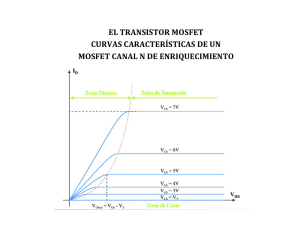

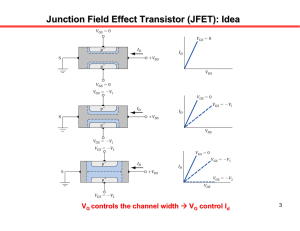

Tema 7. El transistor Tema 7. El transistor Objetivos: ● ● Entender cualitativamente el funcionamiento de los transistores de unión y de efecto campo. Conocer algunas aplicaciones de transistores. Shockley, Bardeen, Brattain (1948) Nobel 1956 El transistor bipolar de unión Tema 7. El Transistor 7.1 El transistor bipolar de unión (BJT). 7.1 Transistor bipolar de unión BJT (Bipolar Juntion Transistor) El transistor de unión como amplificador. 7.2 Transistores de efecto campo. P Emisor Transistores de efecto campo de unión (JFET). Transistores de efecto campo metal-óxidosemiconductor (MOS-FET). N Base P Colector E N Emisor C P E C B El transistor bipolar de unión N Colector Base B El transistor bipolar de unión 7.1 E P Emisor P N Base C P Colector P B Transistor bipolar de unión a 300 GHz N - E + + 0,001mm V V0 7.1 E - Concentración de portadores El transistor bipolar de unión E P Emisor Colector nn0 np0 P N P Concentración de portadores de carga P pp0 N Base C B P P - E + p'p0 + E Análogo a dos diodos con polarización directa: Saturación n'p0 pn0 V V0 N IE + I C = I B El transistor bipolar de unión E Transistor polarizado en forma activa 7.1 C B P 7.1 E B P 7.1 C P P N N I E =I BIC I C ≫I B - Corte E + + E V V0 - Análogo a dos diodos con polarización inversa: Activa IE=IC=IB=0 - E + + InB I E≈ IC InC IBB I C =β I B IpC IpB Transistor polarizado en forma activa E Transistor polarizado en forma activa (P) Emisor (N) Base 7.1 (P) Colector I E =I BIC P Emisor N Base P Colector I C ≫I B I pB IE E E IC I nB I nC I E≈ IC I BB pp0 P Concentración de portadores de carga nn0 IB p'p0 np0 Difusió n P n'p0 E N E I C =β I B (región activa) β factor de ganancia Transistor polarizado en forma activa (P) Emisor (N) Base (P) Colector IpB, huecos que por difusión van del emisor IpB a la base I E InB InC IC Configuraciones del transistor Base N Colector hay 4 variables que dependen del tipo de conexión: Vsalida, Ventrada, Isalida, Ientrada. E C B C E B C E B IB IBB, electrones procedentes del circuito para recombinarse IE = IpB + InB P N Emisor IBB InB, electrones que van de la base al emisor 7.1 Variables: VBE, VCB, IE, IC IB = -InC + IBB +InB IC = IpB - IBB + InC Curva característica de entrada Colector común Emisor común Base común InC, corriente de electrones del colector a la base. Variables: Variables: VCB, VCE, IB, IE VBE, VCE, IB, IC Curva característica de salida Si variamos el valor del generador VBB de la malla de entrada, tomando valores de IB y VBE podemos obtener la característica de (la malla de) entrada. Como vemos, el la característica del diodo base-emisor Ajustando VBB fijo un valor de IB que voy a mantener constante (por ejemplo IB = 10 mA). Ahora variando VCC mido valores de VBE y IC y obtengo la correspondiente curva de IB = 10 mA. Curva característica de salida 7.1 Emisor común: variables Zona entre 1 y 2: ZONA DE SATURACIÓN. E-B directa. C-B directa. Variables: VBE, VCE, IB, IC E-B directa. C-B inversa. Zona a partir de 3: ZONA DE RUPTURA. E-B directa. C-B muy en inversa. VBE ≈ 0,7 V para el silicio VBB Base N Colector IB IC VCE VBE E +VCC IC IC = βIB (en activa) RB VBB P B VBE = VBB - IB RB VCE = VCC - IC RC N Emisor RC C RB Zona entre 2 y 3: ZONA ACTIVA. B RC C IB E VCC IC ( mA) Curva característica del transistor CE IB = 80 µA Recta de carga y punto de funcionamiento Q 1 Región de saturación 4 VBB V CC 4 Ruptura IB = 20 µA RB VCE (V) IB VBB B VCC VCE = -IC RC+ VCC IB3 IC VCE VBE IC VCE IB VBE IB4 RC RC C IB = 0 µA RB IC 3 Región de corte IB = 40 µA RC 2 Región activa IB = 60 µA Q IB2 VCC E re c ta de ca IB1 • En región activa: unión EB con polarización directa, BC con polarización inversa. Aplicación en amplificación. • En región de corte: les dos uniones polarizadas inversamente: circuito abierto. • En región de saturación: las dos uniones polarizadas directamente: cortocircuito. O Punto de trabajo: IB rg a VCC VCE I C= V CC −V CE RC VCE IC RC Punto de trabajo: IB IC IC IB4 V CC RC IB4 V CC RC RC IB3 RB IB2 VBB RC IB3 RB IC IB VBE VCE IB2 VCC IB1 VBB IC IB VCE VBE VCC IB1 V VCC VCE VCC elCEsilicio VBE ≈ 0,7 V para VBE = VBB - IB RB VCE = -IC RC+ VCC I C= Punto de trabajo: IB V CC −V CE RC Punto de trabajo (Q) C B IC IB4 V CC RC E RC IB3 RB IB2 VBB IC IB VBE VCE VCC IB1 VCC VCE VCE = -IC RC+ VCC I C= V CC −V CE RC I B= V e −V γ RB Recta de carga V CC =V CE IC R C 7.1 El transistor como conmutador Circuito inversor simple C Si VBB ↑, IB = ↑, IE ≈IC = VCC/RC saturación +VCC B RC RB cortocircuito CE VCE = 0 IC E A Vsalida Ventrada Si VBB = 0 o < 0,7 V, IB = 0, VBB (V) 0,7 0,8 0,9 1 1,2 1,4 1,6 1,8 2 2,2 2,3 VCE (V) 10 9,38 8,75 8,13 6,88 5,63 4,38 3,13 1,88 0,63 0 Ic (mA) 0 0,63 1,25 1,88 3,13 4,38 5,63 6,88 8,13 9,38 10 IB (µA) 0 6,25 12,5 18,75 31,25 43,75 56,25 68,75 81,25 93,75 100 INVERSOR Y = not A IE ≈IC ≈ 0, VCE = VCC corte A circuito abierto VCE = VCC VCC Ventrada Y Vsalida VCE Curva de transferencia Vs (Ve) El transistor de unión: amplificador 7.1 IC corte A V CC I C=β I B activa D V sat saturación V sat VEB Vγ V ' V CC =V s I C RC I C=β I B =β I C= V CC −V s V e−V γ RC V '=V γ RB ∆(-IC) = gm ∆VEB RB V CC−V sat ΔV EB β RC E + Vi IB B _ _ C =RL g m gm : transconductancia Transistor de unión: modelización IE ΔV AD ∆VAD = RL∆IC IC IE + Vo + Vi _ Transistores de efecto campo IC IC + Vo _ ● FET ● Monopolares ● Control por voltaje ● Muy alta integración Transistores de efecto campo ● ● Transistores de efecto campo de unión (JFET) El transistor de efecto de campo de unión JFET (Juntion Field Effect Transistor) Transistor de efecto campo de unión (JFET) Transistor de efecto campo metal-óxidosemiconductor (MOSFET) Contactos óhmicos Drenador D Región de agotamiento n p p Puerta G Fuente S Transistores de efecto campo de unión (JFET) Transistores de efecto campo de unión (JFET) 7.2 D G S El transistor de efecto de campo de unión JFET D n D p S n p p n G n IDSS S S transistor de canal p. IG D VDD IG D P P VP Voltaje de estrechamiento F F Transistores de efecto campo de unión (JFET) S n ID D p p VGS=0 VDD G ID S n ID G S G ID Estrechamiento del canal, aumento de la resistencia Región de comportamiento óhmico VP VDS Manteniendo nula la tensión entre la fuente y G, VGS, al aumentar la tensión entre Drenador y Fuente VDS, la intensidad ID aumenta, al tiempo que se estrecha el pasillo debido al incremento de la de las uniones p-n y la ampliación de la región de agotamiento . G S ID VDD G Para VGS= 0 IDSS 7.2 D D p p VDD Para VGS= 0 ID S n ID ID p VDS Al aumentar la tensión entre Drenador y Fuente VDS, la intensidad ID aumenta, al tiempo que se estrecha el pasillo debido al incremento de la de las uniones p-n y la ampliación de la región de agotamiento. El pasillo se cierra para VDS = VP; tensión para la que ID deja de aumentar. Transistores de efecto campo de unión (JFET) 7.2 D D p P. inversa G G ID transistor de canal n. p ID p p n D ID Corriente de saturación, IDSat IDSS Estrechamiento del canal, aumento de la resistencia Región de comportamiento óhmico Voltaje de estrechamiento, VP VP VDS Al aumentar la tensión entre Drenador y Fuente VDS, la intensidad ID aumenta, al tiempo que se estrecha el pasillo debido al incremento de las uniones p-n y la ampliación de la región de agotamiento El pasillo se cierra para VDS = VP Transistores de efecto campo de unión (JFET) Transistores de efecto campo de unión (JFET) 7.2 D G 7.2 D G S Con valores negativos de VGS el pasillo se cierra antes, siendo la corriente de saturación menor n S p ID IDSS D ID G IDSS ID VGS= 0 V D VVPP (para VGS=0) I Dsat =I DSS 1− IDSat2 VGS= -3 V VGS= -VP VDS IDSat1 VGS= -VP VDS VVPP (para VGS=0) G V GS 5 IDSS S ID=0 VGS= -Vp 7.2 El Transistor de efecto de campo metal-óxidosemiconductor MOSTFET (Metal Oxide Semiconductor Field Effect Transistor) b) S VGS= 0 V G Metal D 2 S VGS = 0 V a) ID (mA) I Dsat =7,8 1− G VP ID Transistores de efecto campo MOSFET D 2 V GS D VGS= -1 V VGS= -3 V Intensidad de saturación IDS=f(VGS) VDD VDS> Vp G IDSat3 S IDSat1 ID G VGS< 0 VGS= -1 V IDSat2 p ID p VGS= 0 V IDSat3 n S VDD p VGS< 0 ID S D S Óxido G D Semiconductor 5 VGS= -1 V n+ p n+ n+ p n+ Metal VP 1 VGS (V) -5 -4 -3 -2 -1 5 0 10 VP = 5 V Modo enriquecimiento” VDS (V) 15 Modo “agotamiento” VGS= -VP Transistores de efecto campo MOSFET 7.2 MOSFET de enriquecimiento n Metal S G D S Óxido G n n p p G S G nMOS-FET de enriquecimiento sustrato p S G pMOS-FET S de enriquecimiento D sustrato n G nMOS-FET de agotamiento D sustrato p S G pMOS-FET de agotamiento sustrato n S n p •Puerta, gate en inglés, simbolizado con G; que se conecta a la placa metálica. •Fuente (Source) y drenador (Drain), ambos simétricos, que se internan en el sustrato. •Sustrato (Body), generalmente conectado eléctricamente con la fuente. D D SiO2 n de agotamiento Formado por una placa de metal y un semiconductor, separados por una zona de óxido del semiconductor - por ejemplo SiO2 - de unos 100 nm de espesor. Posee cuatro electrodos: D Contactos metálicos n Metal de enriquecimiento G S D Semiconductor n 7.2 D Formación del canal en el MOSFET de enriquecimiento n Formación del canal en el MOSFET de enriquecimiento n D D G VGS =0 ID = 0 S G VGS =0 G G ID = 0 S S S n p D D n n n n P. inversa VDS p VDS p ID (mA) Región de agotamiento n p Región de agotamiento VGS< VT P. inversa Formación del canal en el MOSFET de enriquecimiento n D G VGS>VT G e- atraídos por la puerta + ID S Formación del canal en el MOSFET de enriquecimiento n D +++++++++++ n ID S D ----------------- +++++++++++ n n ID (mA) D ----------------- VDS p G VGS>VT G S S VDS n VDS p ID (mA) I DSat VGS>VT VGS< VT Al aumentar VDS, se estrecha el canal, alcanzándose la I de saturación, IDS VGS>VT Región de agotamiento VGS< VT VDS VDS D En ausencia de canal para VGS = 0, no hay corriente ID. Es necesario un valor mínimo de voltaje umbral VT positivo de VGS para que se forme el canal. Aumentando VGS aumenta el valor de la corriente de saturación Característica MOSFET de enriquecimiento de canal n D n+ + VD n+ p S + VG G + VDS D + + + + + - - - - - - n+ -- -- - - - - - n+ - p ID (mA) S n+ S + + VG VDS=VDsat G D + + + + + + -- -- -- -- -- -- -- n + -- p VGS= 7 V VGS= 6 V VGS= 5 V VGS= 4 V VGS= VT VDS G S Característica MOSFET de enriquecimiento de canal n G S D En ausencia de canal para VGS = 0, no hay corriente ID. Es necesario un valor mínimo de voltaje umbral VT positivo de VGS para que se forme el canal. Aumentando VGS aumenta el valor de la corriente de saturación G D n+ + VD S n+ p Sat + VDS D + + + + + - - - - - - n+ -- -- - - - - - n+ - p ID (mA) ID (mA) ID + VG G =K V GS−V T 2 S n+ G S + + VG VDS=VDsat G D + + + + + + -- -- -- -- -- -- -- n + -- p VGS= 7 V VGS= 6 V VGS= 5 V VT VGS= 4 V 1 2 3 4 5 6 7 8 VGS (V) VGS= VT VDS MOSFET de agotamiento n D G VDS S D ID = 0 D ID G G G S S S D VGS >VT VGS< VT 7.2 n n ID (mA) n VGS= 7 V p VGS= 6 V VGS= 5 V VGS= 4 V VGS= VT D G S VDS MOSFET de agotamiento n VGS = 0 7.2 MOSFET de agotamiento n D G S G S S D n - - - - - - - - -n -------- ID —————— D n n n- - -- -- -- -- -- -- -- -- -- -- -- -- - n + + ++ ++ ++ ++ ++ ++ ++ ++ ++ ++ + + + VDS p ID (mA) G- VGS < 0 ID 7.2 ID (mA) 10 VDS p 10 VGS= 0 V VGS= 0 V Con VGS=0 ya existe canal y hay corriente de electrones 5 Con VGS<0, los e- del canal son repelidos hacia la zona p, recombinándose con huecos. La corriente de saturación disminuye. 5 VGS < 0 G S 10 15 VDS (V) 5 MOSFET de agotamiento n VGS > 0 S - - - - - - - -n- - - - - - - - - - - - - - - - - - n p ID (mA) VGS > 0 V 10 VGS= 0 V Con VGS>0, los e atraidos. La corriente de saturación aumenta. (como el MOSFET de enriquecimiento) - 5 VGS < 0 7.2 D ID n D VDS + 10 15 VDS (V) n + p ID (mA) I D =I DSS 1− I D =8 1− V GS Vp V GS 4 S D n n - VG + VDS G S G S D + + p ID (mA) VGS= 1 V 2 + VDS=VDsat - - - - - - - - - - - - n n - -- -- - - - - - 10 10 IDSS 2 5 VGS= 0 V 5 VGS= -1 V VP -4 -3 5 VDS (V) 15 G G+ +++++++++ 10 7.2 Característica MOSFET de agotamiento de canal n 5 D VGS= -2 VGS= -3 V -2 -1 0 1 VGS (V) 5 10 15 VDS (V) MOSFET de agotamiento n G D I D VDS Lógica de diodos: puertas AND y OR 7.2 D I =0 D G S S VGS < V VGS>=0 ID (mA) VGS= 1 V 10 VGS= 0 V 1N914 5 VGS= -1 V VGS= -2 VGS= -3 V 5 10 15 1N914 VDS (V) Aplicaciones: circuitos lógicos inversores 7.3 De las válvulas de vacío al CMOS 1950: Abandono de las válvulas de vacío y sustitución por transistores individuales 2N4124 1960: Circuitos integrados en substrato de silicio lógica de resistencias y transistores (RTL) 2N4124 lógica de diodos y transistores (DTL) 1980: Transistores de efecto campo 1993: Tecnología CMOS 2N4124 lógica de transistores (TTL) Aplicaciones: circuitos lógicos, tecnología CMOS 7.3 Aplicaciones: memoria RAM DRAM BIT D G S FILA SRAM Puerta NAND Inversor (NOT) Se almacena un “1” en la celda cargando el condensador mediante una VG en fila y VD en bit La lectura se hace aplicando VG en fila y midiendo la corriente en la línea bit La lectura es un proceso destructivo. Hay que restaurar el valor leído 7.3 Aplicaciones: memorias ROM 7.3 Aplicaciones: CCD CMOS sensor CCD EPROM MOSFET ROM Aplicaciones: TFT Estructura DRAM con celda LCD y LED RGB 7.3 7.3