PRACTICA nº 4

Anuncio

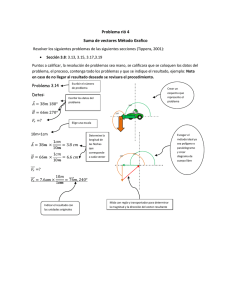

Grado en Ingeniería de Tecnologías de Telecomunicación 3er Curso Sistemas Electrónicos Digitales PRACTICA nº 4 Descripción VHDL a nivel algorítmico y síntesis de un procesador dedicado elemental para la caracterización de vectores binarios y su conversión a enteros decimales con aproximación Objetivos: Diseño y síntesis sobre un dispositivo FPGA de un pequeño procesador hardware dedicado a obtener el número de 1s en un número binario, las posiciones más y menos significativa con valor 1, su valor decimal equivalente (asumiendo la representación en binario sin signo) y su valor aproximado con el menor número de 1s según un criterio establecido. Descripción a nivel de algoritmo basada en la utilización de un “procedure”. Descripción estructural basada en módulos descritos a nivel de algoritmo. Síntesis sobre FPGA y comparación de ambas implementaciones. Herramientas CAD:Quartus II©. Instrumentación: -. Material fungible o de laboratorio: -. Se desea realizar un circuito capaz de recibir como entrada un vector (“std_logic_vector”) y dar como salidas: La posición de la componente ‘1’ más significativa del vector; la posición de la componente ‘1’ menos significativa; el numero de ‘1s’; el valor entero considerando al vector como un entero sin signo; el valor aproximado (con un número de ‘1s” reducido) del vector. En el caso de que ninguna de las componentes del vector sea ‘1’, las posiciones de los ‘1s’ más significativo y menos significativo se codificarán como -1. Para obtener el valor aproximado se considerará el siguiente criterio: sea p = 0, 1, 2, …, n-1, la posición de la componente ‘1’ más significativa; si el número de ‘1s’ detrás del más significativo es mayor que p-3, el valor del entero se aproximará por 2p+1, excepto que p sea la posición más significativa del vector o que el vector no tenga ninguna componente ‘1’. Parte 1:Diseño del procesador elemental utilizando para su descripción el lenguaje VHDL. La descripción, de tipo algorítmico, consistirá en una entidad principal que incluya un procedure. El procedure deberá ser declarado y descrito en un package. La caracterización del vector: número y posiciones de los ‘1s’ y valor decimal equivalente deberán ser obtenidos por el procedure, mientras que la entidad principal obtendrá el valor aproximado según el criterio establecido. a) Implementar el procesador elemental. Suponer que el vector es de tamaño 8. 1 de 3 Grado en Ingeniería de Tecnologías de Telecomunicación 3er Curso Sistemas Electrónicos Digitales Una descripción VHDL del package conteniendo la declaración del procedure conforme con lo anterior se muestra en la figura 1: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; package paquete_procedu is procedure vector_to_int (signal data_in: in std_logic_vector; data_out: out integer; ms : out std_logic_vector; ls : out std_logic_vector; nu_un : out integer); end paquete_procedu; package body paquete_procedu is procedure vector_to_int (signal data_in: in std_logic_vector; data_out: out integer; ms : out std_logic_vector; ls : out std_logic_vector; nu_un : out integer) is variable a_out : integer; variable m : std_logic_vector (ms'length-1 downto 0); variable l : std_logic_vector (ls'length-1 downto 0); variable nu : integer; begin m := std_logic_vector(to_signed(-1,ms'length)); l := std_logic_vector(to_signed(-1,ls'length)); a_out := 0; nu := 0; for i in (data_in'length-1) downto 0 loop a_out := a_out*2; if (data_in(i) = '1') then a_out := a_out+1; nu := nu+1; if (i > to_integer(signed(m))) then m := std_logic_vector(to_signed(i,ms'length)); end if; if (i < to_integer(unsigned(l)) or to_integer(signed(l)) = -1) then l := std_logic_vector(to_signed(i,ls'length)); end if; end if; end loop; ms := m; ls := l; data_out := a_out; nu_un := nu; end vector_to_int; end paquete_procedu; Figura 1 Una descripción VHDL para la entidad principal (top level) se muestra en la figura 2: library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all; use work.paquete_procedu.all; entity procedu is generic (long : integer := 8; log2_long : integer := 3); port ( i : in std_logic_vector(long-1 downto 0); pos_ms1 : out std_logic_vector (log2_long downto 0); pos_ls1 : out std_logic_vector (log2_long downto 0); 2 de 3 Grado en Ingeniería de Tecnologías de Telecomunicación 3er Curso Sistemas Electrónicos Digitales o : out integer; o_apr : out integer; num_unos : out integer); end procedu; architecture behave of procedu is begin process (i) variable ms1 : std_logic_vector (log2_long downto 0); variable ls1 : std_logic_vector (log2_long downto 0); variable o_out : integer; variable o_apr_out : integer; variable num_u : integer; begin vector_to_int(i,o_out,ms1,ls1,num_u); if (num_u > to_integer(signed(ms1))-2 and to_integer(signed(ms1)) < long-1 and to_integer(signed(ms1)) > -1) then o_apr_out := 2**(to_integer(signed(ms1))+1); else o_apr_out := o_out; end if; pos_ms1 <= ms1; pos_ls1 <= ls1; o <= o_out; o_apr <= o_apr_out; num_unos <= num_u; end process; end behave; Figura 2 Mediante Quartus II, sintetizar el circuito. Para la compilación y síntesis, seleccionar el chip FPGA Cyclone II EP2C35F672C6 (Assignments -> Settings: Settings fsm_control -> Device: Family √ Cyclone II: Target Device √ Specific Device selected in ‘Available devices’ list. Show in ‘Available devices’ list √ Fastest. Available devices √ EP2C35F672C6). b) Utilizando Quartus II editar un fichero de Formas de Onda para simulación y verificar el correcto funcionamiento del circuito sintetizado. Parte 2:Diseño del procesador dedicado completo utilizando una descripción VHDL jerárquica en 2 niveles, mediante módulos exclusivamente. a) Realizar una descripción estructural del procesador elemental. El módulo del segundo nivel deberá ser descrito a nivel de algoritmo. Como en la Parte 1, el número y posiciones de los ‘1s’ y valor decimal equivalente deberán ser obtenidos por el módulo del segundo nivel, mientras que la entidad principal deberá obtener el valor aproximado según el criterio establecido. Sintetizar el circuito mediante Quartus II. b) Utilizando el mismo fichero de Formas de Onda para simulación generado en la Parte 1, simular mediante Quartus II el circuito sintetizado y verificar su correcto funcionamiento. Comparar los resultados con los obtenidos para el procesador diseñado en la Parte 1. 3 de 3